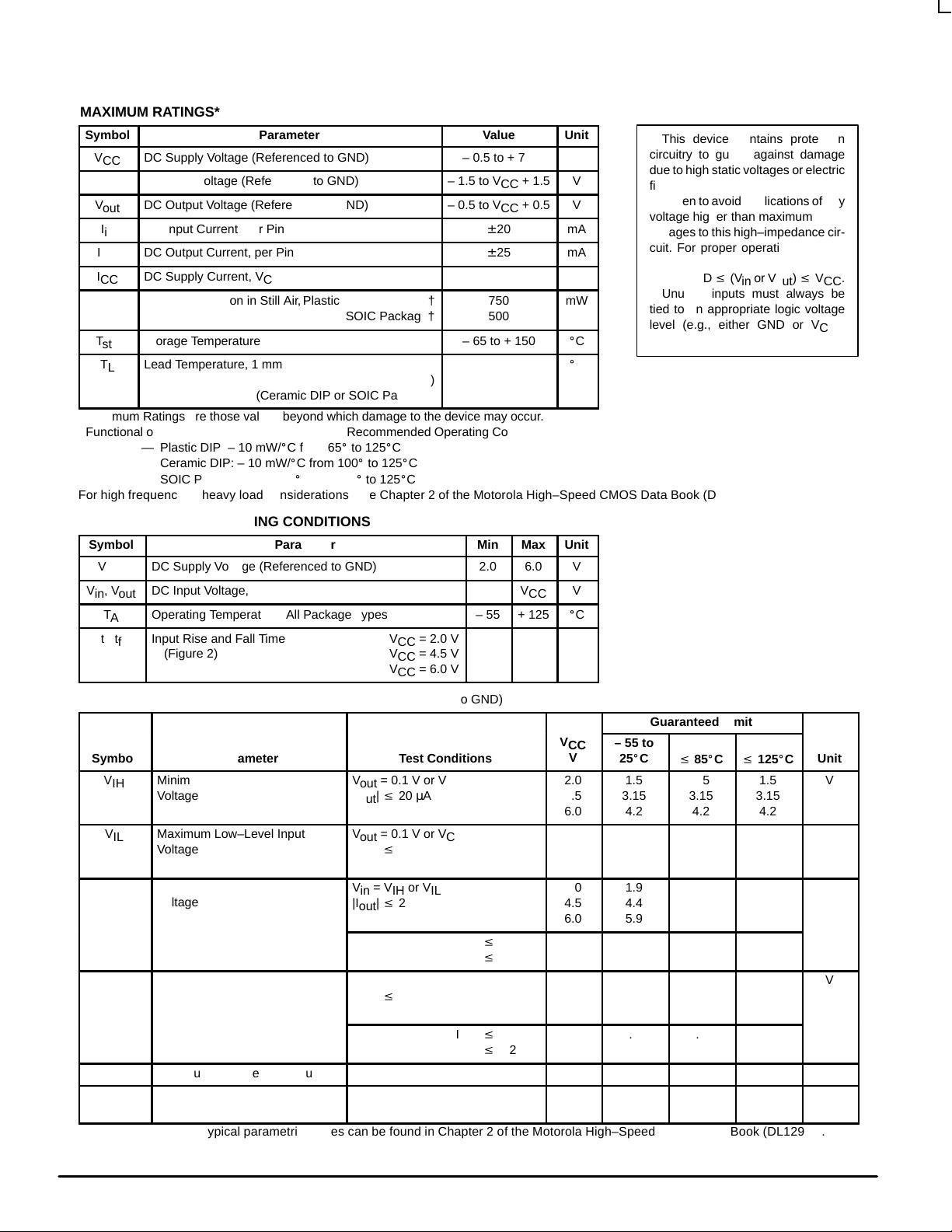

SEMICONDUCTOR TECHNICAL DATA

1

REV 6

Motorola, Inc. 1995

10/95

High–Performance Silicon–Gate CMOS

The MC54/74HC154 is identical in pinout to the LS154. The device inputs

are compatible with standard CMOS outputs; with pullup resistors, they are

compatible with LSTTL outputs.

This device, when enabled, selects one of 16 active–low outputs. Two

active–low Chip Selects are provided to facilitate the chip–select, demulti-

plexing, and cascading functions. When either Chip Select is high, all

outputs are high. The demultiplexing function is accomplished by using the

Address inputs to select the desired device output. Then, while holding one

chip select input low, data can be applied to the other chip select input (see

Application Note).

The HC154 is primarily used for memory address decoding and data

routing applications.

• Output Drive Capability: 10 LSTTL Loads

• Outputs Directly Interface to CMOS, NMOS, and TTL

• Operating Voltage Range: 2 to 6 V

• Low Input Current: 1 µA

• High Noise Immunity Characteristic of CMOS Devices

• In Compliance with the Requirements Defined by JEDEC Standard

No. 7A

• Chip Complexity: 192 FETs or 48 Equivalent Gates

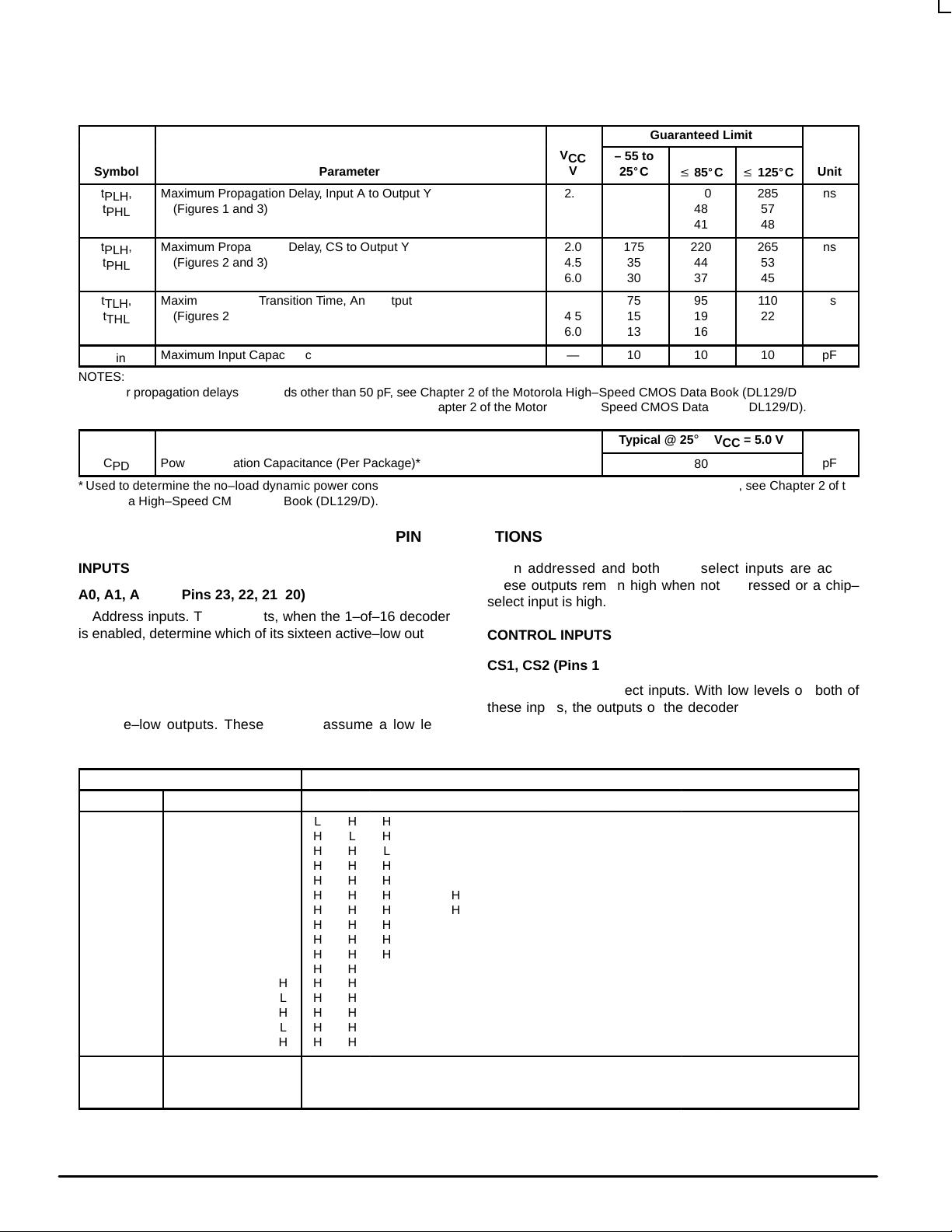

LOGIC DIAGRAM

Y0

Y1

Y2

Y3

Y4

Y5

Y6

Y7

Y8

Y9

Y10

Y11

Y12

Y13

Y14

Y15

A0

A1

A2

A3

CS1

CS2

18

19

23

22

21

20

1

2

3

4

5

6

7

8

9

10

13

14

15

16

17

BINARY

ADDRESS

INPUTS

CHIP

SELECT

INPUTS

ACTIVE–LOW

OUTPUTS

PIN 24 = V

CC

PIN 12 = GND

11

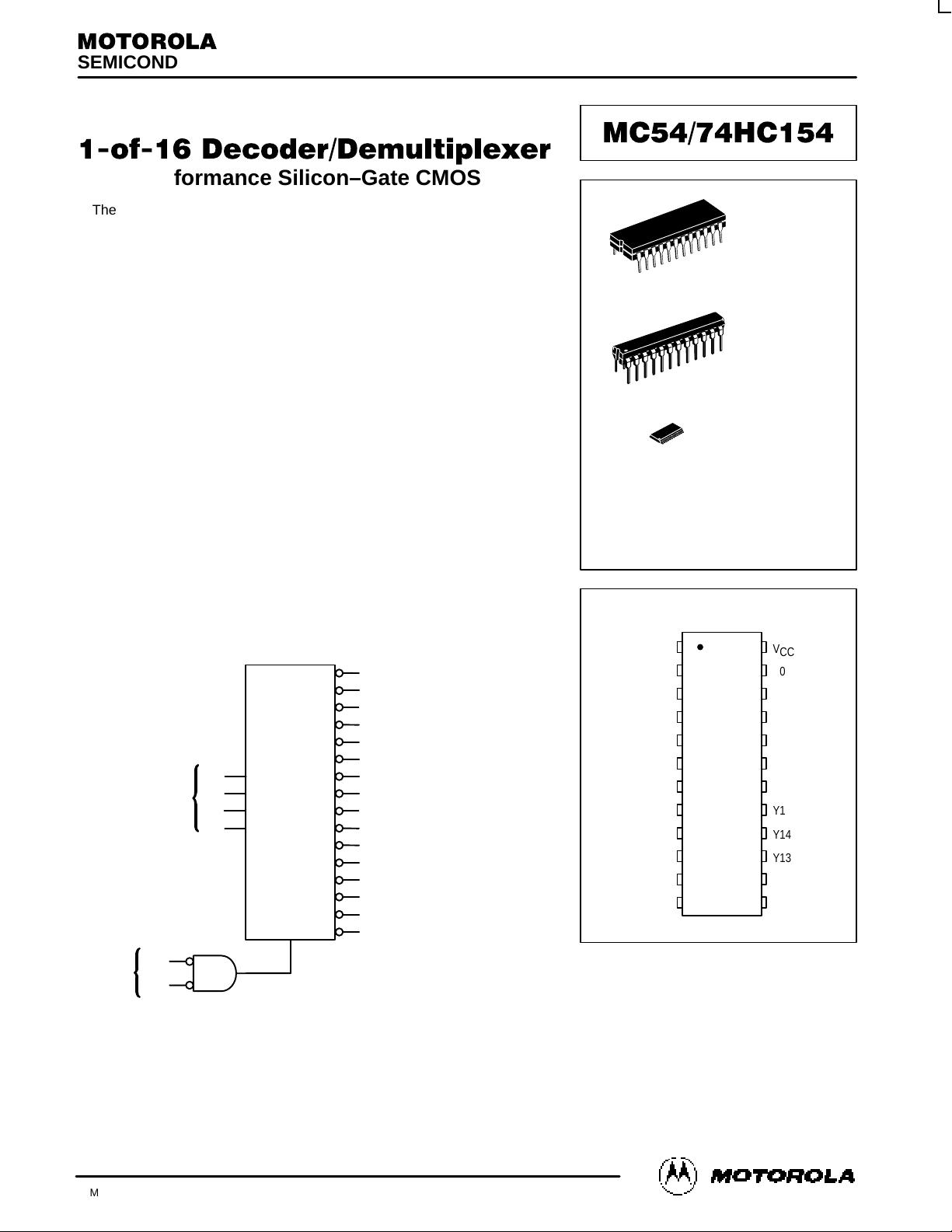

PIN ASSIGNMENT

Y5

Y3

Y2

Y1

Y0

Y7

Y6

Y4 A3

A2

A1

A0

V

CC

Y13

Y14

Y15

Y11

Y12

CS1

CS2

Y10

GND

Y9

Y8

5

4

3

2

1

10

9

8

7

6

14

15

16

17

18

19

20

13

11

12

21

22

23

24

ORDERING INFORMATION

MC54HCXXXJ

MC74HCXXXN

MC74HCXXXDW

Ceramic

Plastic

SOIC

N SUFFIX

PLASTIC PACKAGE

CASE 724–03

J SUFFIX

CERAMIC PACKAGE

CASE 758–02

DW SUFFIX

SOIC PACKAGE

CASE 751E–04

1

24

1

24

1

24