没有合适的资源?快使用搜索试试~ 我知道了~

directory based cache coherency

需积分: 13 1 下载量 168 浏览量

2022-12-23

09:14:22

上传

评论

收藏 249KB PDF 举报

温馨提示

试读

34页

directory based cache coherency,内存一致性

资源推荐

资源详情

资源评论

http://www.csg.csail.mit.edu/6.823

Joel Emer

Computer Science and Artificial Intelligence Lab

M.I.T.

Directory-Based Cache Coherence

1

Sanchez & Emer

http://www.csg.csail.mit.edu/6.823

Maintaining Cache Coherence

It is sufficient to have hardware such that

• only one processor at a time has write permission

for a location

• no processor can load a stale copy of the location

after a write

Þ Α correct approach could be:

write request:

The address is invalidated in all other caches before

the write is performed

read request:

If a dirty copy is found in some cache, a write-back

is performed before the memory is read

April 4, 2016

L16-2

Sanchez & Emer

http://www.csg.csail.mit.edu/6.823

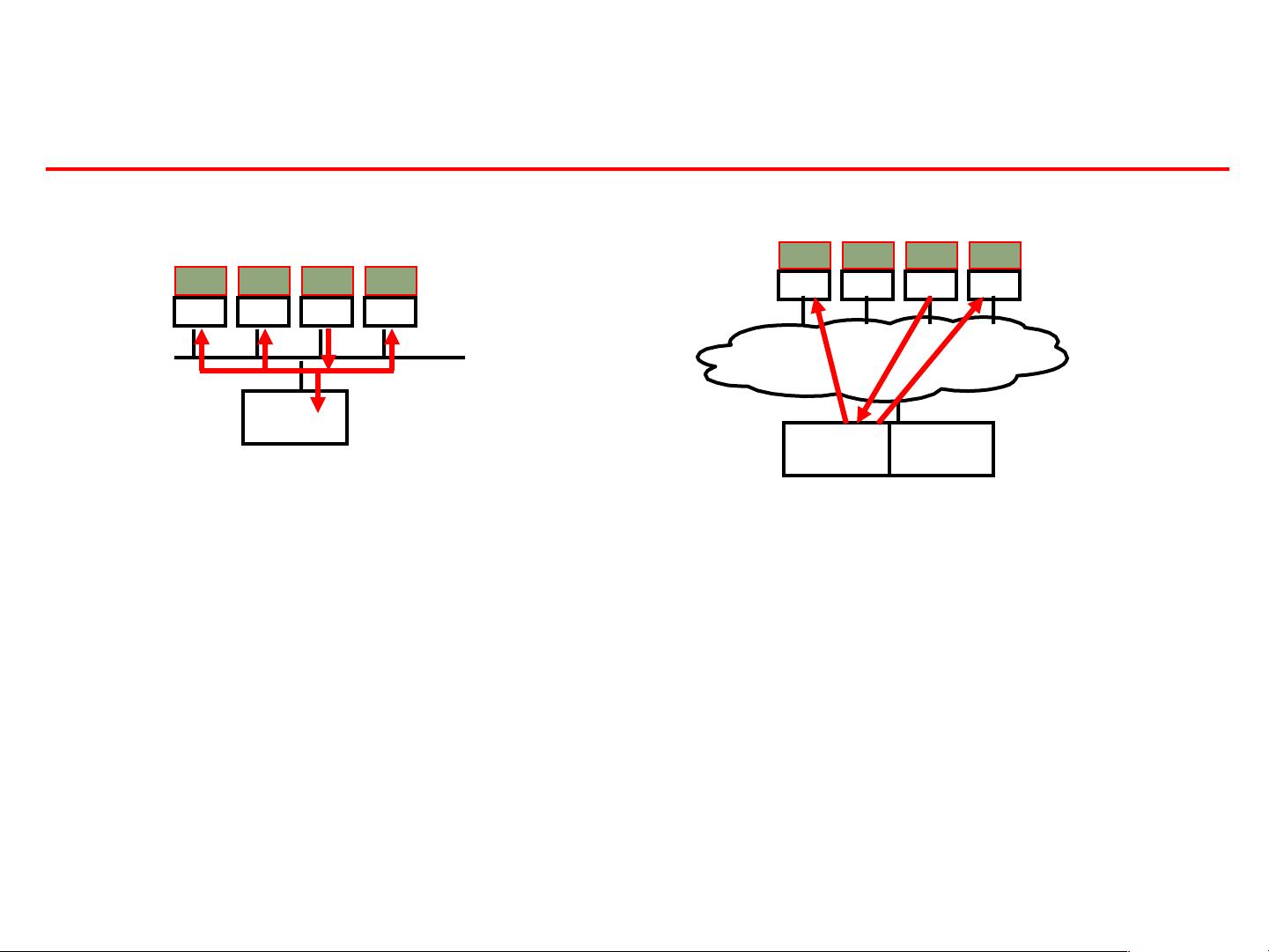

Directory-Based Coherence

(Censier and Feautrier, 1978)

• Snoopy schemes broadcast

requests over memory bus

• Difficult to scale to large

numbers of processors

• Requires additional

bandwidth to cache tags for

snoop requests

• Directory schemes send

messages to only those caches

that might have the line

• Can scale to large numbers of

processors

• Requires extra directory

storage to track possible

sharers

$

P

$

P

$

P

$

P

Bus

Mem.

Snoopy Protocols

$

P

$

P

$

P

$

P

Dir.

Interconnect

Network

Mem.

Directory Protocols

April 4, 2016

L16-3

Sanchez & Emer

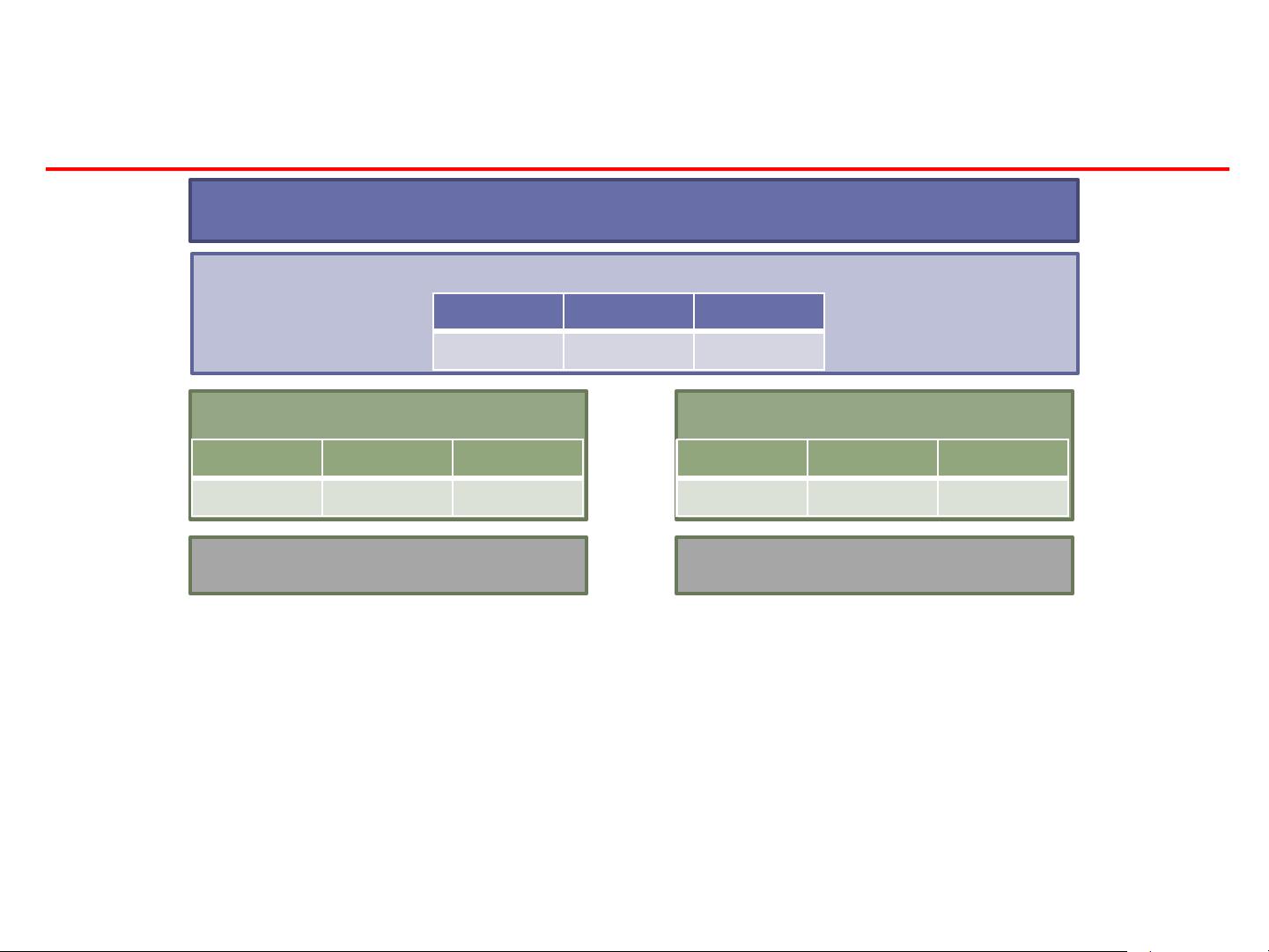

An MSI Directory Protocol

• Cache states: Modified (M) / Shared (S) / Invalid (I)

• Directory states:

– Uncached (Un): No sharers

– Shared (Sh): One or more sharers with read permission (S)

– Exclusive (Ex): A single sharer with read & write permissions (M)

• Transient states not drawn for clarity; for now,

assume no racing requests

http://www.csg.csail.mit.edu/6.823

Core 0

Main Memory

Cache 0

Core N

Cache N

Tag State Data

Tag State DataTag State Data

Directory

Tag State Sharers

…

April 4, 2016

L16-4

Sanchez & Emer

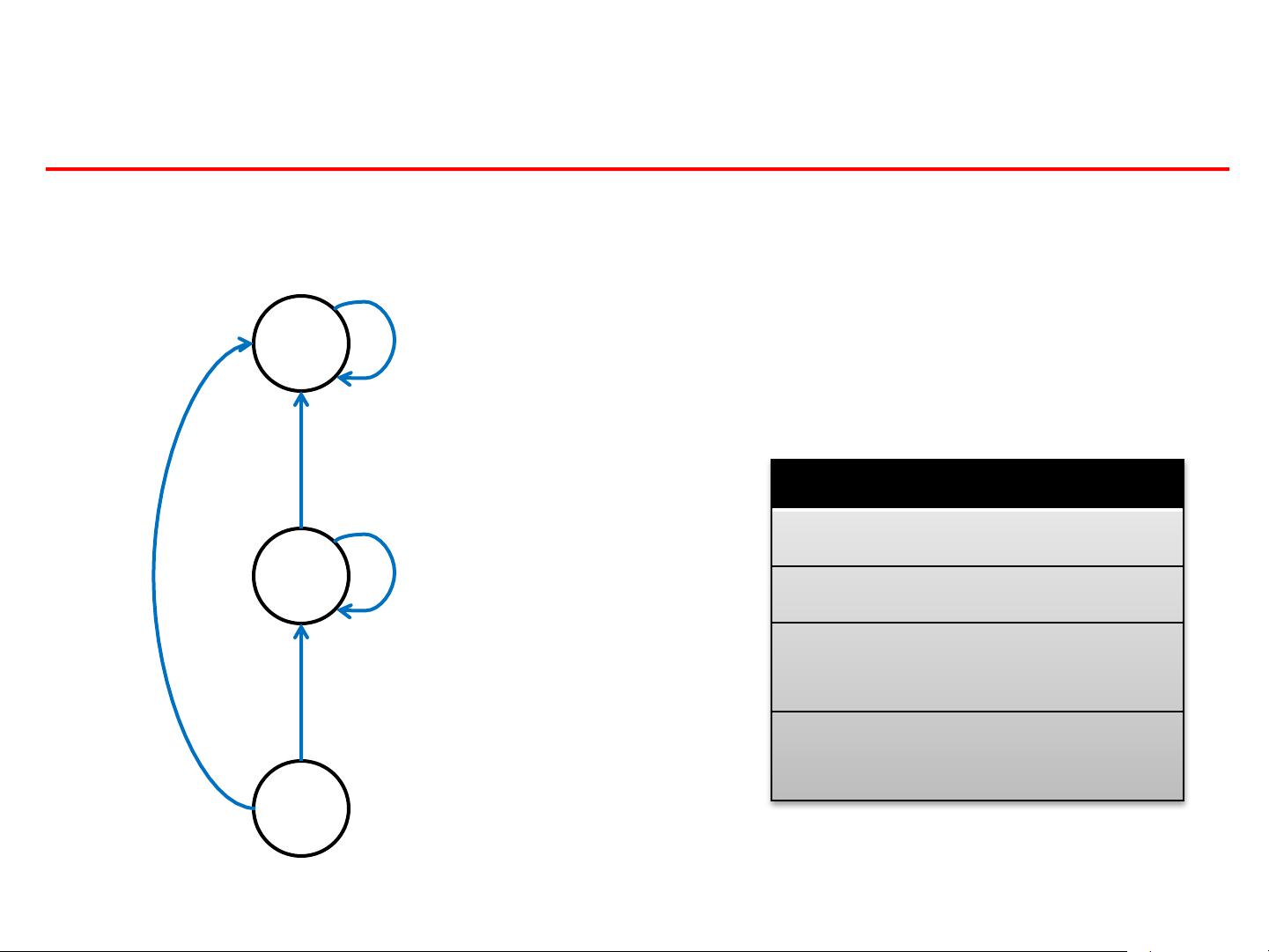

MSI Protocol: Caches (1/3)

http://www.csg.csail.mit.edu/6.823

M

S

I

PrWr / ExReq

Transitions initiated by processor accesses:

PrRd / ShReq

PrWr /

ExReq

PrRd / --

PrRd / --

PrWr / --

Actions

Processor Read (PrRd)

Processor Write (PrWr)

Shared Request

(ShReq)

Exclusive Request

(ExReq)

April 4, 2016

L16-5

剩余33页未读,继续阅读

资源评论

u010634378

- 粉丝: 0

- 资源: 8

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功