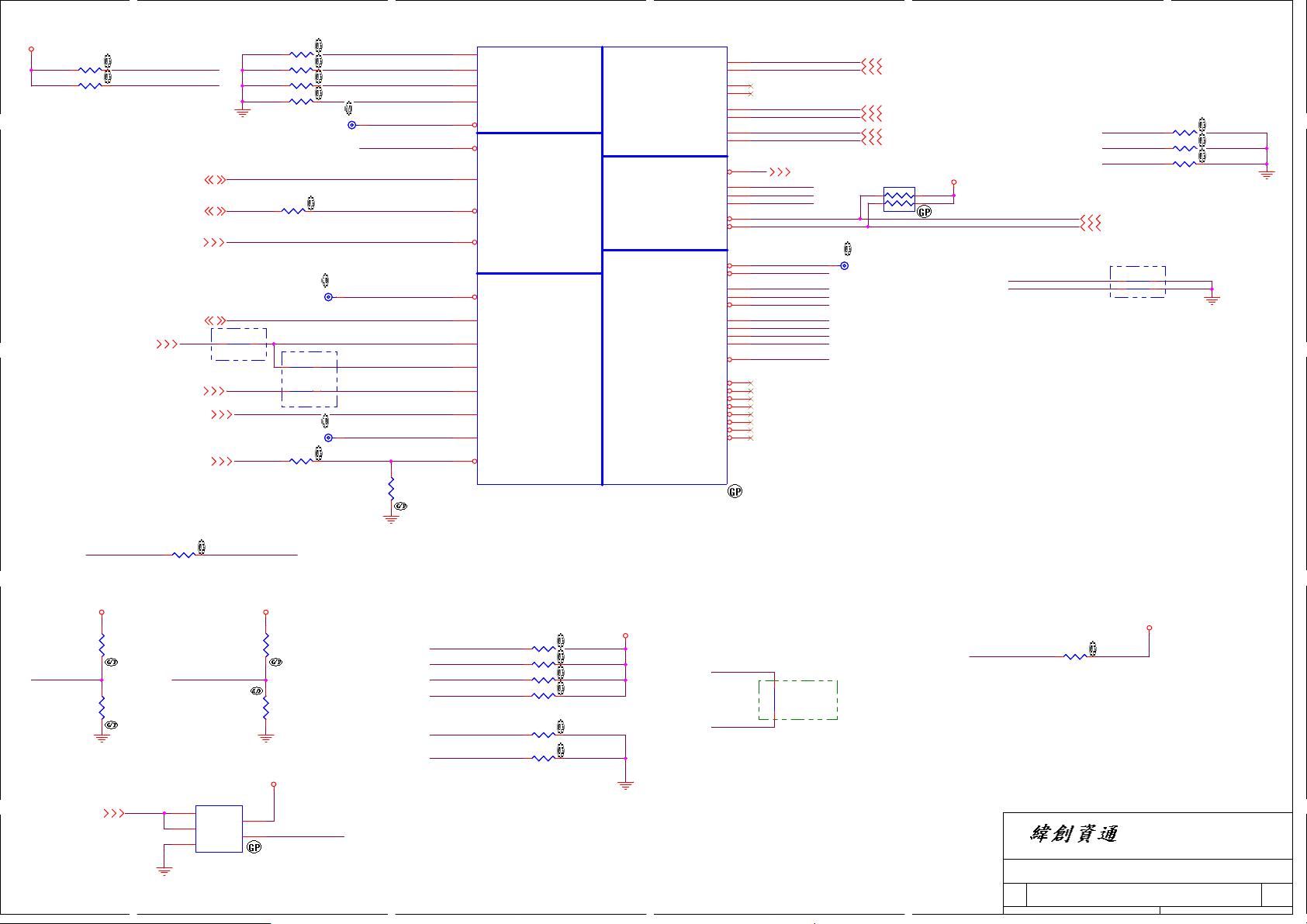

宏基4741G图纸

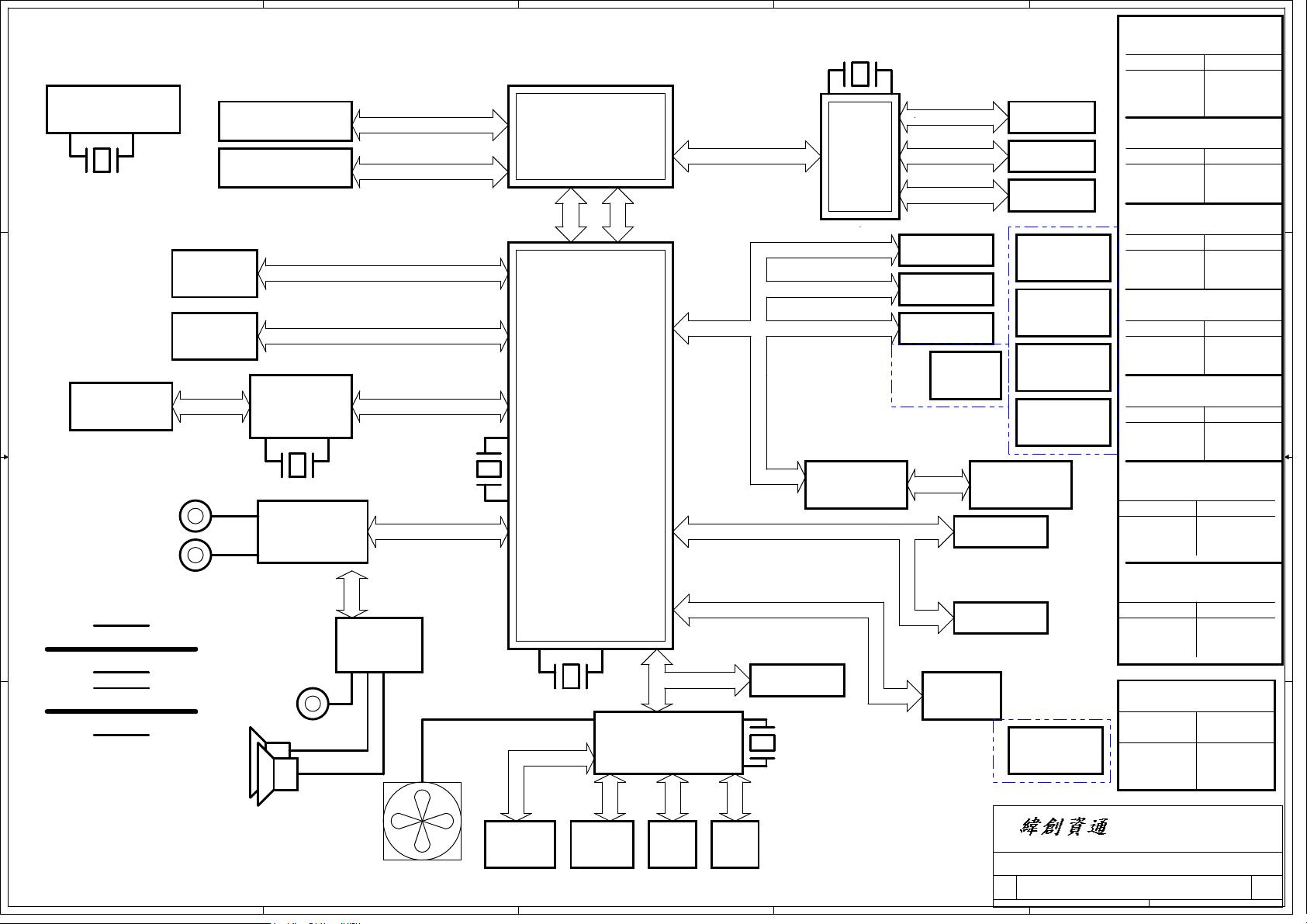

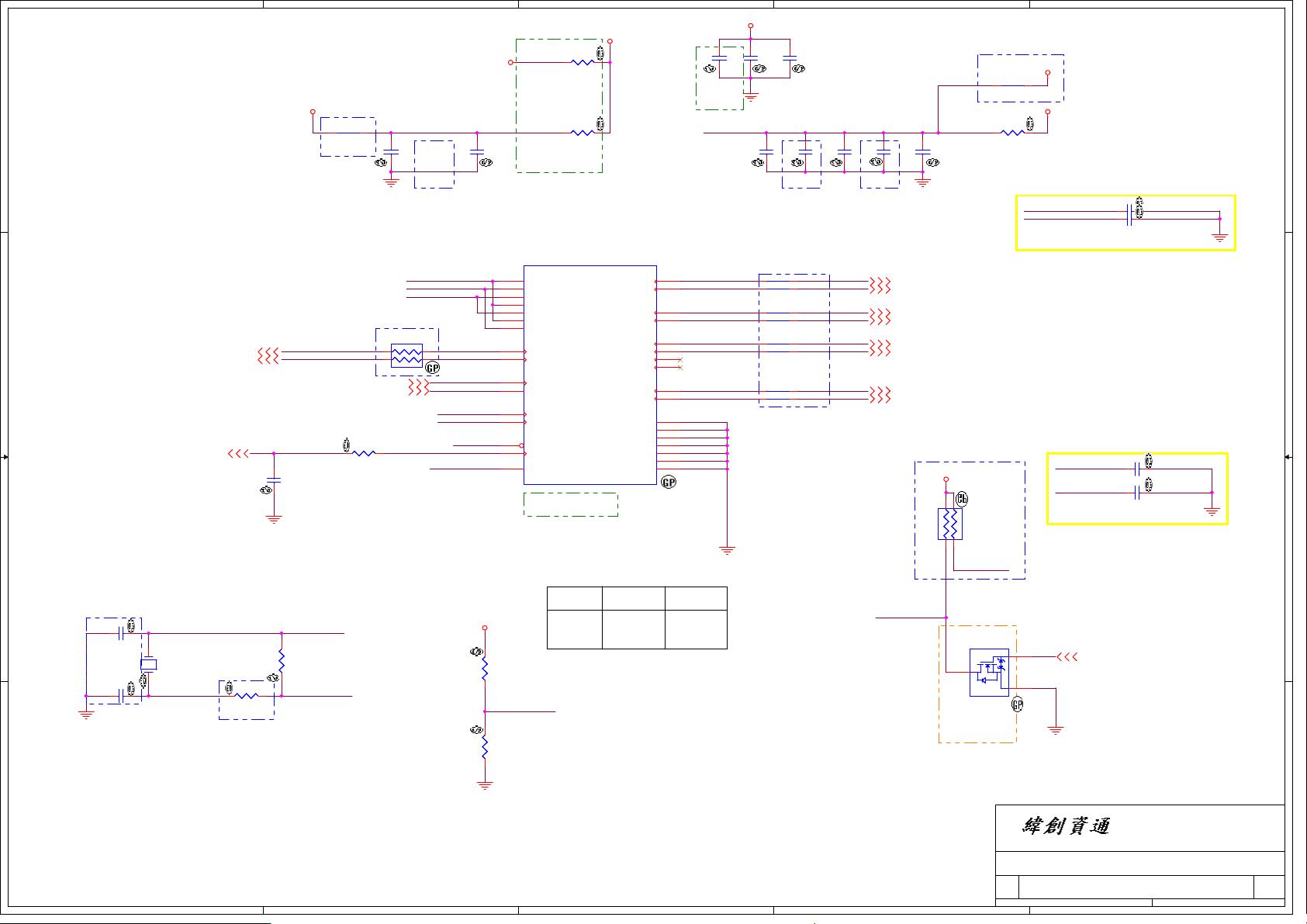

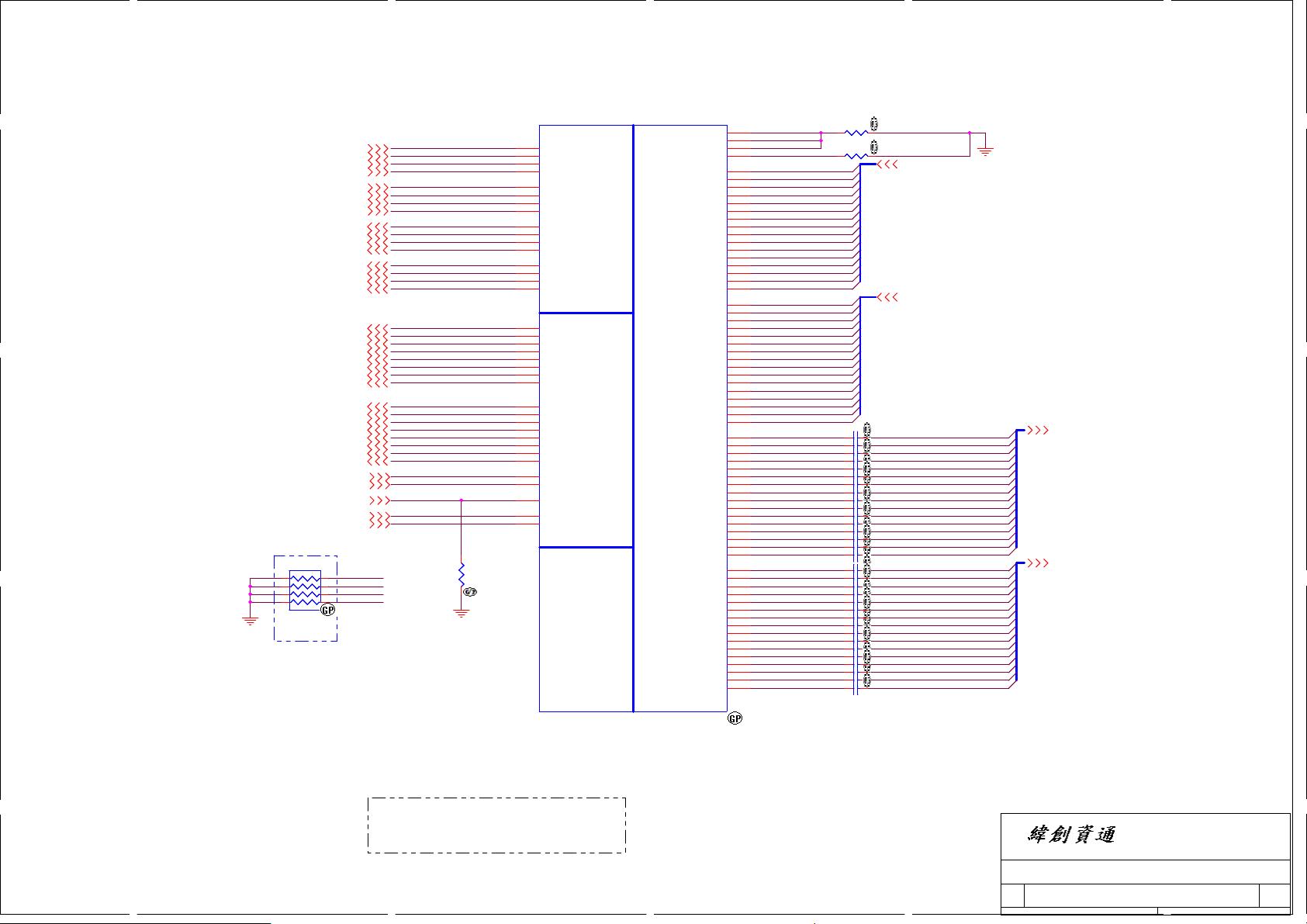

从给定的宏基4741G图纸信息来看,我们深入探讨的将是一台笔记本电脑内部硬件架构的详尽细节。宏基4741G是一款颇受欢迎的笔记本型号,其内部设计不仅反映了宏基在笔记本制造领域的技术实力,也展示了当时硬件配置的先进水平。下面,我们将对这份图纸中的关键组件及其功能进行详细解析。 ### CPU与内存 - **Intel CPU**: 宏基4741G采用的是Intel处理器,具体型号为Arrandale系列,支持DDR3 800/1066 MHz内存规格。这意味着它能够处理复杂的计算任务,并且拥有较快的数据传输速度。 - **DDR3 Memory**: 笔记本配备了DDR3内存,这是一种高性能、低功耗的内存类型,能显著提升系统响应速度和多任务处理能力。图纸中提到的“DDRIII 800/1066”指的是支持的内存频率范围。 ### 显卡与图形处理 - **Nvidia GPU**: 笔记本搭载了Nvidia显卡,具体型号为AU6433,支持PCI Express图形接口。这表明宏基4741G具有一定的图形处理能力,适合运行图形密集型应用或游戏。 - **VGA/LVDS**: 提供了VGA和LVDS输出选项,用于连接外部显示器或投影仪,满足不同场景下的显示需求。 ### 存储与外设 - **SATA HDD/Optical Drive**: 配备了SATA硬盘驱动器和光驱,提供足够的存储空间和数据读写功能。 - **Card Reader**: 支持SD/MMC、MS/MS Pro/xD等多种存储卡格式,便于用户快速传输数据。 ### 连接性与通信 - **Bluetooth**: 内置蓝牙模块,确保设备之间的无线通信,方便连接无线耳机、鼠标等外设。 - **Ethernet/GigaLAN**: 通过BCM57780芯片支持有线网络连接,实现高速稳定的互联网接入。 - **USB Ports**: 提供了多个USB 2.0端口,兼容USB 1.1标准,增强数据传输和外设扩展能力。 ### 电源管理 - **DCBATOUT**: 表示电源输入输出接口,负责电池和适配器的充电及供电管理。 - **System DC/DC**: 包括多个电压转换电路,如RT8209E、RT8223等,用于调节不同硬件所需的电源电压。 ### 声音与输入设备 - **High Definition Audio**: 集成了高清音频解决方案,确保高质量的声音输出。 - **Line Out/Speakers**: 提供线路输出和扬声器接口,方便用户连接音响系统或耳机。 - **Touch Pad**: 配置了触摸板作为主要的输入设备,支持多种手势操作,提高用户体验。 ### 其他特性 - **Thermal Sensor**: 内置温度传感器,监控系统温度,防止过热。 - **3G Module**: 提供了3G通信模块,意味着宏基4741G具备移动宽带上网的能力,增强了其便携性和网络连接灵活性。 通过以上分析,我们可以看出宏基4741G不仅在硬件配置上考虑到了性能与实用性,还在连接性、多媒体支持以及电源管理等方面做了周全的设计,体现了宏基在笔记本电脑领域的深厚技术积累和市场洞察力。这份图纸不仅是工程师们的工作蓝图,也是理解宏基4741G内部构造和技术特点的宝贵资料。

剩余67页未读,继续阅读

tmdhx2014-07-08赞一个,找了好久好久!不错!

tmdhx2014-07-08赞一个,找了好久好久!不错! llrlove2014-03-29非常好 我喜欢

llrlove2014-03-29非常好 我喜欢

- 粉丝: 0

- 资源: 1

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 每周质量安全排查报告.docx

- 排水报装接入申请表.docx

- 评估报告公示公众意见表.doc

- 评审、登记备案情况表.docx

- 墙板隐蔽前监理检查记录.docx

- 抢救室、输液室周带教计划表.docx

- 人防工程主体结构验收前监理人员检查记录表.docx

- 人防工程竣工验收前监理人员检查记录.docx

- 人防门框及临战封堵框常规数据检查表.docx

- 人防门扇常规数据检查表.docx

- 社区工作者岗位表.docx

- 涉及消防的建筑材料、构配件和设备的进场试验报告汇总表.docx

- 涉及消防的各分部分项工程消防查验结果表.docx

- 十级伤残鉴定标准表.docx

- 市标化优良工地检查自评表(施工、监理企业用表).docx

- 输液结束(拔针)流程表.docx

信息提交成功

信息提交成功