S12XS

Microcontrollers

freescale.com

MC9S12XS256

Reference Manual

Covers MC9S12XS-Family

MC9S12XS256

MC9S12XS128

MC9S12XS64

MC9S12XS256RMV1

Rev. 1.03

06/2008

To provide the most up-to-date information, the document revision on the World Wide Web is the most

current. A printed copy may be an earlier revision. To verify you have the latest information available, refer

to: http://freescale.com/

This document contains information for the complete S12XS-Family and thus includes a set of separate

flash (FTMR) module sections to cover the whole family. A full list of family members and options is

included in the appendices.

This document contains information for all constituent modules, with the exception of the CPU. For CPU

information please refer to CPU12XV1 in the CPU12/CPU12X Reference Manual.

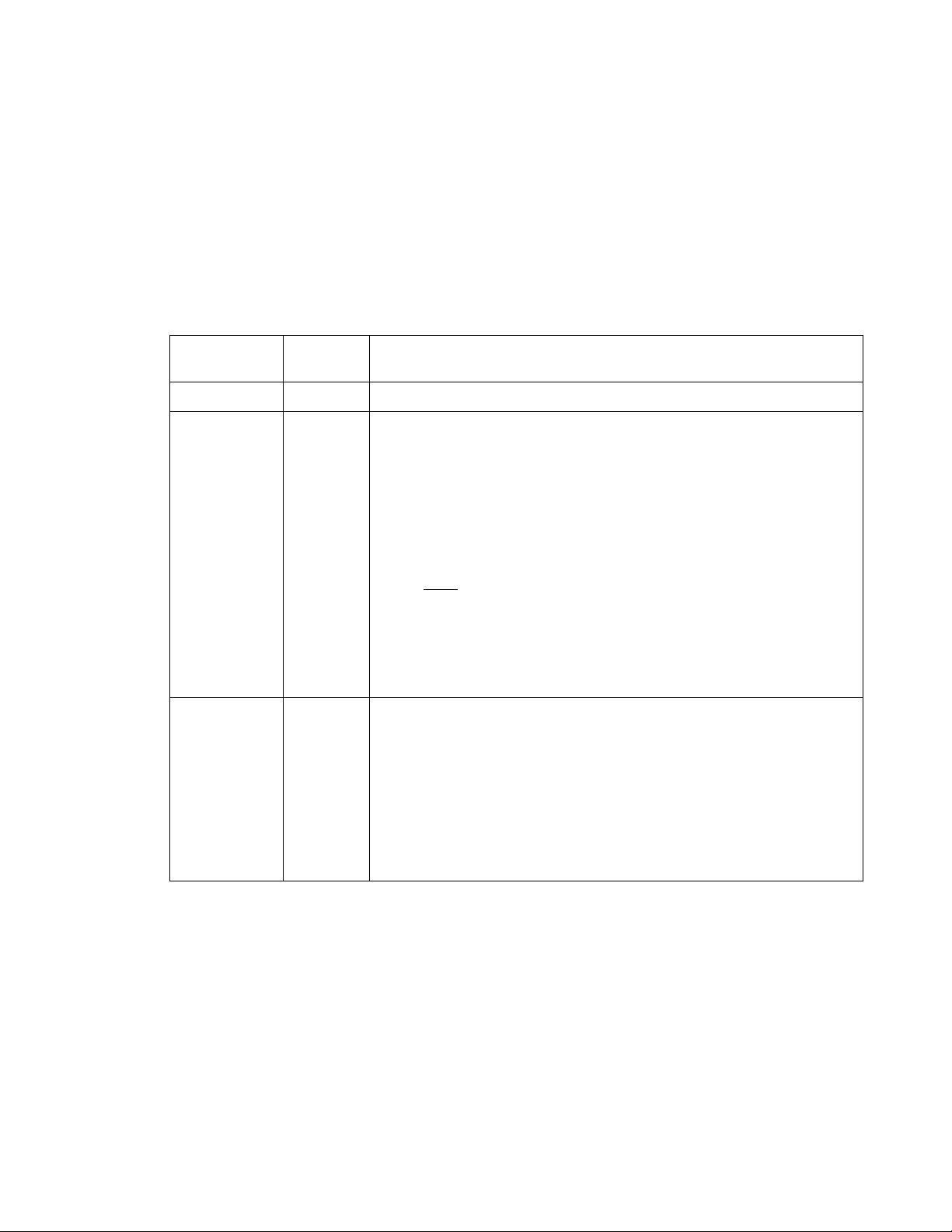

Revision History

Date

Revision

Level

Description

May, 2007 1.00 Initial version - PRELIMINARY

August, 2007 1.01

Corrected CPU documentation reference in above paragraph

Updated chp. ‘256 KByte Flash Module’ - see ‘FTMR256K1 Revision History’

Updated chp. ‘128 KByte Flash Module’ - see ‘FTMR128K1 Revision History’

Updated chp. ‘Port Integration Module’ - see ‘Revision History’

Unburied tag of chp. 16 ‘Timer Module (TIM16B8CV2)’

Removed subject-to-change note on pinouts in figs. 1-3 to 1-5

Changed ‘drive’ to ‘output’ of ECLK on PE4 in 1.2.3.10 for clarity

Added 1M04M mask revision to table 1-3

Corrected description of ESD diode connections in A.1.2

Updated Thermal Package Characteristics in table A-5

Added

XIRQ pulse width to table A-6 and A-7

Made 64-pin package drawing visible in fig. B-3

Corrected PWM channel numbers in table D-2

Several corrections in E.1 ‘Detailed Register Map’

Minor cosmetic corrections

Added document order number to cover, changed title, updated backcover

February, 2008 1.02

Updated CPU version in above paragraph according to new CPU manual

Corrected number of SPI and SCI modules in Features

Corrected SPI pins on routed Port M locations in Detailed Signal Descriptions

Reset Sources and Interrupt Vector Locations tables updated

Updated FTMR, XMMC, PIM, TIM, VREG, XDBG and XINT sections

Added Temperature Sensor Configuration section

Updated several tables in Appendix A

Added NVM timing characteristics

Updated VREG electrical characteristics

Updated mechanical package drawings

S12XS-Family Reference Manual, Rev. 1.03

Freescale Semiconductor PRELIMINARY 3

June, 2008 1.03

Corrected SPI0 pins in family block diagram and Detailed Signal Descriptions

Corrected descriptions of pins PM2,3,5 in Pin-out Summary table

Added general application note at beginning of Detailed Signal Descriptions

Updated ADC, PIM, XDBG, and CRG sections

Added FTM64K1 section

Added/updated max. Idd limits in Appx. A

Added ATD min./max. values to electrical characteristics in Appx. A

Added ATD min./max. values to conversion performance in Appx. A

Added jitter fit parameter in Appx. A

Updated several parameter classifications in Appx. A

Updated several VREG electricals in Appx. A

Corrected bit names in Appx. E

Revision History (continued)

Date

Revision

Level

Description

S12XS-Family Reference Manual, Rev. 1.03

4 PRELIMINARY Freescale Semiconductor

S12XS-Family Reference Manual, Rev. 1.03

Freescale Semiconductor PRELIMINARY 1

Chapter 1 Device Overview S12XS-Family . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

Chapter 2 Port Integration Module (S12XSPIMV1) . . . . . . . . . . . . . . . . . . . . . . . . . . .55

Chapter 3 Memory Mapping Control (S12XMMCV4) . . . . . . . . . . . . . . . . . . . . . . . .121

Chapter 4 Interrupt (S12XINTV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .145

Chapter 5 Background Debug Module (S12XBDMV2) . . . . . . . . . . . . . . . . . . . . . . .161

Chapter 6 S12X Debug (S12XDBGV3) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . .187

Chapter 7 Security (S12XS9SECV2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .223

Chapter 8 S12XE Clocks and Reset Generator (S12XECRGV1) . . . . . . . . . . . . . . .229

Chapter 9 Pierce Oscillator (S12XOSCLCPV2) . . . . . . . . . . . . . . . . . . . . . . . . . . . .263

Chapter 10 Analog-to-Digital Converter (ADC12B16CV1) . . . . . . . . . . . . . . . . . . . . .267

Chapter 11 Freescale’s Scalable Controller Area Network (S12MSCANV3) . . . . . .293

Chapter 12 Periodic Interrupt Timer (S12PIT24B4CV1) . . . . . . . . . . . . . . . . . . . . . . .349

Chapter 13 Pulse-Width Modulator (S12PWM8B8CV1) . . . . . . . . . . . . . . . . . . . . . . .365

Chapter 14 Serial Communication Interface (S12SCIV5) . . . . . . . . . . . . . . . . . . . . . .397

Chapter 15 Serial Peripheral Interface (S12SPIV5). . . . . . . . . . . . . . . . . . . . . . . . . . .435

Chapter 16 Timer Module (TIM16B8CV2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .461

Chapter 17 Voltage Regulator (S12VREGL3V3V1) . . . . . . . . . . . . . . . . . . . . . . . . . . .489

Chapter 18 256 KByte Flash Module (S12XFTMR256K1V1). . . . . . . . . . . . . . . . . . . .507

Chapter 19 128 KByte Flash Module (S12XFTMR128K1V1). . . . . . . . . . . . . . . . . . . .565

Chapter 20 64 KByte Flash Module (S12XFTMR64K1V1). . . . . . . . . . . . . . . . . . . . . .623

Appendix A Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .679

Appendix B Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .719

Appendix C PCB Layout Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .729

Appendix D Derivative Differences . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .733

Appendix E Detailed Register Address Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .734

Appendix F Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .756