没有合适的资源?快使用搜索试试~ 我知道了~

Sumsuang DDR_K4B4G1646E_

需积分: 5 0 下载量 94 浏览量

2022-09-21

15:50:21

上传

评论

收藏 1.09MB PDF 举报

温馨提示

试读

71页

K4B4G1646E_datasheet

资源推荐

资源详情

资源评论

- 1 -

K4B4G1646E

Rev. 1.1, Jun. 2016

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND

SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed

herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung

Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property

right is granted by one party to the other party under this document, by implication, estoppel or other-

wise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or

similar applications where product failure could result in loss of life or personal or physical harm, or any

military or defense application, or any governmental procurement to which special terms or provisions

may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

ⓒ 2016 Samsung Electronics Co., Ltd. All rights reserved.

4Gb E-die DDR3L SDRAM Only x16

96FBGA with Lead-Free & Halogen-Free

(RoHS compliant)

datasheet

1.35V

Manufacturer: SAMSUNG

Manufacturer PN: K4B4G1646E-BYMA

HF,MSL3

*Pin defined: Page.6

*Dimension: Page.7

Symbol same as 072.44164.0D0U

“DDR3L-1866” products are compatible with “DDR3-1866” and “DDR3/DDR3L-1600” products.

- 2 -

datasheetK4B4G1646E DDR3L SDRAM

Rev. 1.1

Revision History

Revision No. History Draft Date Remark Editor

1.0 - First SPEC Release Dec. 2014 - J.Y.Lee

1.1 - Addition of information about I-temp 23th Jun. 2016 - J.Y.Lee

- 3 -

datasheetK4B4G1646E DDR3L SDRAM

Rev. 1.1

Table Of Contents

4Gb E-die DDR3L SDRAM Olny x16

1. Ordering Information .....................................................................................................................................................5

2. Key Features................................................................................................................................................................. 5

3. Package pinout/Mechanical Dimension & Addressing..................................................................................................6

3.1 x16 Package Pinout (Top view) : 96ball FBGA Package ........................................................................................ 6

3.2 FBGA Package Dimension (x16)............................................................................................................................. 7

4. Input/Output Functional Description..............................................................................................................................8

5. DDR3 SDRAM Addressing ........................................................................................................................................... 9

6. Absolute Maximum Ratings ..........................................................................................................................................10

6.1 Absolute Maximum DC Ratings............................................................................................................................... 10

6.2 DRAM Component Operating Temperature Range ................................................................................................ 10

7. AC & DC Operating Conditions.....................................................................................................................................10

7.1 Recommended DC operating Conditions ................................................................................................................ 10

8. AC & DC Input Measurement Levels ............................................................................................................................11

8.1 AC & DC Logic input levels for single-ended signals .............................................................................................. 11

8.2 VREF Tolerances .................................................................................................................................................... 13

8.3 AC & DC Logic Input Levels for Differential Signals................................................................................................ 14

8.3.1. Differential signals definition ............................................................................................................................ 14

8.3.2. Differential swing requirement for clock (CK - CK

) and strobe (DQS - DQS) .................................................. 14

8.3.3. Single-ended requirements for differential signals ........................................................................................... 15

8.4 Differential Input Cross Point Voltage...................................................................................................................... 17

8.5 Slew rate definition for Differential Input Signals ..................................................................................................... 17

8.6 Slew rate definitions for Differential Input Signals ................................................................................................... 18

9. AC & DC Output Measurement Levels .........................................................................................................................18

9.1 Single-ended AC & DC Output Levels..................................................................................................................... 18

9.2 Differential AC & DC Output Levels......................................................................................................................... 18

9.3 Single-ended Output Slew Rate .............................................................................................................................. 19

9.4 Differential Output Slew Rate .................................................................................................................................. 20

9.5 Reference Load for AC Timing and Output Slew Rate ............................................................................................ 20

9.6 Overshoot/Undershoot Specification ....................................................................................................................... 21

9.6.1. Address and Control Overshoot and Undershoot specifications...................................................................... 21

9.6.2. Clock, Data, Strobe and Mask Overshoot and Undershoot Specifications ...................................................... 22

9.7 34ohm Output Driver DC Electrical Characteristics................................................................................................. 23

9.7.1. Output Drive Temperature and Voltage Sensitivity .......................................................................................... 25

9.8 On-Die Termination (ODT) Levels and I-V Characteristics ..................................................................................... 25

9.8.1. ODT DC Electrical Characteristics ................................................................................................................... 26

9.8.2. ODT Temperature and Voltage sensitivity ....................................................................................................... 28

9.9 ODT Timing Definitions ........................................................................................................................................... 29

9.9.1. Test Load for ODT Timings.............................................................................................................................. 29

9.9.2. ODT Timing Definitions .................................................................................................................................... 29

10. IDD Current Measure Method.....................................................................................................................................32

10.1 IDD Measurement Conditions ............................................................................................................................... 32

11. 4Gb DDR3L SDRAM E-die IDD Specification Table ..................................................................................................41

12. Input/Output Capacitance ........................................................................................................................................... 42

13. Electrical Characteristics and AC timing for DDR3-800 to DDR3-1866 ...................................................................... 43

13.1 Clock Specification ................................................................................................................................................ 43

13.1.1. Definition for tCK(avg).................................................................................................................................... 43

13.1.2. Definition for tCK(abs).................................................................................................................................... 43

13.1.3. Definition for tCH(avg) and tCL(avg).............................................................................................................. 43

13.1.4. Definition for note for tJIT(per), tJIT(per, Ick) ................................................................................................. 43

13.1.5. Definition for tJIT(cc), tJIT(cc, Ick) ................................................................................................................. 43

13.1.6. Definition for tERR(nper)................................................................................................................................ 43

13.2 Refresh Parameters by Device Density................................................................................................................. 44

13.3 Speed Bins and CL, tRCD, tRP, tRC and tRAS for corresponding Bin ................................................................. 44

- 4 -

datasheetK4B4G1646E DDR3L SDRAM

Rev. 1.1

13.3.1. Speed Bin Table Notes .................................................................................................................................. 48

14. Timing Parameters by Speed Grade ..........................................................................................................................49

14.1 Jitter Notes ............................................................................................................................................................ 53

14.2 Timing Parameter Notes........................................................................................................................................ 54

14.3 Address/Command Setup, Hold and Derating : .................................................................................................... 55

14.4 Data Setup, Hold and Slew Rate Derating : .......................................................................................................... 64

- 5 -

datasheetK4B4G1646E DDR3L SDRAM

Rev. 1.1

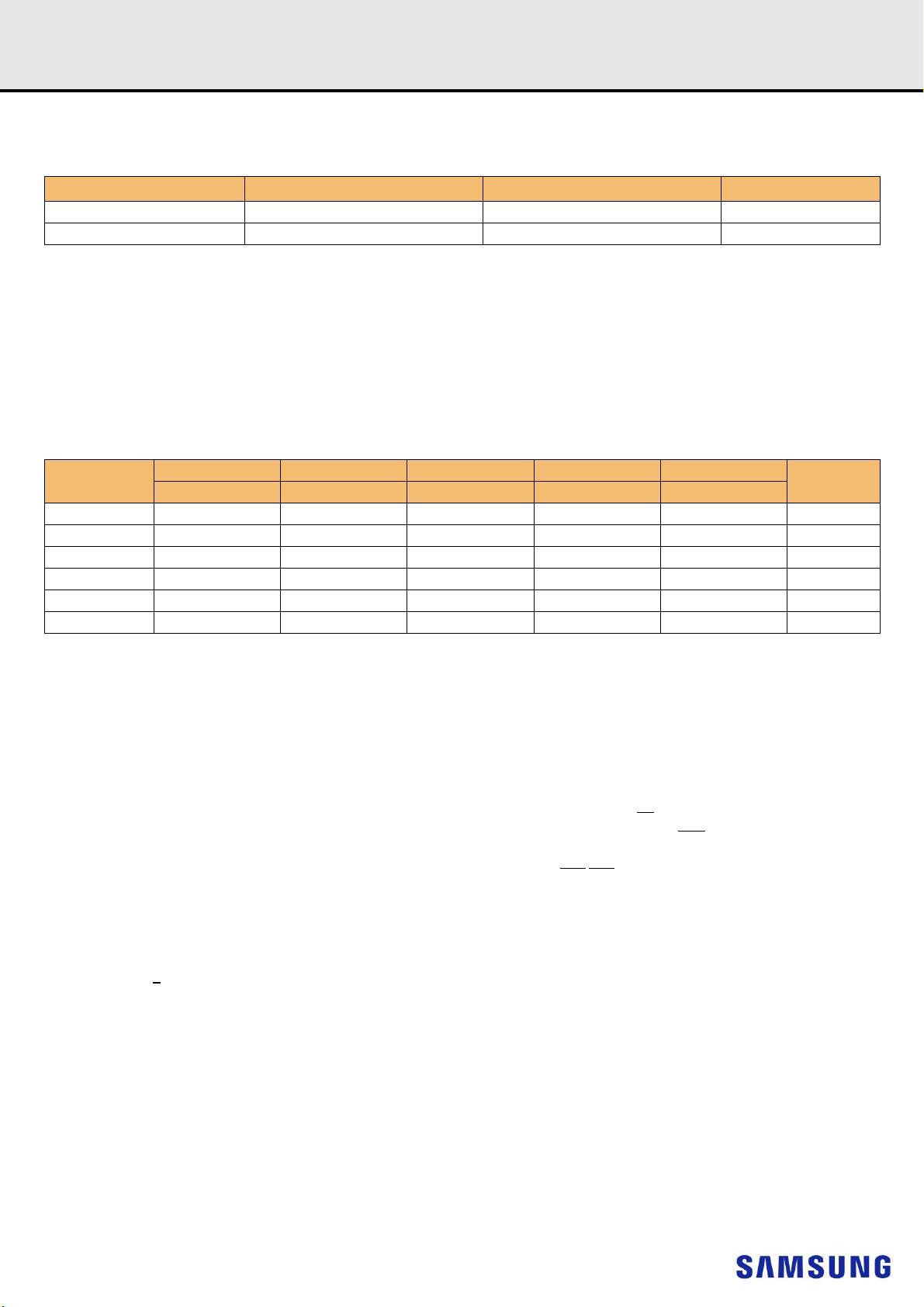

1. Ordering Information

[ Table 1 ] Samsung 4Gb DDR3L E-die ordering information table

NOTE :

1. Speed bin is in order of CL-tRCD-tRP.

2. 13th digit stands for below.

"Y" : Commercial temp/Normal power

"M" : Industrial temp/Normal power

3. Backward compatible to DDR3L-1600(11-11-11), DDR3L-1333(9-9-9)

2. Key Features

[ Table 2 ] 4Gb DDR3 E-die Speed bins

Organization

DDR3L-1600 (11-11-11) DDR3L-1866 (13-13-13)

3

Package

256Mx16 K4B4G1646E-BYK0 K4B4G1646E-BYMA 96 FBGA

256Mx16 K4B4G1646E-BMK0 K4B4G1646E-BMMA 96 FBGA

Speed

DDR3-800 DDR3-1066 DDR3-1333 DDR3-1600 DDR3-1866

Unit

6-6-6 7-7-7 9-9-9 11-11-11 13-13-13

tCK(min) 2.5 1.875 1.5 1.25 1.071 ns

CAS Latency 6 7 9 11 13 nCK

tRCD(min) 15 13.125 13.5 13.75 13.91 ns

tRP(min) 15 13.125 13.5 13.75 13.91 ns

tRAS(min) 37.5 37.5 36 35 34 ns

tRC(min) 52.5 50.625 49.5 48.75 47.91 ns

• JEDEC standard 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V)

•V

DDQ

= 1.35V(1.28V~1.45V) & 1.5V(1.425V~1.575V)

• 400 MHz f

CK

for 800Mb/sec/pin, 533MHz f

CK

for 1066Mb/sec/pin,

667MHz f

CK

for 1333Mb/sec/pin, 800MHz f

CK

for 1600Mb/sec/pin

933MHz f

CK

for 1866Mb/sec/pin

• 8 Banks

• Programmable CAS Latency(posted CAS): 5,6,7,8,9,10,11,12,13

• Programmable Additive Latency: 0, CL-2 or CL-1 clock

• Programmable CAS Write Latency (CWL) = 5 (DDR3-800), 6

(DDR3-1066), 7 (DDR3-1333), 8 (DDR3-1600) and 9(DDR3-1866)

• 8-bit pre-fetch

• Burst Length: 8 , 4 with tCCD = 4 which does not allow seamless read

or write [either On the fly using A12 or MRS]

• Bi-directional Differential Data-Strobe

• Internal(self) calibration : Internal self calibration through ZQ pin

(RZQ : 240 ohm ± 1%)

• On Die Termination using ODT pin

• Average Refresh Period 7.8us at lower than T

CASE

85C, 3.9us at

85C < T

CASE

< 95 C

• Support Industrial Temp ( -4095C )

- tREFI 7.8us at -40 °C ≤ TCASE ≤ 85°C

- tREFI 3.9us at 85 °C < TCASE ≤ 95°C

• Asynchronous Reset

• Package : 96 balls FBGA - x16

• All of Lead-Free products are compliant for RoHS

• All of products are Halogen-free

The 4Gb DDR3 SDRAM E-die is organized as a 32Mbit x 16I/Os x 8banks,

device. This synchronous device achieves high speed double-data-rate

transfer rates of up to 1866Mb/sec/pin (DDR3-1866) for general applica-

tions.

The chip is designed to comply with the following key DDR3 SDRAM fea-

tures such as posted CAS, Programmable CWL, Internal (Self) Calibration,

On Die Termination using ODT pin and Asynchronous Reset .

All of the control and address inputs are synchronized with a pair of exter-

nally supplied differential clocks. Inputs are latched at the crosspoint of dif-

ferential clocks (CK rising and CK

falling). All I/Os are synchronized with a

pair of bidirectional strobes (DQS and DQS

) in a source synchronous fash-

ion. The address bus is used to convey row, column, and bank address

information in a RAS

/CAS multiplexing style. The DDR3 device operates

with a single 1.35V(1.28V~1.45V) or 1.5V(1.425V~1.575V) power supply

and 1.35V(1.28V~1.45V) or 1.5V(1.425V~1.575V) V

DDQ

.

The 4Gb DDR3L E-die device is available in 96ball FBGAs(x16).

NOTE : 1. This data sheet is an abstract of full DDR3 specification and does not cover the common features which are described in “DDR3 SDRAM Device Operation & Timing

Diagram”.

2. The functionality described and the timing specifications included in this data sheet are for the DLL Enabled mode of operation.

剩余70页未读,继续阅读

资源评论

tosongsong

- 粉丝: 0

- 资源: 3

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功