没有合适的资源?快使用搜索试试~ 我知道了~

de0-nano-soc_5CSEMA4U23C6N 开发板原理图

温馨提示

试读

30页

de0-nano-soc_5CSEMA4U23C6N 开发板原理图 开发中可以参考

资源推荐

资源详情

资源评论

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

ALTERA Cyclone V SoC Development & Education Board (DE1-SoC)

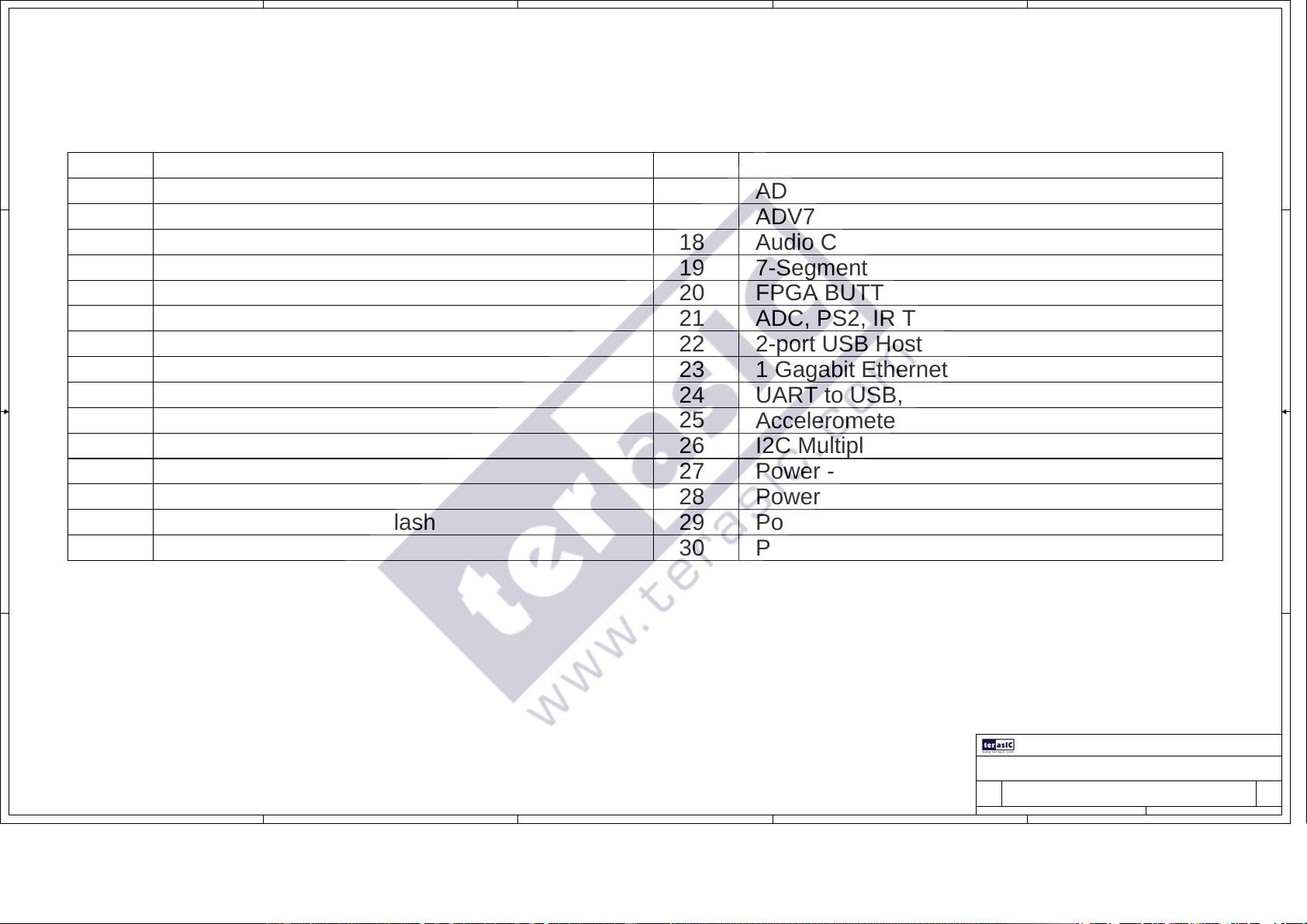

CONTENT

1 Cover Page

PAGE PAGE CONTENT

2

3

4

5

6

7

8

9

10

11

12

13

14

Block Diagram

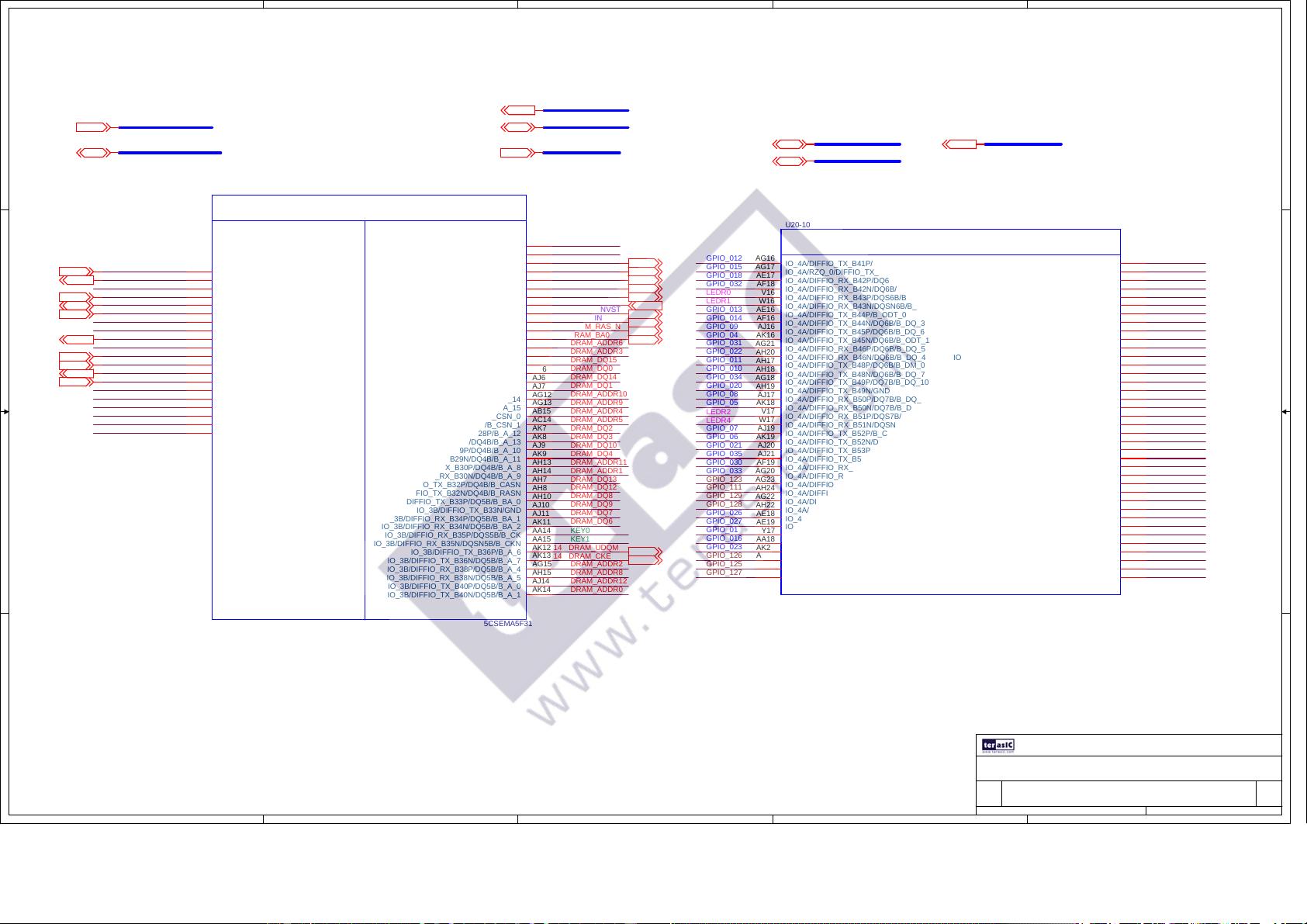

FPGA BANK 3, BANK 4

FPGA BANK 5, BANK 6

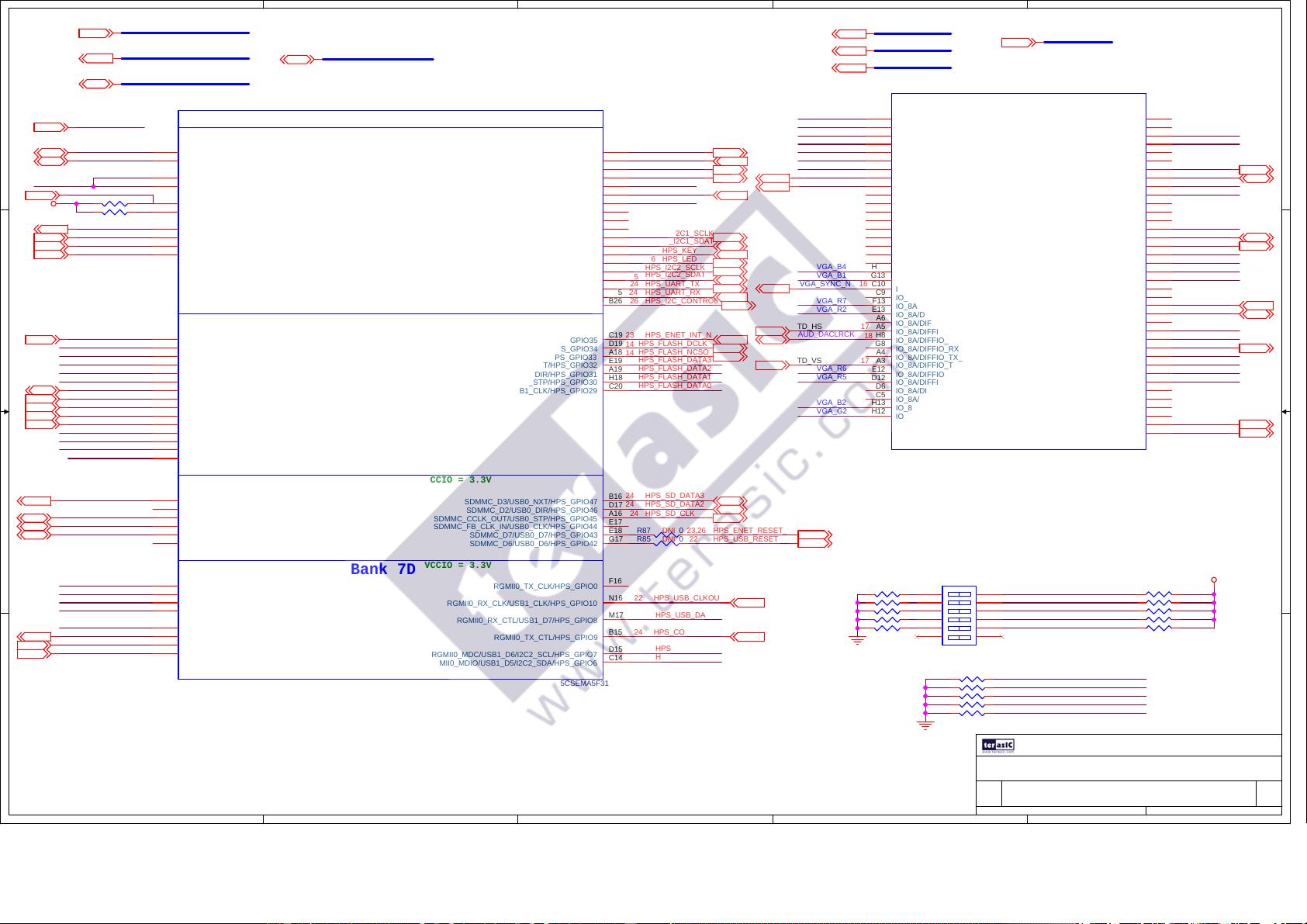

FPGA BANK 7, BANK 8

FPGA Clocks, GND

FPGA Configuration

FPGA Decoupling

FPGA Power

USB Blaster II

JTAG Chain

GPIO 0

GPIO 1

SDRAM, HPS QSPI Flash

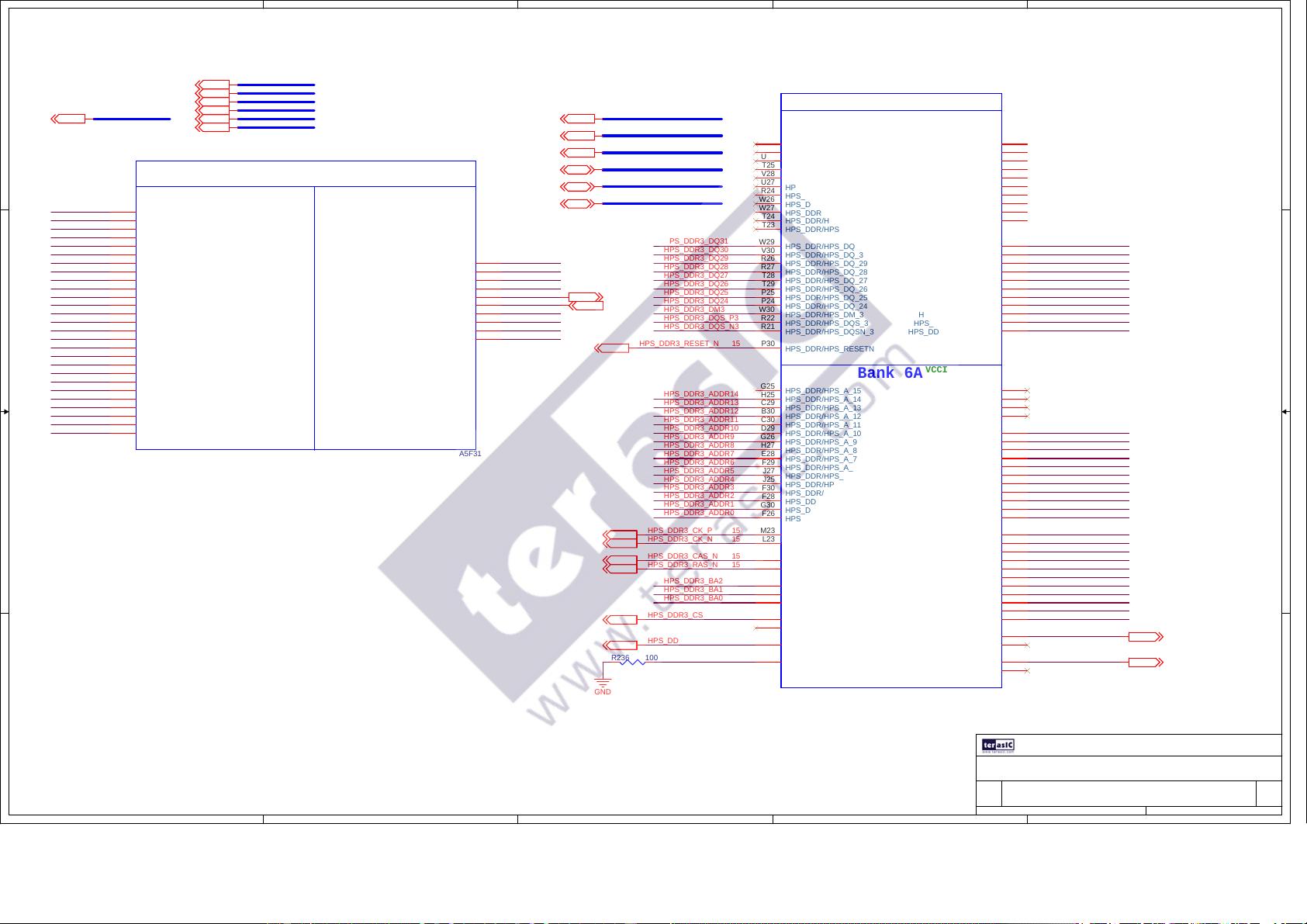

HPS DDR3 SDRAM15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

ADV7123 VGA

ADV7180 Video Decoder

Audio CODEC

7-Segment Display, LED

FPGA BUTTON, Switch

ADC, PS2, IR Tx, IR Rx

2-port USB Host

1 Gagabit Ethernet

UART to USB, SD CARD

Accelerometer, LTC Connector

I2C Multiplexer, HPS BUTTON, HPS LED

Power - 1.1V

Power - 5V, 3.3V

Power - 9V, 2.5V, 1.5V

Power - 1.2V, 1.8V, DDR3 VREF, DDR3 VTT

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page F

DE1-SoC Board

B

130Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page F

DE1-SoC Board

B

130Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Cover Page F

DE1-SoC Board

B

130Thursday, November 20, 2014

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram F

DE1-SoC Board

B

230Friday, December 19, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram F

DE1-SoC Board

B

230Friday, December 19, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

Block Diagram F

DE1-SoC Board

B

230Friday, December 19, 2014

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VCCIO = 3.3V

VCCIO = 3.3V

USB_B2_DATA1

USB_B2_DATA2

USB_B2_DATA3

USB_B2_DATA4

USB_B2_DATA6

USB_B2_DATA7

GPIO_012

GPIO_015

GPIO_018

GPIO_032

LEDR0

LEDR1

GPIO_013

GPIO_014

GPIO_09

GPIO_04

GPIO_031

GPIO_022

GPIO_011

GPIO_010

GPIO_034

GPIO_020

GPIO_08

GPIO_05

LEDR2

LEDR4

GPIO_07

GPIO_06

GPIO_021

GPIO_035

GPIO_030

GPIO_033

GPIO_123

GPIO_111

GPIO_129

GPIO_128

GPIO_026

GPIO_027

GPIO_01

GPIO_016

GPIO_023

GPIO_126

GPIO_028

GPIO_029

GPIO_03

GPIO_017

GPIO_124

GPIO_122

GPIO_121

GPIO_120

GPIO_131

GPIO_130

GPIO_019

GPIO_024

GPIO_117

GPIO_118

GPIO_19

GPIO_119

GPIO_132

GPIO_15

LEDR3

LEDR5

GPIO_113

GPIO_116

GPIO_115

GPIO_114

GPIO_025

GPIO_133

LEDR6

GPIO_134

GPIO_110

GPIO_112

GPIO_17

GPIO_18

GPIO_135

GPIO_13

GPIO_11

GPIO_12

GPIO_125

GPIO_127

GPIO_14

GPIO_16

SW0

SW1

SW2

SW5

DRAM_ADDR10

DRAM_ADDR12

DRAM_ADDR0

DRAM_DQ0

DRAM_DQ2

DRAM_DQ3

DRAM_DQ12

DRAM_DQ4

DRAM_DQ9

DRAM_DQ6

DRAM_DQ7

DRAM_DQ8

DRAM_DQ5

DRAM_DQ10

DRAM_DQ11

DRAM_DQ1

DRAM_DQ13

DRAM_DQ14

DRAM_DQ15

DRAM_ADDR6

DRAM_ADDR4

DRAM_ADDR8

DRAM_ADDR1

DRAM_ADDR11

DRAM_ADDR9

DRAM_ADDR2

DRAM_ADDR3

DRAM_ADDR5

KEY1

KEY0

DRAM_DQ[15..0]

14

KEY[3..0] 6,20

DRAM_ADDR[12..0]

6,14

USB_SDA 10

USB_B2_DATA[7..0] 7,10

USB_B2_CLK 10

USB_RESET_n 10

USB_EMPTY 10

USB_FULL 10

USB_WR_n 10

USB_RD_n 10

USB_OE_n 10

USB_SCL 10

GPIO_0[35..0]

6,12

GPIO_1[35..0]

6,13

SW[9..0] 7,20

LEDR[9..0]

4,19

FAN_CTRL 7

DRAM_CAS_N14

DRAM_CS_N14

DRAM_RAS_N14

DRAM_BA014

DRAM_UDQM14

DRAM_CKE14

DRAM_WE_N14

DRAM_LDQM14

ADC_SCLK21

ADC_DOUT

21

ADC_DIN21

ADC_CONVST21

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 3, BANK 4 F

DE1-SoC Board

B

330Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 3, BANK 4 F

DE1-SoC Board

B

330Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 3, BANK 4 F

DE1-SoC Board

B

330Thursday, November 20, 2014

Bank 4A

5CSEMA5F31

U20-10

IO_4A/RZQ_0/DIFFIO_TX_B41N

AG17

IO_4A/DIFFIO_RX_B42N/DQ6B/B_DQ_0

AF18

IO_4A/DIFFIO_TX_B41P/DQ6B/B_DQ_2

AG16

IO_4A/DIFFIO_RX_B42P/DQ6B/B_DQ_1

AE17

IO_4A/DIFFIO_RX_B43N/DQSN6B/B_DQSN_0

W16

IO_4A/DIFFIO_TX_B44N/DQ6B/B_DQ_3

AF16

IO_4A/DIFFIO_RX_B43P/DQS6B/B_DQS_0

V16

IO_4A/DIFFIO_TX_B44P/B_ODT_0

AE16

IO_4A/DIFFIO_TX_B45N/DQ6B/B_ODT_1

AK16

IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_4

AH20

IO_4A/DIFFIO_TX_B45P/DQ6B/B_DQ_6

AJ16

IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_5

AG21

IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_7

AH18

IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_0

AH17

IO_4A/DIFFIO_TX_B49N/GND

AH19

IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_8

AK18

IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_10

AG18

IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_9

AJ17

IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_1

W17

IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_11

AK19

IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_1

V17

IO_4A/DIFFIO_TX_B52P/B_CKE_1

AJ19

IO_4A/DIFFIO_TX_B53N/DQ7B/B_CKE_0

AJ21

IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_12

AG20

IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_14

AJ20

IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_13

AF19

IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_15

AH24

IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_1

AG23

IO_4A/DIFFIO_TX_B57N/GND

AH22

IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_16

AE19

IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_18

AG22

IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_17

AE18

IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_2

AA18

IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_19

AK22

IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_2

Y17

IO_4A/DIFFIO_TX_B60P/B_RESETN

AK21

IO_4A/DIFFIO_TX_B61N/DQ8B/GND

AJ22

IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_20

AF21

IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_22

AH23

IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_21

AF20

IO_4A/DIFFIO_RX_B63N/GND

AA19

IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_23

AK24

IO_4A/DIFFIO_RX_B63P/GND

Y18

IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_2

AK23

IO_4A/DIFFIO_TX_B65N/GND

AJ25

IO_4A/DIFFIO_RX_B66N/DQ9B/B_DQ_24

AF24

IO_4A/DIFFIO_TX_B65P/DQ9B/B_DQ_26

AJ24

IO_4A/DIFFIO_RX_B66P/DQ9B/B_DQ_25

AF23

IO_4A/DIFFIO_RX_B67N/DQSN9B/B_DQSN_3

AD19

IO_4A/DIFFIO_TX_B68N/DQ9B/B_DQ_27

AK26

IO_4A/DIFFIO_RX_B67P/DQS9B/B_DQS_3

AC20

IO_4A/DIFFIO_TX_B68P/GND

AJ26

IO_4A/DIFFIO_TX_B69N/DQ9B/GND

AH25

IO_4A/DIFFIO_RX_B70N/DQ9B/B_DQ_28

AE23

IO_4A/DIFFIO_TX_B69P/DQ9B/B_DQ_30

AG25

IO_4A/DIFFIO_RX_B70P/DQ9B/B_DQ_29

AE22

IO_4A/DIFFIO_RX_B71N/GND

W19

IO_4A/DIFFIO_TX_B72N/DQ9B/B_DQ_31

AK27

IO_4A/DIFFIO_RX_B71P/GND

V18

IO_4A/DIFFIO_TX_B72P/DQ9B/B_DM_3

AJ27

IO_4A/DIFFIO_TX_B73N/GND

AK29

IO_4A/DIFFIO_RX_B74N/DQ10B/B_DQ_32

AD21

IO_4A/DIFFIO_TX_B73P/DQ10B/B_DQ_34

AK28

IO_4A/DIFFIO_RX_B74P/DQ10B/B_DQ_33

AD20

IO_4A/DIFFIO_RX_B75N/DQSN10B/B_DQSN_4

AA20

IO_4A/DIFFIO_TX_B76N/DQ10B/B_DQ_35

AH27

IO_4A/DIFFIO_RX_B75P/DQS10B/B_DQS_4

Y19

IO_4A/DIFFIO_TX_B76P/GND

AG26

IO_4A/DIFFIO_TX_B77N/DQ10B/GND

AF26

IO_4A/DIFFIO_RX_B78N/DQ10B/B_DQ_36

AC23

IO_4A/DIFFIO_TX_B77P/DQ10B/B_DQ_38

AF25

IO_4A/DIFFIO_RX_B78P/DQ10B/B_DQ_37

AC22

IO_4A/DIFFIO_RX_B79N/GND

AB21

IO_4A/DIFFIO_TX_B80N/DQ10B/B_DQ_39

AE24

IO_4A/DIFFIO_RX_B79P/GND

AA21

IO_4A/DIFFIO_TX_B80P/DQ10B/B_DM_4

AD24

Bank 3

Bank 3A Bank 3B

5CSEMA5F31

U20-9

IO_3A/PR_DONE/DIFFIO_RX_B7N

AF5

IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1B

AG8

IO_3A/PR_ERROR/DIFFIO_RX_B7P

AF4

IO_3A/DIFFIO_TX_B8P/DQ1B

AF9

IO_3A/DIFFIO_TX_B9N

AG7

IO_3A/DIFFIO_RX_B10N/DQ2B

AH2

IO_3A/DIFFIO_TX_B9P/DQ2B

AF8

IO_3A/DIFFIO_RX_B10P/DQ2B

AG1

IO_3A/DIFFIO_RX_B11N/DQSN2B

AB12

IO_3A/DIFFIO_TX_B12N/DQ2B

AG6

IO_3A/DIFFIO_RX_B11P/DQS2B

AA12

IO_3A/DIFFIO_TX_B12P

AF6

IO_3A/DIFFIO_TX_B13N/DQ2B

AH5

IO_3A/DIFFIO_RX_B14N/DQ2B

AJ2

IO_3A/DIFFIO_TX_B13P/DQ2B

AG5

IO_3A/DIFFIO_RX_B14P/DQ2B

AJ1

IO_3A/DIFFIO_RX_B15N

AD12

IO_3A/DIFFIO_TX_B16N/DQ2B

AH3

IO_3A/DIFFIO_RX_B15P

AC12

IO_3A/DIFFIO_TX_B16P/DQ2B

AG2

IO_3B/DIFFIO_TX_B17N

AH9

IO_3B/DIFFIO_RX_B18N/DQ3B

AG11

IO_3B/DIFFIO_TX_B17P/DQ3B

AG10

IO_3B/DIFFIO_RX_B18P/DQ3B

AF11

IO_3B/DIFFIO_RX_B19N/DQSN3B

AB13

IO_3B/DIFFIO_TX_B20N/DQ3B

AK3

IO_3B/DIFFIO_RX_B19P/DQS3B

AA13

IO_3B/DIFFIO_TX_B20P

AK2

IO_3B/DIFFIO_TX_B21N/DQ3B

AK4

IO_3B/DIFFIO_RX_B22N/DQ3B

AF13

IO_3B/DIFFIO_TX_B21P/DQ3B

AJ4

IO_3B/DIFFIO_RX_B22P/DQ3B

AE13

IO_3B/DIFFIO_RX_B23N

AE14

IO_3B/DIFFIO_TX_B24N/DQ3B

AK6

IO_3B/DIFFIO_RX_B23P

AD14

IO_3B/DIFFIO_TX_B24P/DQ3B

AJ5

IO_3B/DIFFIO_TX_B25N/GND

AJ7

IO_3B/DIFFIO_RX_B26N/DQ4B/B_A_15

AG13

IO_3B/DIFFIO_TX_B25P/DQ4B/B_WEN

AJ6

IO_3B/DIFFIO_RX_B26P/DQ4B/B_A_14

AG12

IO_3B/DIFFIO_RX_B27N/DQSN4B/B_CSN_1

AC14

IO_3B/DIFFIO_TX_B28N/DQ4B/B_A_13

AK8

IO_3B/DIFFIO_RX_B27P/DQS4B/B_CSN_0

AB15

IO_3B/DIFFIO_TX_B28P/B_A_12

AK7

IO_3B/DIFFIO_TX_B29N/DQ4B/B_A_11

AK9

IO_3B/DIFFIO_RX_B30N/DQ4B/B_A_9

AH14

IO_3B/DIFFIO_TX_B29P/DQ4B/B_A_10

AJ9

IO_3B/DIFFIO_RX_B30P/DQ4B/B_A_8

AH13

IO_3B/DIFFIO_TX_B32N/DQ4B/B_RASN

AH8

IO_3B/DIFFIO_TX_B32P/DQ4B/B_CASN

AH7

IO_3B/DIFFIO_TX_B33N/GND

AJ10

IO_3B/DIFFIO_RX_B34N/DQ5B/B_BA_2

AK11

IO_3B/DIFFIO_TX_B33P/DQ5B/B_BA_0

AH10

IO_3B/DIFFIO_RX_B34P/DQ5B/B_BA_1

AJ11

IO_3B/DIFFIO_RX_B35N/DQSN5B/B_CKN

AA15

IO_3B/DIFFIO_TX_B36N/DQ5B/B_A_7

AK13

IO_3B/DIFFIO_RX_B35P/DQS5B/B_CK

AA14

IO_3B/DIFFIO_TX_B36P/B_A_6

AK12

IO_3B/DIFFIO_RX_B38N/DQ5B/B_A_5

AH15

IO_3B/DIFFIO_RX_B38P/DQ5B/B_A_4

AG15

IO_3B/DIFFIO_TX_B40N/DQ5B/B_A_1

AK14

IO_3B/DIFFIO_TX_B40P/DQ5B/B_A_0

AJ14

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VCCIO = 3.3V

VCCIO = 1.5V

VCCIO = 1.5V

VCCIO = 3.3V

VCCIO = 3.3V

HPS_DDR3_RZQ

HPS_DDR3_DQ24

HPS_DDR3_DQ25

HPS_DDR3_DQ26

HPS_DDR3_DQ27

HPS_DDR3_DQ28

HPS_DDR3_DQ29

HPS_DDR3_DQ30

HPS_DDR3_DQ31

HPS_DDR3_DM3

HPS_DDR3_DQS_P3

HPS_DDR3_DQS_N3

HPS_DDR3_ADDR11

HPS_DDR3_ADDR12

HPS_DDR3_ADDR13

HPS_DDR3_ADDR14

HPS_DDR3_BA1

HPS_DDR3_BA0

HPS_DDR3_BA2

HPS_DDR3_ADDR7

HPS_DDR3_ADDR8

HPS_DDR3_ADDR9

HPS_DDR3_ADDR10

HPS_DDR3_ADDR3

HPS_DDR3_ADDR4

HPS_DDR3_ADDR5

HPS_DDR3_ADDR6

HPS_DDR3_ADDR0

HPS_DDR3_ADDR1

HPS_DDR3_ADDR2

HPS_DDR3_DQ16

HPS_DDR3_DQ17

HPS_DDR3_DQ18

HPS_DDR3_DQ19

HPS_DDR3_DQ20

HPS_DDR3_DQ21

HPS_DDR3_DQ22

HPS_DDR3_DQ23

HPS_DDR3_DM2

HPS_DDR3_DQS_P2

HPS_DDR3_DQS_N2

HPS_DDR3_DQ8

HPS_DDR3_DQ9

HPS_DDR3_DQ10

HPS_DDR3_DQ11

HPS_DDR3_DQ12

HPS_DDR3_DQ13

HPS_DDR3_DQ14

HPS_DDR3_DQ15

HPS_DDR3_DM1

HPS_DDR3_DQS_P1

HPS_DDR3_DQS_N1

HPS_DDR3_DQ0

HPS_DDR3_DQ1

HPS_DDR3_DQ2

HPS_DDR3_DQ3

HPS_DDR3_DQ4

HPS_DDR3_DQ5

HPS_DDR3_DQ6

HPS_DDR3_DQ7

HPS_DDR3_DM0

HPS_DDR3_DQS_P0

HPS_DDR3_DQS_N0

LEDR7

LEDR8

LEDR9

HEX12

HEX11

HEX06

HEX13

HEX05

HEX03

HEX15

HEX14

HEX04

HEX02

HEX01

HEX30

HEX31

HEX54

HEX35

HEX20

HEX40

HEX36

HEX56

HEX42

HEX41

HEX44

HEX43

HEX45

HEX24

HEX23

HEX25

HEX26

HEX34

HEX51

HEX46

HEX50

GND

HPS_DDR3_CK_P 15

HPS_DDR3_CK_N 15

HPS_DDR3_CAS_N 15

HPS_DDR3_RAS_N 15

HPS_DDR3_CS_N 15

HPS_DDR3_RESET_N 15

HPS_DDR3_WE_N 15

HPS_DDR3_CKE15

HPS_DDR3_ODT15

LEDR[9..0]

3,19

HEX0[6..0]

7,19

HEX1[6..0]

7,19

HEX2[6..0]

6,19

HEX3[6..0]

7,19

HEX4[6..0]

19

HEX5[6..0]

6,19

IRDA_TXD

21

IRDA_RXD21

HPS_DDR3_DQS_N[3..0] 15

HPS_DDR3_DQS_P[3..0] 15

HPS_DDR3_DQ[31..0] 15

HPS_DDR3_DM[3..0] 15

HPS_DDR3_BA[2..0] 15

HPS_DDR3_ADDR[14..0] 15

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 5, BANK 6 F

DE1-SoC Board

B

430Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 5, BANK 6 F

DE1-SoC Board

B

430Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 5, BANK 6 F

DE1-SoC Board

B

430Thursday, November 20, 2014

R236 100

Bank 5

Bank 5A Bank 5B

5CSEMA5F31

U20-11

IO_5A/RZQ_1/DIFFIO_TX_R1P/DQ1R

AG27

IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1R

AH28

IO_5A/DIFFIO_RX_R4P/DQ1R

W20

IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1R

AH29

IO_5A/DIFFIO_RX_R4N/DQ1R

Y21

IO_5A/DIFFIO_RX_R6P/DQS1R

W21

IO_5A/DIFFIO_RX_R6N/DQSN1R

W22

IO_5A/DIFFIO_TX_R7P/DQ1R

AA25

IO_5A/DIFFIO_RX_R8P/DQ1R

AB22

IO_5A/DIFFIO_TX_R7N

AB26

IO_5A/DIFFIO_RX_R8N/DQ1R

AB23

IO_5A/DIFFIO_RX_R9P

AA24

IO_5A/DIFFIO_TX_R10P/DQ2R

AE27

IO_5A/DIFFIO_RX_R9N

AB25

IO_5A/DIFFIO_TX_R10N/DQ2R

AE28

IO_5A/DIFFIO_RX_R11P/DQ2R

Y23

IO_5A/DIFFIO_TX_R12P/DQ2R

AG28

IO_5A/DIFFIO_RX_R11N/DQ2R

Y24

IO_5A/DIFFIO_TX_R12N/DQ2R

AF28

IO_5A/DIFFIO_RX_R13P/DQS2R

V23

IO_5A/DIFFIO_TX_R14P

AF29

IO_5A/DIFFIO_RX_R13N/DQSN2R

W24

IO_5A/DIFFIO_TX_R14N/DQ2R

AF30

IO_5A/DIFFIO_RX_R15P/DQ2R

AD26

IO_5A/DIFFIO_TX_R16P/DQ2R

AH30

IO_5A/DIFFIO_RX_R15N/DQ2R

AC27

IO_5A/DIFFIO_TX_R16N

AG30

IO_5B/DIFFIO_RX_R17P

W25

IO_5B/DIFFIO_TX_R18P/DQ3R

AC28

IO_5B/DIFFIO_RX_R17N

V25

IO_5B/DIFFIO_TX_R18N/DQ3R

AC29

IO_5B/DIFFIO_RX_R19P/DQ3R

AB30

IO_5B/DIFFIO_TX_R20P/DQ3R

AB28

IO_5B/DIFFIO_RX_R19N/DQ3R

AA30

IO_5B/DIFFIO_TX_R20N/DQ3R

AA28

IO_5B/DIFFIO_TX_R24P/DQ3R

AD30

IO_5B/RZQ_2/DIFFIO_TX_R24N

AC30

Bank 6

Bank 6B

Bank 6A

5CSEMA5F31

U20-12

HPS_DDR/HPS_DM_4

W27

HPS_DDR/HPS_DQ_39

Y29

HPS_DDR/HPS_DQ_37

U25

HPS_DDR/HPS_DQ_38

V27

HPS_DDR/HPS_DQ_36

T25

HPS_DDR/HPS_DQS_4

T24

HPS_GPI13

Y28

HPS_DDR/HPS_DQSN_4

T23

HPS_DDR/HPS_DQ_35

V28

HPS_DDR/HPS_DQ_33

R24

HPS_DDR/HPS_DQ_34

U27

HPS_DDR/HPS_DQ_32

W26

HPS_GPI12

V29

HPS_GPI11

U20

HPS_DDR/HPS_DM_3

W30

HPS_GPI10

T21

HPS_DDR/HPS_DQ_31

W29

HPS_DDR/HPS_DQ_29

R26

HPS_DDR/HPS_DQ_30

V30

HPS_DDR/HPS_DQ_28

R27

HPS_DDR/HPS_DQS_3

R22

HPS_GPI9

U28

HPS_DDR/HPS_DQSN_3

R21

HPS_DDR/HPS_DQ_27

T28

HPS_DDR/HPS_DQ_25

P25

HPS_DDR/HPS_DQ_26

T29

HPS_DDR/HPS_DQ_24

P24

HPS_GPI8

T30

HPS_GPI7

V20

HPS_DDR/HPS_DM_2

R28

HPS_GPI6

P22

HPS_DDR/HPS_DQ_23

R29

HPS_DDR/HPS_DQ_21

P27

HPS_DDR/HPS_DQ_22

N27

HPS_DDR/HPS_DQ_20

P26

HPS_GPI5

P29

HPS_DDR/HPS_DQS_2

R19

HPS_DDR/HPS_RESETN

P30

HPS_DDR/HPS_DQSN_2

R18

HPS_DDR/HPS_DQ_19

N28

HPS_DDR/HPS_DQ_17

T26

HPS_DDR/HPS_DQ_18

N29

HPS_DDR/HPS_DQ_16

U26

HPS_GPI4

N30

HPS_GPI3

M22

HPS_DDR/HPS_DM_1

M28

HPS_GPI2

N23

HPS_DDR/HPS_DQ_15

M30

HPS_DDR/HPS_DQ_13

M27

HPS_DDR/HPS_DQ_14

L28

HPS_DDR/HPS_DQ_12

M26

HPS_DDR/HPS_CKE_0

L29

HPS_DDR/HPS_DQS_1

N25

HPS_DDR/HPS_CKE_1

L30

HPS_DDR/HPS_DQSN_1

N24

HPS_DDR/HPS_DQ_11

K27

HPS_DDR/HPS_DQ_9

L26

HPS_DDR/HPS_DQ_10

K29

HPS_DDR/HPS_DQ_8

K26

HPS_GPI1

J26

HPS_GPI0

M25

HPS_DDR/HPS_DM_0

K28

HPS_DDR/HPS_DQ_7

J29

HPS_DDR/HPS_DQ_5

L24

HPS_DDR/HPS_DQ_6

J30

HPS_DDR/HPS_DQ_4

L25

HPS_DDR/HPS_ODT_1

H29

HPS_DDR/HPS_DQS_0

N18

HPS_DDR/HPS_ODT_0

H28

HPS_DDR/HPS_DQSN_0

M19

HPS_DDR/HPS_DQ_3

G28

HPS_DDR/HPS_DQ_1

K22

HPS_DDR/HPS_DQ_2

H30

HPS_DDR/HPS_DQ_0

K23

HPS_DDR/HPS_A_0

F26

HPS_DDR/HPS_A_1

G30

HPS_DDR/HPS_A_4

J25

HPS_DDR/HPS_A_2

F28

HPS_DDR/HPS_A_5

J27

HPS_DDR/HPS_A_3

F30

HPS_DDR/HPS_CK

M23

HPS_DDR/HPS_A_6

F29

HPS_DDR/HPS_CKN

L23

HPS_DDR/HPS_A_7

E28

HPS_DDR/HPS_BA_1

J24

HPS_DDR/HPS_BA_0

E29

HPS_DDR/HPS_BA_2

J23

HPS_DDR/HPS_CASN

E27

HPS_DDR/HPS_RASN

D30

HPS_DDR/HPS_A_8

H27

HPS_DDR/HPS_A_10

D29

HPS_DDR/HPS_A_9

G26

HPS_DDR/HPS_A_11

C30

HPS_DDR/HPS_CSN_0

H24

HPS_DDR/HPS_A_12

B30

HPS_DDR/HPS_CSN_1

K21

HPS_DDR/HPS_A_13

C29

HPS_DDR/HPS_A_14

H25

HPS_DDR/HPS_WEN

C28

HPS_DDR/HPS_A_15

G25

HPS_RZQ_0

D27

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

VCCIO = 3.3V

VCCIO = 3.3V

VCCIO = 3.3V

VCCIO = 3.3V

VCCIO = 3.3V

(BOOTSEL0)

(BOOTSEL1)

(BOOTSEL2)

Default Setting: BOOTSEL[2:0]=101 (Boot from SD CARD)

CLKSEL[1:0]=0

(CLOCKSEL0)

(CLOCKSEL1)

(BOOTSEL0)

(BOOTSEL1)

(BOOTSEL2)

(CLOCKSEL0)

(CLOCKSEL1)

HPS_CLOCK1_25

HPS_CLOCK2_25

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

HPS_BOOTSEL0

HPS_FLASH_NCSO

HPS_BOOTSEL2

HPS_SPIM_SS

HPS_CLOCKSEL1

HPS_CLOCKSEL1

HPS_BOOTSEL2

HPS_BOOTSEL0

HPS_ENET_TX_DATA0

HPS_ENET_TX_DATA1

HPS_ENET_TX_DATA2

HPS_ENET_TX_DATA3

HPS_ENET_RX_DATA0

HPS_ENET_RX_DATA1

HPS_ENET_RX_DATA2

HPS_ENET_RX_DATA3

HPS_FLASH_DATA2

HPS_FLASH_DATA1

HPS_FLASH_DATA0

HPS_FLASH_DATA3

HPS_USB_DATA0

HPS_USB_DATA1

HPS_USB_DATA2

HPS_USB_DATA3

HPS_USB_DATA4

HPS_USB_DATA5

HPS_USB_DATA6

HPS_USB_DATA7

HPS_CLK_25

VGA_R0

VGA_B0

VGA_R1

VGA_R3

VGA_R4

VGA_R5

VGA_R2

VGA_R6

VGA_B5

VGA_B3

VGA_B4

VGA_B2

VGA_B1

VGA_R7

VGA_G5

VGA_G2

VGA_G7

VGA_G6

VGA_G4

VGA_G1

VGA_G0

TD_DATA7

TD_DATA6

TD_DATA5

TD_DATA4

TD_DATA3

TD_DATA2

TD_DATA1

TD_DATA0

VGA_G3

VCC3P3

VCC3P3

HPS_CLK_25 6

HPS_FLASH_NCSO

14

HPS_SPIM_SS

25

HPS_TDO 11

HPS_TDI 11

HPS_TMS 11

HPS_TCK 11

HPS_SPIM_CLK25

HPS_SPIM_MOSI25

HPS_SPIM_MISO25

HPS_UART_TX24

HPS_UART_RX24

HPS_I2C2_SCLK25

HPS_I2C2_SDAT

25

HPS_LED26

HPS_KEY26

HPS_I2C1_SCLK

25,26

HPS_I2C1_SDAT

25,26

HPS_ENET_GTX_CLK 23

HPS_ENET_TX_EN 23

HPS_ENET_MDC 23

HPS_ENET_MDIO 23

HPS_ENET_RX_CLK 23

HPS_ENET_RX_DV 23

HPS_ENET_INT_N23

HPS_FLASH_DCLK

14

HPS_ENET_RX_DATA[3..0]

23

HPS_ENET_TX_DATA[3..0]

23

HPS_FLASH_DATA[3..0]

14

HPS_ENET_RESET_N23,26

HPS_USB_RESET22

HPS_SD_DATA0 24

HPS_SD_DATA1 24

HPS_SD_CMD 24

HPS_SD_DATA224

HPS_SD_DATA324

HPS_SD_CLK24

HPS_LTC_GPIO 25

HPS_USB_STP 22

HPS_USB_DIR 22

HPS_USB_NXT 22

HPS_USB_CLKOUT22

HPS_CONV_USB_N24

AUD_ADCDAT

18

AUD_ADCLRCK

18

AUD_BCLK

18

AUD_DACLRCK

18

AUD_XCK18

AUD_DACDAT18

VGA_SYNC_N 16

VGA_HS 16

VGA_VS 16

VGA_R[7..0]

16

VGA_G[7..0]

16

VGA_B[7..0]

6,16

TD_RESET_N17

TD_HS 17

TD_VS 17

TD_DATA[7..0] 17

FPGA_I2C_SCLK26

FPGA_I2C_SDAT

26

HPS_GSENSOR_INT25

HPS_I2C_CONTROL26

VGA_BLANK_N16

HPS_USB_DATA[7..0]

22

HPS_WARM_RST_N

10,11,26

HPS_RESET_N

10,26

JTAG_TRST

10,11

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 7, BANK 8 F

DE1-SoC Board

B

530Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 7, BANK 8 F

DE1-SoC Board

B

530Thursday, November 20, 2014

Title

Size Document Number Rev

Date: Sheet

of

Copyright (c) 2013 by Terasic Technologies Inc. Taiwan.

No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.

All rights reserved.

FPGA BANK 7, BANK 8 F

DE1-SoC Board

B

530Thursday, November 20, 2014

R104 1K R107 10K DNI

R87 0DNI

R85 0DNI

Bank 7

Bank 7A

Bank 7B

Bank 7C

Bank 7D

5CSEMA5F31

U20-13

HPS_NRST

C27

HPS_NPOR

F23

HPS_TDO

B28

HPS_TMS

A29

HPS_TCK

H22

HPS_TRST

A28

HPS_TDI

B27

HPS_PORSEL

F24

HPS_CLK1

D25

HPS_CLK2

F25

TRACE_CLK/HPS_GPIO48

B26

TRACE_D0/SPIS0_CLK/UART0_RX/HPS_GPIO49

B25

TRACE_D1/SPIS0_MOSI/UART0_TX/HPS_GPIO50

C25

TRACE_D2/SPIS0_MISO/I2C1_SDA/HPS_GPIO51

A25

TRACE_D3/SPIS0_SS0/I2C1_SCL/HPS_GPIO52

H23

TRACE_D4/SPIS1_CLK/CAN1_RX/HPS_GPIO53

A24

TRACE_D5/SPIS1_MOSI/CAN1_TX/HPS_GPIO54

G21

TRACE_D6/SPIS1_SS0/I2C0_SDA/HPS_GPIO55

C24

TRACE_D7/SPIS1_MISO/I2C0_SCL/HPS_GPIO56

E23

SPIM0_CLK/I2C1_SDA/UART0_CTS/HPS_GPIO57

A23

SPIM0_MOSI/I2C1_SCL/UART0_RTS/HPS_GPIO58

C22

SPIM0_MISO/CAN1_RX/UART1_CTS/HPS_GPIO59

B23

SPIM0_SS0,BOOTSEL0/SPIM0_SS0/CAN1_TX/UART1_RTS/HPS_GPIO60

H20

UART0_RX/CAN0_RX/SPIM0_SS1/HPS_GPIO61

B22

UART0_TX,CLKSEL1/UART0_TX/CAN0_TX/SPIM1_SS1/HPS_GPIO62

G22

I2C0_SDA/UART1_RX/SPIM1_CLK/HPS_GPIO63

C23

I2C0_SCL/UART1_TX/SPIM1_MOSI/HPS_GPIO64

D22

CAN0_RX/UART0_RX/SPIM1_MISO/HPS_GPIO65

E24

CAN0_TX,CLKSEL0/CAN0_TX/UART0_TX/SPIM1_SS0/HPS_GPIO66

D24

NAND_ALE/RGMII1_TX_CLK/QSPI_SS3/HPS_GPIO14

H19

NAND_CE/RGMII1_TXD0/USB1_D0/HPS_GPIO15

F20

NAND_CLE/RGMII1_TXD1/USB1_D1/HPS_GPIO16

J19

NAND_RE/RGMII1_TXD2/USB1_D2/HPS_GPIO17

F21

NAND_RB/RGMII1_TXD3/USB1_D3/HPS_GPIO18

F19

NAND_DQ0/RGMII1_RXD0/HPS_GPIO19

A21

NAND_DQ1/RGMII1_MDIO/I2C3_SDA/HPS_GPIO20

E21

NAND_DQ2/RGMII1_MDC/I2C3_SCL/HPS_GPIO21

B21

NAND_DQ3/RGMII1_RX_CTL/USB1_D4/HPS_GPIO22

K17

NAND_DQ4/RGMII1_TX_CTL/USB1_D5/HPS_GPIO23

A20

NAND_DQ5/RGMII1_RX_CLK/USB1_D6/HPS_GPIO24

G20

NAND_DQ6/RGMII1_RXD1/USB1_D7/HPS_GPIO25

B20

NAND_DQ7/RGMII1_RXD2/HPS_GPIO26

B18

NAND_WP/RGMII1_RXD3/QSPI_SS2/HPS_GPIO27

D21

NAND_WE,BOOTSEL2/NAND_WE/QSPI_SS1/HPS_GPIO28

D20

QSPI_IO0/USB1_CLK/HPS_GPIO29

C20

QSPI_IO1/USB1_STP/HPS_GPIO30

H18

QSPI_IO2/USB1_DIR/HPS_GPIO31

A19

QSPI_IO3/USB1_NXT/HPS_GPIO32

E19

QSPI_SS0,BOOTSEL1/QSPI_SS0/HPS_GPIO33

A18

QSPI_CLK/HPS_GPIO34

D19

QSPI_SS1/HPS_GPIO35

C19

SDMMC_CMD/USB0_D0/HPS_GPIO36

F18

SDMMC_PWREN/USB0_D1/HPS_GPIO37

B17

SDMMC_D0/USB0_D2/HPS_GPIO38

G18

SDMMC_D1/USB0_D3/HPS_GPIO39

C17

SDMMC_D4/USB0_D4/HPS_GPIO40

H17

SDMMC_D5/USB0_D5/HPS_GPIO41

C18

SDMMC_D6/USB0_D6/HPS_GPIO42

G17

SDMMC_D7/USB0_D7/HPS_GPIO43

E18

SDMMC_FB_CLK_IN/USB0_CLK/HPS_GPIO44

E17

SDMMC_CCLK_OUT/USB0_STP/HPS_GPIO45

A16

SDMMC_D2/USB0_DIR/HPS_GPIO46

D17

SDMMC_D3/USB0_NXT/HPS_GPIO47

B16

RGMII0_TX_CLK/HPS_GPIO0

F16

RGMII0_TXD0/USB1_D0/HPS_GPIO1

E16

RGMII0_TXD1/USB1_D1/HPS_GPIO2

G16

RGMII0_TXD2/USB1_D2/HPS_GPIO3

D16

RGMII0_TXD3/USB1_D3/HPS_GPIO4

D14

RGMII0_RXD0/USB1_D4/HPS_GPIO5

A15

RGMII0_MDIO/USB1_D5/I2C2_SDA/HPS_GPIO6

C14

RGMII0_MDC/USB1_D6/I2C2_SCL/HPS_GPIO7

D15

RGMII0_RX_CTL/USB1_D7/HPS_GPIO8

M17

RGMII0_TX_CTL/HPS_GPIO9

B15

RGMII0_RX_CLK/USB1_CLK/HPS_GPIO10

N16

RGMII0_RXD1/USB1_STP/HPS_GPIO11

C15

RGMII0_RXD2/USB1_DIR/HPS_GPIO12

E14

RGMII0_RXD3/USB1_NXT/HPS_GPIO13

A14

R108 10K

R95 1K

R99 1K

R110 1K

R97 10K DNI

R234 4.7K

R96 1K

Bank 8A

5CSEMA5F31

U20-14

IO_8A/DIFFIO_TX_T2P/DQ1T

B13

IO_8A/DIFFIO_TX_T2N/DQ1T

A13

IO_8A/DIFFIO_RX_T3P/DQ1T

C13

IO_8A/DIFFIO_RX_T3N/DQ1T

B12

IO_8A/DIFFIO_RX_T5P/DQS1T

F15

IO_8A/DIFFIO_TX_T6P

C12

IO_8A/DIFFIO_RX_T5N/DQSN1T

F14

IO_8A/DIFFIO_TX_T6N/DQ1T

B11

IO_8A/DIFFIO_RX_T7P/DQ1T

D11

IO_8A/DIFFIO_TX_T8P/DQ1T

A9

IO_8A/DIFFIO_RX_T7N/DQ1T

D10

IO_8A/DIFFIO_TX_T8N

A8

IO_8A/DIFFIO_TX_T10P/DQ2T

C7

IO_8A/DIFFIO_TX_T10N/DQ2T

B7

IO_8A/DIFFIO_RX_T11P/DQ2T

E9

IO_8A/DIFFIO_TX_T12P/DQ2T

C8

IO_8A/DIFFIO_RX_T11N/DQ2T

D9

IO_8A/DIFFIO_TX_T12N/DQ2T

B8

IO_8A/DIFFIO_RX_T13P/DQS2T

H14

IO_8A/DIFFIO_TX_T14P

C10

IO_8A/DIFFIO_RX_T13N/DQSN2T

G13

IO_8A/DIFFIO_TX_T14N/DQ2T

C9

IO_8A/DIFFIO_RX_T15P/DQ2T

F13

IO_8A/DIFFIO_TX_T16P/DQ2T

A6

IO_8A/DIFFIO_RX_T15N/DQ2T

E13

IO_8A/DIFFIO_TX_T16N

A5

IO_8A/DIFFIO_RX_T17P

H8

IO_8A/DIFFIO_TX_T18P/DQ3T

A4

IO_8A/DIFFIO_RX_T17N

G8

IO_8A/DIFFIO_TX_T18N/DQ3T

A3

IO_8A/DIFFIO_RX_T19P/DQ3T

E12

IO_8A/DIFFIO_TX_T20P/DQ3T

D6

IO_8A/DIFFIO_RX_T19N/DQ3T

D12

IO_8A/DIFFIO_TX_T20N/DQ3T

C5

IO_8A/DIFFIO_RX_T21P/DQS3T

H13

IO_8A/DIFFIO_TX_T22P

D5

IO_8A/DIFFIO_RX_T21N/DQSN3T

H12

IO_8A/DIFFIO_TX_T22N/DQ3T

C4

IO_8A/DIFFIO_RX_T23P/DQ3T

F11

IO_8A/DIFFIO_TX_T24P/DQ3T

E8

IO_8A/DIFFIO_RX_T23N/DQ3T

E11

IO_8A/DIFFIO_TX_T24N

D7

IO_8A/DIFFIO_RX_T25P

J7

IO_8A/DIFFIO_TX_T26P/DQ4T

B2

IO_8A/DIFFIO_RX_T25N

H7

IO_8A/DIFFIO_TX_T26N/DQ4T

B1

IO_8A/DIFFIO_RX_T27P/DQ4T

B6

IO_8A/DIFFIO_TX_T28P/DQ4T

C3

IO_8A/DIFFIO_RX_T27N/DQ4T

B5

IO_8A/DIFFIO_TX_T28N/DQ4T

B3

IO_8A/DIFFIO_RX_T29P/DQS4T

K12

IO_8A/DIFFIO_TX_T30P

D2

IO_8A/DIFFIO_RX_T29N/DQSN4T

J12

IO_8A/DIFFIO_TX_T30N/DQ4T

C2

IO_8A/DIFFIO_RX_T31P/DQ4T

G12

IO_8A/DIFFIO_TX_T32P/DQ4T

E4

IO_8A/DIFFIO_RX_T31N/DQ4T

G11

IO_8A/DIFFIO_TX_T32N

D4

IO_8A/DIFFIO_RX_T33P

K7

IO_8A/DIFFIO_TX_T34P/DQ5T

E3

IO_8A/DIFFIO_RX_T33N

K8

IO_8A/DIFFIO_TX_T34N/DQ5T

E2

IO_8A/DIFFIO_RX_T35P/DQ5T

G10

IO_8A/DIFFIO_TX_T36P/DQ5T

E1

IO_8A/DIFFIO_RX_T35N/DQ5T

F10

IO_8A/DIFFIO_TX_T36N/DQ5T

D1

IO_8A/DIFFIO_RX_T37P/DQS5T

J10

IO_8A/DIFFIO_TX_T38P

E7

IO_8A/DIFFIO_RX_T37N/DQSN5T

J9

IO_8A/DIFFIO_TX_T38N/DQ5T

E6

IO_8A/DIFFIO_RX_T39P/DQ5T

F9

IO_8A/DIFFIO_TX_T40P/DQ5T

G7

IO_8A/DIFFIO_RX_T39N/DQ5T

F8

IO_8A/DIFFIO_TX_T40N

F6

R98 10K DNI

1

ON

SW16

SW-DIP12

DNI

1

2

3

4

12

11

10

9

8

7

5

6

R100 1K

R103 1K

R105 1K

R106 10K

R109 1KDNI

R237 4.7K

R111 1KDNI

剩余29页未读,继续阅读

资源评论

rxjrlsq2016-07-27还是不错的,但后来没有用到。等大陆流行起来吧

rxjrlsq2016-07-27还是不错的,但后来没有用到。等大陆流行起来吧 GNSS792018-02-03很好资源可以确定适合方向。

GNSS792018-02-03很好资源可以确定适合方向。 fengshuxian7692019-05-14很全面,很好用,谢谢分享.

fengshuxian7692019-05-14很全面,很好用,谢谢分享. 徐中元2015-09-02全英文看不懂

徐中元2015-09-02全英文看不懂

tbw2_163_com

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功