没有合适的资源?快使用搜索试试~ 我知道了~

MT6750芯片规格书,MT6750 datdahseet资料下载

需积分: 40 12 下载量 81 浏览量

2018-08-07

10:49:23

上传

评论 1

收藏 9.37MB PDF 举报

温馨提示

MT6750 MT6750单芯片是联发科技支持LTE Cat-6技术的中端产品,以八核心的强大运算能力执行新一代的调制解调技术,支持各 式主流的IP多媒体子系统(IMS),包含 VoLTE、ViLTE、VoWiFi、RCS ,以优异性能提升界面显示效果、多媒体内容与拍照 体验等等,大大满足用户需求。MT6750是Cortex-A53八核心处理器(最高主频1.5GHz),搭载Mali T860双图像处理器(最高 频率650MHz),支持最高4G运存和1600w像素摄像头

资源推荐

资源详情

资源评论

loginid=yszzw118@droi.com,time=2016-03-29 23:49:23,ip=124.74.128.198,doctitle=MT6750 LTE-A Smartphone Application Processor Functional Specification V1.3.pdf,company=DROI_WCX

© 2016 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Version: 1.3

Release date: 2016-02-15

Specifications are subject to change without notice.

MT6750 LTE-A Smartphone Application

Processor Functional Specification

M

loginid=yszzw118@droi.com,time=2016-03-29 23:49:23,ip=124.74.128.198,doctitle=MT6750 LTE-A Smartphone Application Processor Functional Specification V1.3.pdf,company=DROI_WCX

MT6750

LTE-A Smartphone Application Processor

Functional Specification

Confidential A

MediaTek Confidential © 2016 MediaTek Inc.

Page 2 of 225

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

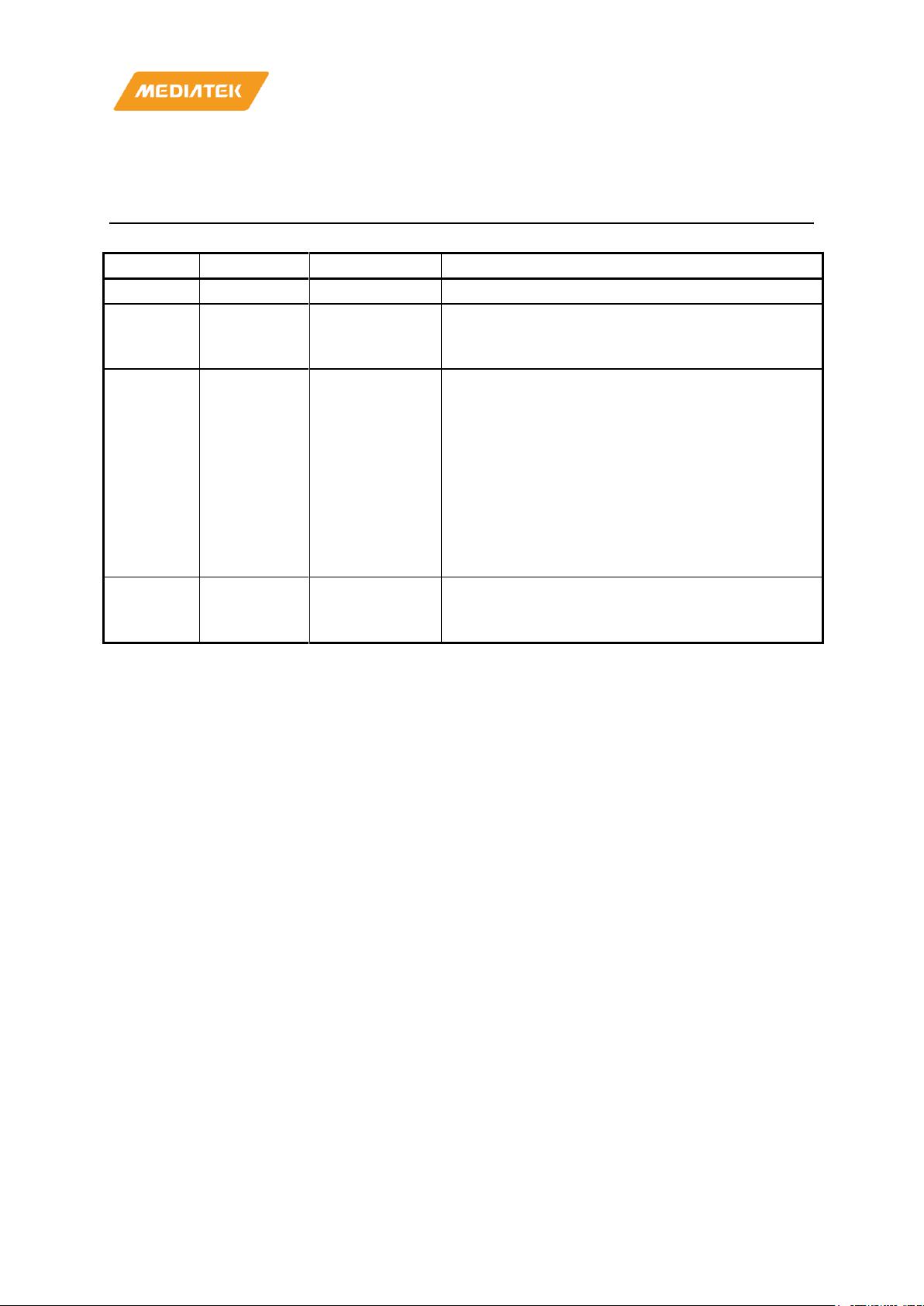

Document Revision History

Revision Date Author Description

1.0 2015-11-17 Gene Yeh First release

1.1 2015-12-09 WX Lin, CJ Jan

1. Updated ISP specification.

2. Updated pin description.

3. Updated EINT table.

1.2 2015-12-30 CJ Jan

1. Updated system configuration.

2. Updated POD logo.

3. Updated top marking.

4. Updated PDN table.

5. Updated power-on sequence.

6. Removed USB3.0 feature.

7. Updated image size of video snapshot.

8. Updated EMI bus clock frequency.

9. Updated GPU triangle rate and shader rate.

10. Updated MCU system bus frequency.

1.3 2016-02-15 CJ Jan

1. Modified pin description in Table 2-1, Table 2-3.

2. Modified Table 2-37 PDN specifications.

3. Added chapter 5.5 USB.

loginid=yszzw118@droi.com,time=2016-03-29 23:49:23,ip=124.74.128.198,doctitle=MT6750 LTE-A Smartphone Application Processor Functional Specification V1.3.pdf,company=DROI_WCX

MT6750

LTE-A Smartphone Application Processor

Functional Specification

Confidential A

MediaTek Confidential © 2016 MediaTek Inc.

Page 3 of 225

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

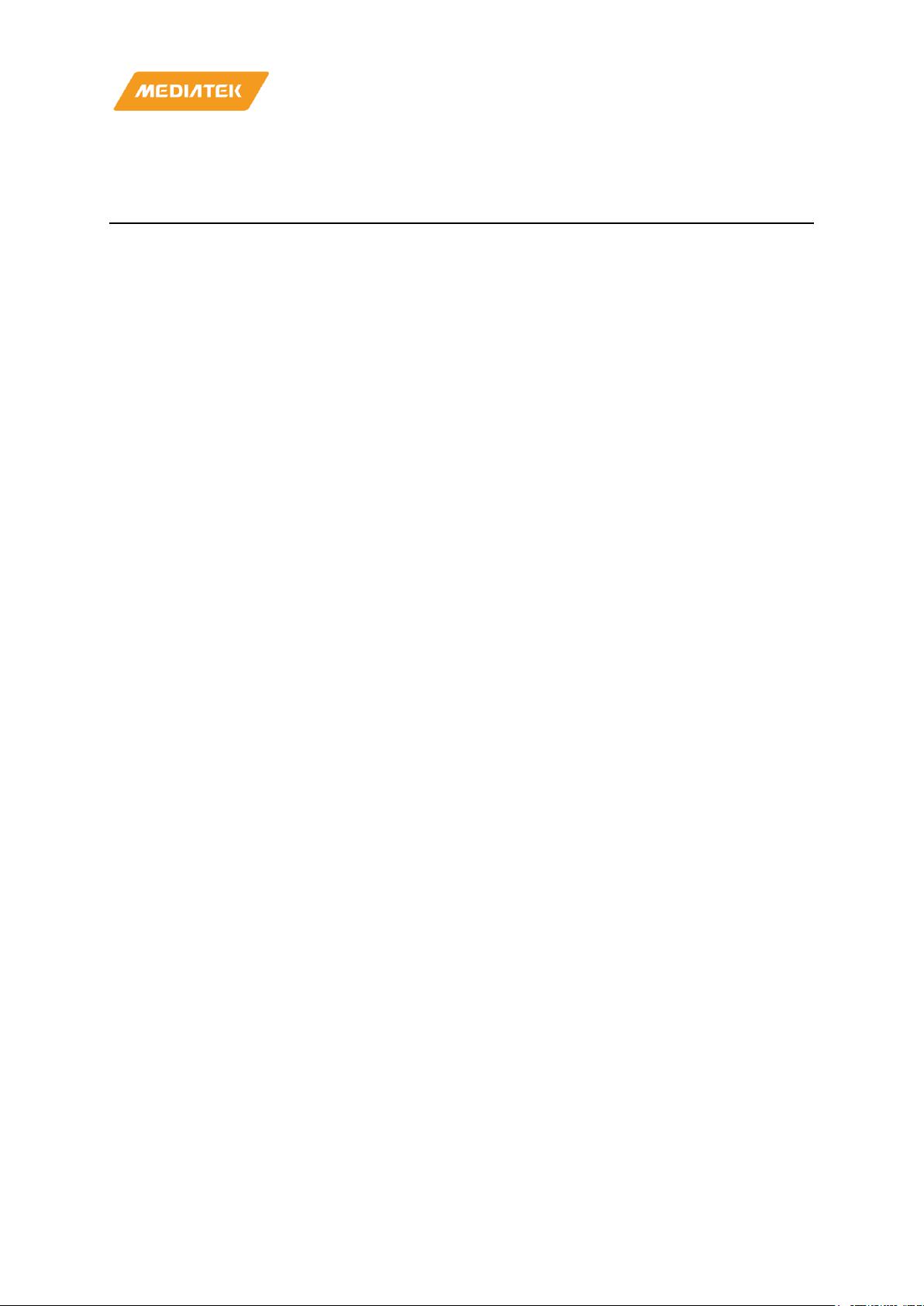

Table of Contents

Document Revision History ............................................................................................. 2

Table of Contents .............................................................................................................. 3

Preface ........................................................................................................................... 10

1 System Overview ..................................................................................................... 11

1.1 Highlighted Features Integrated in MT6750.......................................................................... 11

1.2 Platform Features ..................................................................................................................... 13

1.3 Modem Features ...................................................................................................................... 15

1.4 Connectivity Features .............................................................................................................. 17

1.5 Multimedia Features ................................................................................................................ 19

1.6 General Description ................................................................................................................. 21

2 Product Description ............................................................................................... 23

2.1 Pin Description ........................................................................................................................ 23

2.2 Electrical Characteristic .......................................................................................................... 40

2.3 System Configuration .............................................................................................................. 61

2.4 Power-on Sequence ................................................................................................................. 62

2.5 Analog Baseband ..................................................................................................................... 63

2.6 Package Information ................................................................................................................ 72

2.7 Power Delivery Network .......................................................................................................... 74

2.8 Ordering Information .............................................................................................................. 75

3 MCU and Bus Fabric .............................................................................................. 76

3.1 MCU System ............................................................................................................................. 76

3.2 On-chip Memory Controller ................................................................................................... 85

3.3 External Interrupt Controller ................................................................................................. 88

3.4 System Interrupt Controller .................................................................................................... 91

3.5 Infrastructure System Configuration Module ....................................................................... 95

3.6 External Memory Interface ..................................................................................................... 97

3.7 DRAM Controller .................................................................................................................... 99

3.8 AP_DMA .................................................................................................................................104

3.9 CQ_DMA ................................................................................................................................109

4 Clock and Power Control ...................................................................................... 111

4.1 Top Clock Generator ............................................................................................................... 111

4.2 Top Reset Generator Unit ...................................................................................................... 117

4.3 PMIC Wrapper .......................................................................................................................120

4.4 Frequency Hopping Controller ............................................................................................. 122

5 Peripherals .......................................................................................................... 123

5.1 Pericfg Controller ................................................................................................................... 123

5.2 GPIO Control .......................................................................................................................... 125

5.3 Keypad Scanner ...................................................................................................................... 132

5.4 UART ...................................................................................................................................... 136

5.5 USB ......................................................................................................................................... 139

5.6 USB 2.0 High Speed Dual-Role Controller ........................................................................... 142

5.7 USBPHY Register File ............................................................................................................ 147

loginid=yszzw118@droi.com,time=2016-03-29 23:49:23,ip=124.74.128.198,doctitle=MT6750 LTE-A Smartphone Application Processor Functional Specification V1.3.pdf,company=DROI_WCX

MT6750

LTE-A Smartphone Application Processor

Functional Specification

Confidential A

MediaTek Confidential © 2016 MediaTek Inc.

Page 4 of 225

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

5.8 SPI Interface Controller ......................................................................................................... 150

5.9 Memory Stick and SD card Controller .................................................................................. 154

5.10 AUXADC .................................................................................................................................160

5.11 I2C/SCCB Controller ............................................................................................................. 163

5.12 Pulse-Width Modulation (PWM) .......................................................................................... 168

5.13 General-Purpose Timer (GPT) .............................................................................................. 170

5.14 Thermal Controller ................................................................................................................ 172

5.15 IRTX ........................................................................................................................................ 179

5.16 Audio System .......................................................................................................................... 183

5.17 BTIF ........................................................................................................................................ 186

6 Multimedia .......................................................................................................... 189

6.1 Display Controller .................................................................................................................. 189

6.2 CAM ........................................................................................................................................ 191

6.3 SENINF_TOP (Sensor Interface).......................................................................................... 192

6.4 FDVT ....................................................................................................................................... 193

6.5 DISPLAY PWM Generator.................................................................................................... 200

6.6 DPI (Digital Parallel Interface) .............................................................................................201

6.7 Display Serial Interface ......................................................................................................... 202

6.8 JPEG Encoder ....................................................................................................................... 203

6.9 JPEG Decoder ....................................................................................................................... 206

6.10 Video Decoder ........................................................................................................................ 211

6.11 H.264 Video Encoder ............................................................................................................. 219

6.12 MFG ........................................................................................................................................ 221

7 Analog Baseband.................................................................................................. 223

7.1 AP Mixedsys .......................................................................................................................... 223

loginid=yszzw118@droi.com,time=2016-03-29 23:49:23,ip=124.74.128.198,doctitle=MT6750 LTE-A Smartphone Application Processor Functional Specification V1.3.pdf,company=DROI_WCX

MT6750

LTE-A Smartphone Application Processor

Functional Specification

Confidential A

MediaTek Confidential © 2016 MediaTek Inc.

Page 5 of 225

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

Lists of Figures

Figure 1-1. High-level MT6750 functional block diagram ......................................................................... 12

Figure 1-2. Block diagram of MT6750 ........................................................................................................ 21

Figure 1-3. Bus structure of MT6750 ......................................................................................................... 22

Figure 2-1. Ball map view ........................................................................................................................... 23

Figure 2-2. Basic timing parameter for LPDDR3 commands .................................................................. 45

Figure 2-3. Basic timing parameter for LPDDR3 write ............................................................................ 46

Figure 2-4. Basic LPDDR3 read timing parameter .................................................................................. 46

Figure 2-5. SPI timing diagram ................................................................................................................. 48

Figure 2-6. I2S master mode timing diagram ........................................................................................... 49

Figure 2-7. I2C timing diagram of standard mode (100kHz) and fast mode (400kHz) ........................ 50

Figure 2-8. MSDC input timing diagram of default speed ........................................................................ 51

Figure 2-9. MSDC output timing diagram of default speed ...................................................................... 51

Figure 2-10. MSDC input timing diagram of high speed ......................................................................... 52

Figure 2-11. MSDC output timing diagram of high speed ........................................................................ 52

Figure 2-12. MSDC clock timing diagram of SDR12/SDR25/SDR50/SDR104 mode ............................ 53

Figure 2-13. MSDC input timing diagram of SDR50/SDR104 mode ...................................................... 53

Figure 2-14. MSDC output timing diagram of fixed data window (SDR12/SDR25/SDR50) ................ 54

Figure 2-15. MSDC output timing diagram of variable window (SDR104) ............................................. 54

Figure 2-16. MSDC clock timing diagram of DDR50 speed mode. .......................................................... 55

Figure 2-17. MSDC input/output timing diagram of DDR50 speed mode .............................................. 55

Figure 2-18. MSDC clock timing diagram of HS200 ................................................................................ 56

Figure 2-19. MSDC input timing diagram of HS200................................................................................ 56

Figure 2-20. MSDC output timing diagram of HS200 .............................................................................. 57

Figure 2-21. MSDC input timing diagram of HS400 ................................................................................ 58

Figure 2-22. MSDC output timing diagram of HS400 ............................................................................. 58

Figure 2-23. Power on sequence ................................................................................................................ 62

Figure 2-24. Block diagram of BBRX-ADC ............................................................................................... 64

Figure 2-25. Block diagram of BBTX ......................................................................................................... 65

Figure 2-26. Block diagram of ETDAC ...................................................................................................... 66

Figure 2-27. Block diagram of DETADC ....................................................................................................67

Figure 2-28. Block diagram of APC-DAC .................................................................................................. 68

Figure 2-29. Outlines and dimensions of TFBGA 13mm*13.4mm, 873-ball, 0.4mm pitch package ..... 72

Figure 2-30. Top marking of MT6750 ........................................................................................................ 75

Figure 3-1. Block diagram of on-chip memory controller ........................................................................ 85

Figure 3-2. Security memory protection scheme ...................................................................................... 86

Figure 3-3. Block diagram of external interrupt controller ..................................................................... 88

Figure 3-4. System level block diagram of system interrupt controller ................................................... 91

Figure 3-5. Block diagram of system interrupt controller ........................................................................ 92

Figure 3-6. DCM in action .......................................................................................................................... 95

Figure 3-7. EMI/DRAM controller top connection .................................................................................. 98

Figure 3-8. Block diagram of DRAM controller ...................................................................................... 102

Figure 3-9. APDMA block diagram .......................................................................................................... 105

Figure 4-1. Block diagram of clock architecture ....................................................................................... 111

Figure 4-2. Example of clock multiplier ................................................................................................... 112

Figure 4-3. PLL block diagram ................................................................................................................. 113

Figure 4-4. TOPCKGEN FMETER structure ........................................................................................... 115

Figure 4-5. Block diagram of top reset generation unit .......................................................................... 117

MediaTek Confiden tial A

剩余224页未读,继续阅读

资源评论

szx940213

- 粉丝: 727

- 资源: 49

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- ssm-vue-高校实验室管理系统-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- Java源码ssm+vue框架百色学院创新实践学分认定系统-毕业设计-期末大作业.zip

- Java源码ssm+vue框架宝康药房销售管理系统-毕业设计-期末大作业.zip

- Java源码ssm+vue框架包头市交通管理局路况查询系统-毕业设计-期末大作业.zip

- 基于小程序的新生自助报到系统源码(小程序毕业设计完整源码+LW).zip

- ssm-vue-海鲜自助餐厅系统-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- ssm-vue-个人博客网站-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- Java源码ssm+vue框架本科生毕业设计选题系统-毕业设计-期末大作业.zip

- Java源码ssm+vue框架毕业生就业信息统计系统+vue-毕业设计-期末大作业.zip

- Java源码ssm+vue框架编程类在线答题系统-毕业设计-期末大作业.zip

- 基于小程序的智能停车场管理系统源码(小程序毕业设计完整源码+LW).zip

- ssm-vue-理发店会员管理系统-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- ssm-vue-绿色农产品推广应用网站-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- ssm-vue-鲸落文化线上体验馆-源码工程-29页从零开始全套图文详解-34页参考论文-27页参考答辩ppt-全套开发环境工具、文档模板、电子教程、视频教学资源分享.zip

- Java源码ssm+vue框架超市场管理系统-毕业设计-期末大作业.zip

- Java源码ssm+vue框架大美新疆论坛交流系统-毕业设计-期末大作业.zip

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功