IP210T

Data Sheet

2 / 69

December 19, 2008

Copyright © 2007, IC Plus Corp. IP210T-DS-R01

Table of Contents

Features .................................................................................................................................................................................1

General Description .............................................................................................................................................................. 1

Table of Contents ..................................................................................................................................................................2

Revision History..................................................................................................................................................................... 4

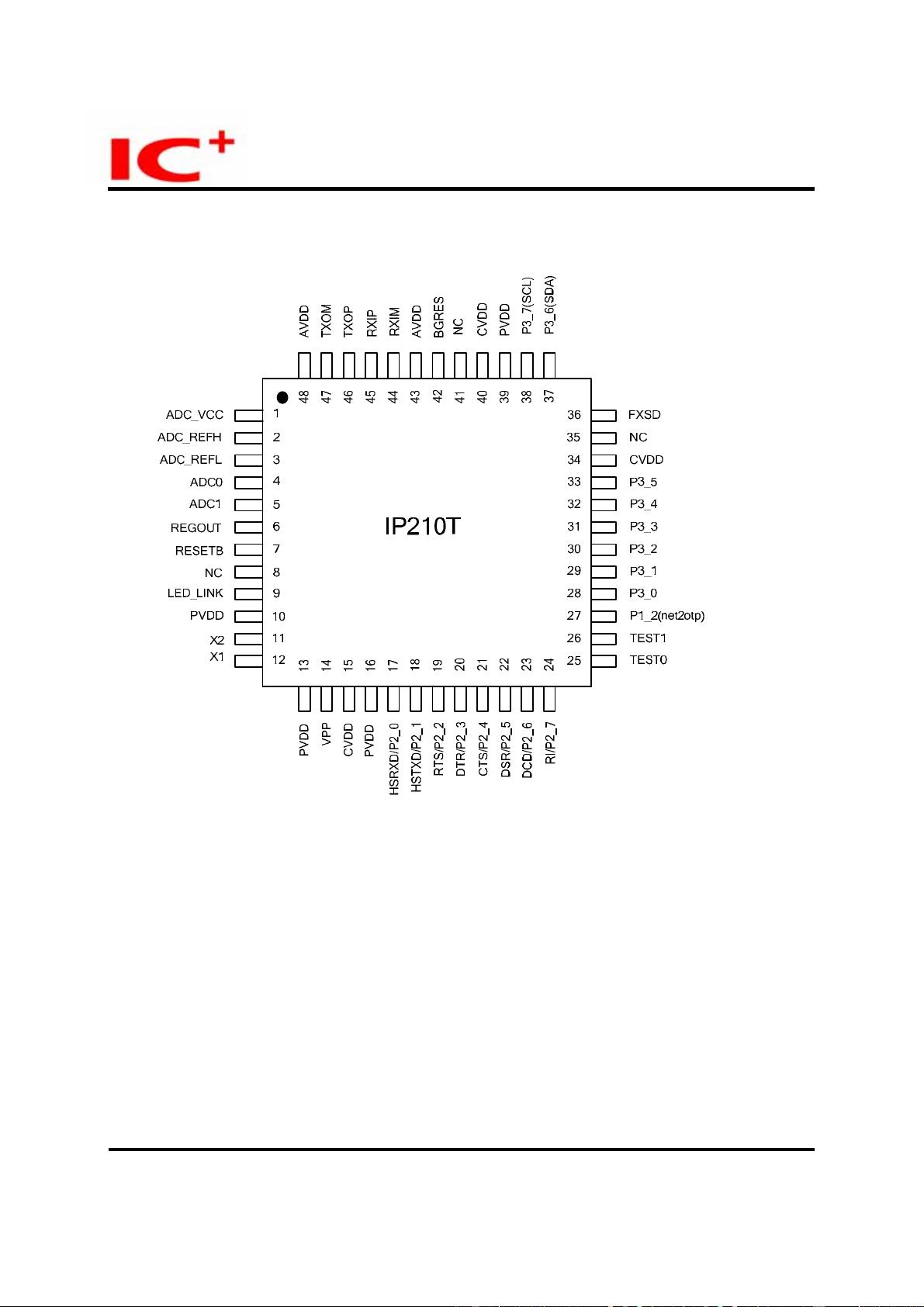

1 Pin Diagram................................................................................................................................................................... 5

2 Block Diagram............................................................................................................................................................... 6

3 Pin Description..............................................................................................................................................................7

4 Function Description...................................................................................................................................................10

4.1 CPU ......................................................................................................................................10

4.1.1 Memory organization...............................................................................................10

4.1.2 SFR MAP and Default Value ................................................................................... 11

4.1.3 Bit Addressable Registers’ Bit definition.................................................................. 11

4.1.4 Non Bit Addressable Registers’ Bit definition ..........................................................12

4.1.5 Register Description (Non 8051 standard registers) ...............................................12

4.1.6 Register description (8051 standard registers) .......................................................13

4.1.7 CPU Interrupt...........................................................................................................15

4.1.8 CPU Timers/Counters..............................................................................................16

4.1.8.1 Timer0............................................................................................................16

4.1.8.2 Timer1............................................................................................................16

4.1.8.3 Timer2............................................................................................................16

4.1.9 CPU Mirror Mode.....................................................................................................18

4.1.9.1 Purpose..........................................................................................................18

4.1.9.2 Action.............................................................................................................18

4.1.10 Power Management ................................................................................................18

4.1.10.1 Idle Mode .......................................................................................................18

4.1.10.2 Power Down Mode ........................................................................................18

4.1.11 Watch Dog Timers ...................................................................................................18

4.1.11.1 Watch Dog Timer 1, WDT..............................................................................18

4.1.11.2 Watch Dog Timer 2, HWWDT........................................................................19

4.2 DMA......................................................................................................................................20

4.2.1 Internal memory to internal memory........................................................................20

4.2.1.1 Purpose..........................................................................................................20

4.2.1.2 Action.............................................................................................................20

4.2.2 OTP to internal memory ..........................................................................................20

4.2.2.1 Purpose..........................................................................................................20

4.2.2.2 Action.............................................................................................................20

4.3 Timer/Counter.......................................................................................................................22

4.3.1 Purpose ...................................................................................................................22

4.3.2 Initialize real-time counter........................................................................................22

4.3.3 Read real-time counter............................................................................................22

4.3.4 Timer/Counter overflow ...........................................................................................22

4.4 MAC......................................................................................................................................23

4.4.1 TX MAC ...................................................................................................................23

4.4.1.1 TX descriptor registers...................................................................................23

4.4.1.2 IP Checksum and CRC32 calculation for a proprietary packet .....................24

4.4.2 RX buffer..................................................................................................................24

4.4.2.1 RX Filter.........................................................................................................24

4.5 EEPROM I/F.........................................................................................................................25

4.5.1 Configuration ...........................................................................................................25

4.5.1.1 Access through P3[7:6]..................................................................................25

4.5.1.2 Supported EEPROM types............................................................................25

4.5.2 Related Registers....................................................................................................25

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功