没有合适的资源?快使用搜索试试~ 我知道了~

Biss转码芯片MB4资料Ic-Haus

温馨提示

试读

40页

Biss转码芯片,将Biss信号转换成并行数据或者I2C数据。Ic-Haus是德国芯片公司,购买需要找国内代理公司。

资源推荐

资源详情

资源评论

preliminary preliminary

iC-MB4

BiSS INTERFACE MASTER

Rev A1, Page 1/40

FEATURES

♦ Bidirectional BiSS communication with up to 8 slaves

♦ Supports SSI protocol for unidirectional data transmission

♦ Synchronous sensor data acquisition with cyclic transfer at

data rates of up to 10 Mbit/s

♦ Configurable interface with TTL, CMOS, RS422 or LVDS

♦ Slave register operations during cyclic data transfers

♦ Automatic compensation of line delays and conversion times

♦ Data lengths of up to 64 bit for sensor data,

configurable for each slave

♦ Data verification by CRC polynomials of up to 16 bits per slave

♦ Separate memory banks enable free controller access during

BiSS sensor data transfers

♦ 64 bytes memory for bidirectional slave register

communication

♦ Parallel interface with 8 bit data/address bus services Intel and

Motorola devices with combined data and address bus

♦ Serial controller communication by SPI

TM

-compatible mode

♦ Single 3 V to 5 V supply, industrial temperature range

APPLICATIONS

♦ Bidirectional communication in

multi sensor systems

♦ Linear and rotary encoders

♦ Motor feedback systems

♦ PLC systems

♦ Drives

PACKAGES

TSSOP24 QFN28

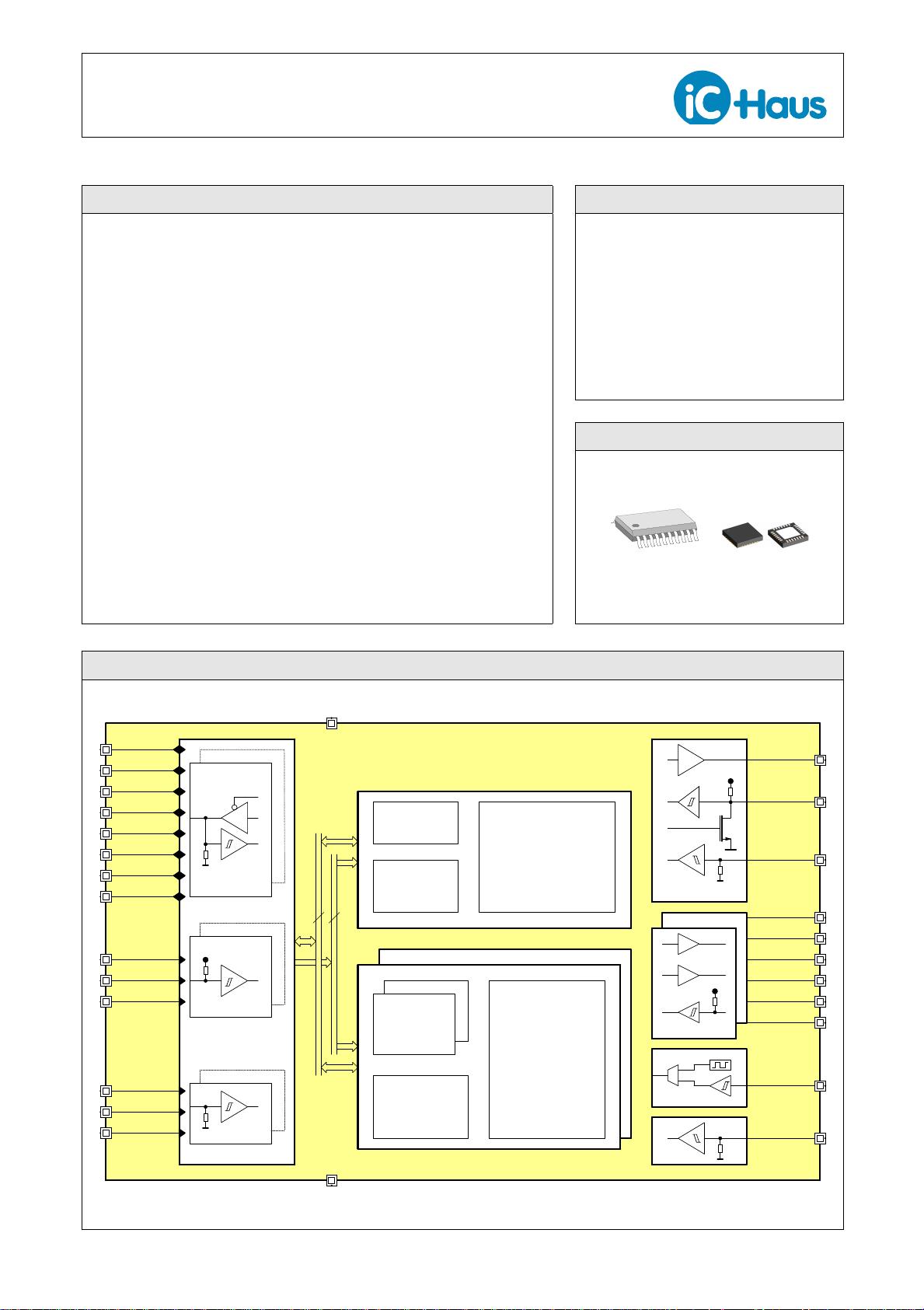

BLOCK DIAGRAM

VDD

PROCESS DATA

OSCILLATOR

HOST INTERFACE RESET

CTRL PORTS

BANK 1

BiSS INTERFACE

VDD

VDD

INSTANCE 1

BANK 2

sample CDS

measure busy

FRAME CONTROLLER

send busy

request sensor data

send acknowledge

DATA BUS

ADDRESS BUS

8 8

CHANNEL 1

iC-MB4

analyse wire delay

INSTANCE 2

CHANNEL 2

16 BYTE RAM

PARAMETER

CONTROL

CONFIG

PROCESS

4 x 32 BIT RAM

DATA

DATA

PROCESS

4 x 64 BIT RAM

CONTROLLER

calculate actuator crc

send actuator data

receive sensor data

check sensor data

64 BYTE RAM

send start

calculate control frame

send CDM

GND

NCS

MO1

DB7

INT_NMOT

SL2_NSL1

MO2_NMO1

DB5

NRES

DB6

CLK

VDD

NWR_E

DB4

EOT

NER

GETSENS

DB2

DB1

DB0

NRD_RNW

CFGSPI

DB3

ALE

MA2_NMA1

MA1

SL1

Copyright © 2014 iC-Haus http://www.ichaus.com

preliminary preliminary

iC-MB4

BiSS INTERFACE MASTER

Rev A1, Page 2/40

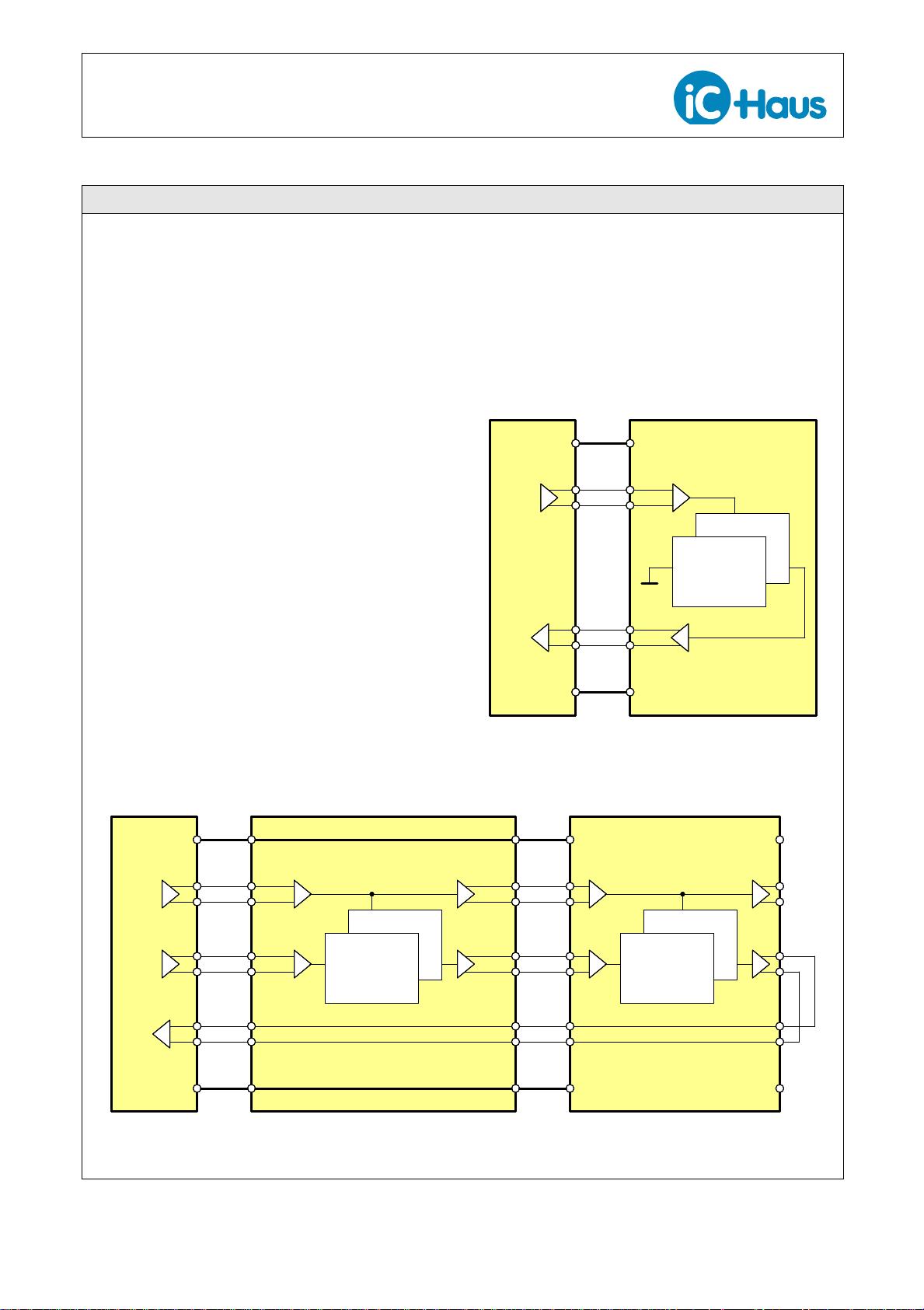

DESCRIPTION

iC-MB4 is a single-chip BiSS/SSI interface master

controller featuring an 8 bit bus interface to industrial

standard microcontrollers. Alternatively an SPI inter-

face enables serial communication between iC-MB4

and the connected microcontroller. Up to 8 BiSS

slaves can be accessed. The BiSS devices are con-

nected to clock line MA1 and data return line SL1

using RS422 transceivers (Figure 2). The BiSS de-

vices can be connected directly in noise-free environ-

ments. A maximum of 8 BiSS slaves is supported,

each with their own configurable data sections cov-

ering:

1. Sensor data from 0 to 64 bit

(for measurement data, flags like alarm and

warning, life cycle counter, . . . )

2. Register data with 128 bytes per slave ID

(e.g. for device parameters)

iC-MB4 provides two RAM memory banks for each

slave, enabling parallel access of the microcontroller

while new sensor data is being read in. A 64 byte

memory supports register transfers. Sensor data ac-

quisition is started by a microcontroller command or

via pin GETSENS. Alternatively, iC-MB4 can also

read in new sensor data automatically; the cycle

time in this instance can be set as required. The

end of sensor data acquisition and reading is sig-

naled at pin EOT by a high; if faults occur dur-

ing transmission pin NER signals a low. Errors

in communication can be verified by the microcon-

troller via a status register; a system error message

can also enter this register if bidirectional message

pin NER is kept low by external intervention. iC-

MB4 generates a clock signal for sensor commu-

nication using an internal 20 MHz oscillator. The

clock can also be supplied externally. iC-MB4 is

based on the BiSS master IP family MB100_X.

controldata

Device 1 (Sensor)Master

clock/

Last Slave

controldata

ID 1..N-1

ID 0

sensordata/

MA+

MA-

SL-

V-

V+

SL+

MA-

MA+

SLO-

SLO+

Figure 1: Point-to-point connection of iC-MB4 to

one device with several slaves

controldata

actuatordata

ID N

ID N+1..M-1

Last Slave

ID 0

ID 1..N-1

Device 2 (Sensor/Actuator) Device 1 (Sensor/Actuator)Master

clock/

controldata

sensordata/

MA-

MA+

V-

V+

SLI+

SLI-

MA+

MA-

SL+

SL-

SL-

SL+

MO+

MO-

MAO-

MAO+

SLO+

SLO-

SLR-

MO-

MO+

V-

V+

MA+

MA-

SL+

SL-

SLR+

Figure 2: Example network of iC-MB4 and two devices

preliminary preliminary

iC-MB4

BiSS INTERFACE MASTER

Rev A1, Page 3/40

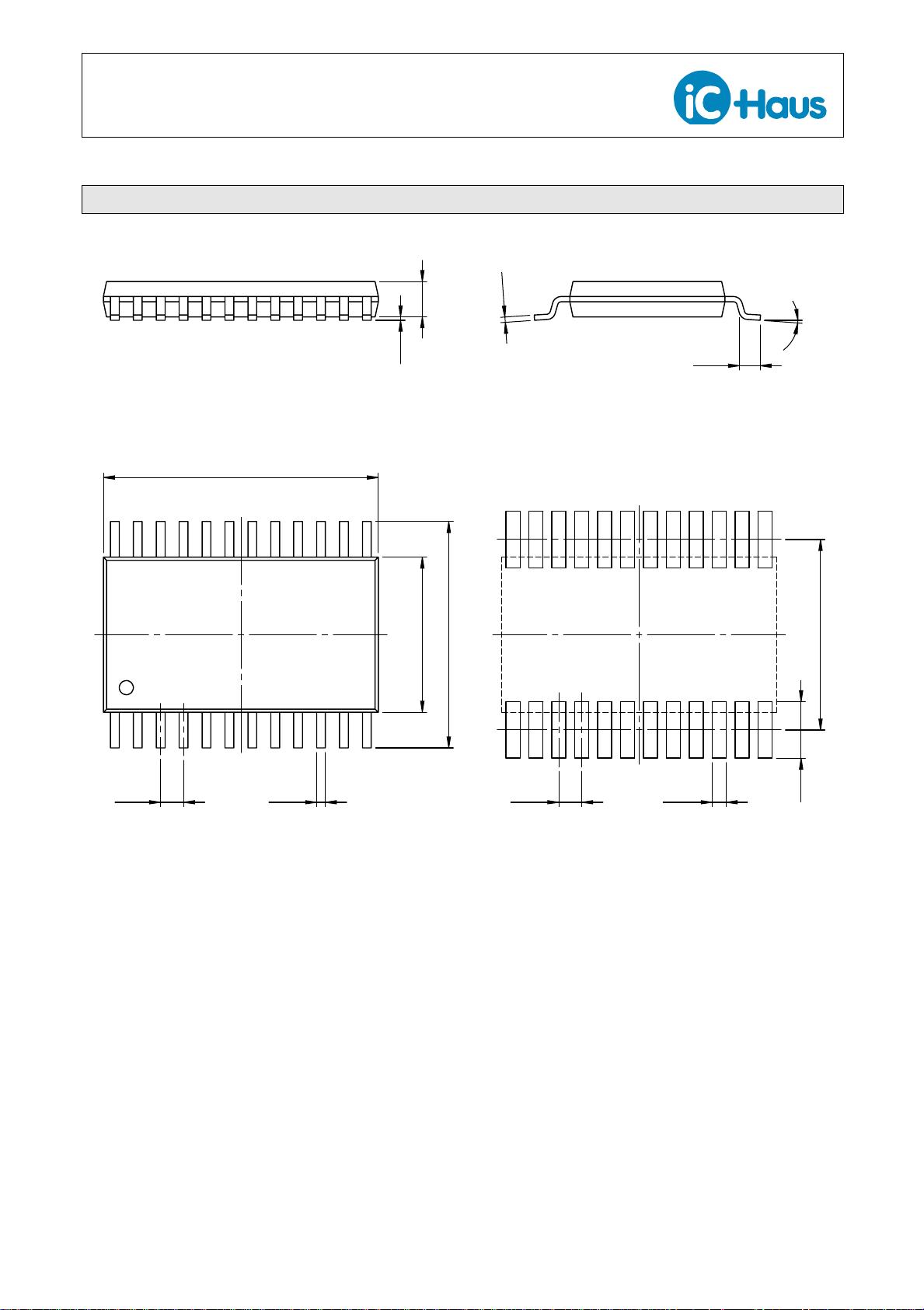

PACKAGING INFORMATION TO JEDEC

PIN CONFIGURATION TSSOP24

(topview)

PIN FUNCTIONS

No. Name Function

SPI Communication Mode

(CFGSI = 1)

1 NCS SPI Chip Select Input, active low

2 ALE SPI Clock Input

3 DB0 SPI Serial Data Input

4 DB1 SPI Serial Data Output

7 DB4 SPI2 Chip Select Input, active low

8 DB5 SPI2 Clock Input

9 DB6 SPI2 Serial Data Input

10 DB7 SPI2 Serial Data Output

Data Bus Communication Mode

(CFGSPI = 0)

1 NCS Chip Select Input, active low

2 ALE Address Latch Enable Input

3 DB0 Data Bus Input/Output

4 DB1 Data Bus Input/Output

5 DB2 Data Bus Input/Output

6 DB3 Data Bus Input/Output

7 DB4 Data Bus Input/Output

8 DB5 Data Bus Input/Output

9 DB6 Data Bus Input/Output

10 DB7 Data Bus Input/Output

11 GND Ground

12 VDD +3 V . . . +5.5 V Supply Voltage

13 EOT End of transmission Output

14 GETSENS Sensor Data Request Input

15 NER Error Message Input/Output,

low active

16 MA1 BiSS Clock Line Output

17 SL1 BiSS Data Line Input

18 INT_NMOT Communication Mode Select Input

(Intel = 1, Motorola = 0)

19 CFGSPI Serial/Parallel Mode Select Input

(serial SPI = 1, parallel = 0)

20 NRES Reset Input, low active

21 CLK External Clock Input

22 MO1 BiSS Data Line Output

Intel Mode (INT_NMOT = 1)

23 NWR_E Write Input, active low

24 NRD_RNW Read Input, active low

Motorola Mode (INT_NMOT = 0)

23 NWR_E Enable Input, active high

24 NRD_RNW Read/Not-Write Select Input

preliminary preliminary

iC-MB4

BiSS INTERFACE MASTER

Rev A1, Page 4/40

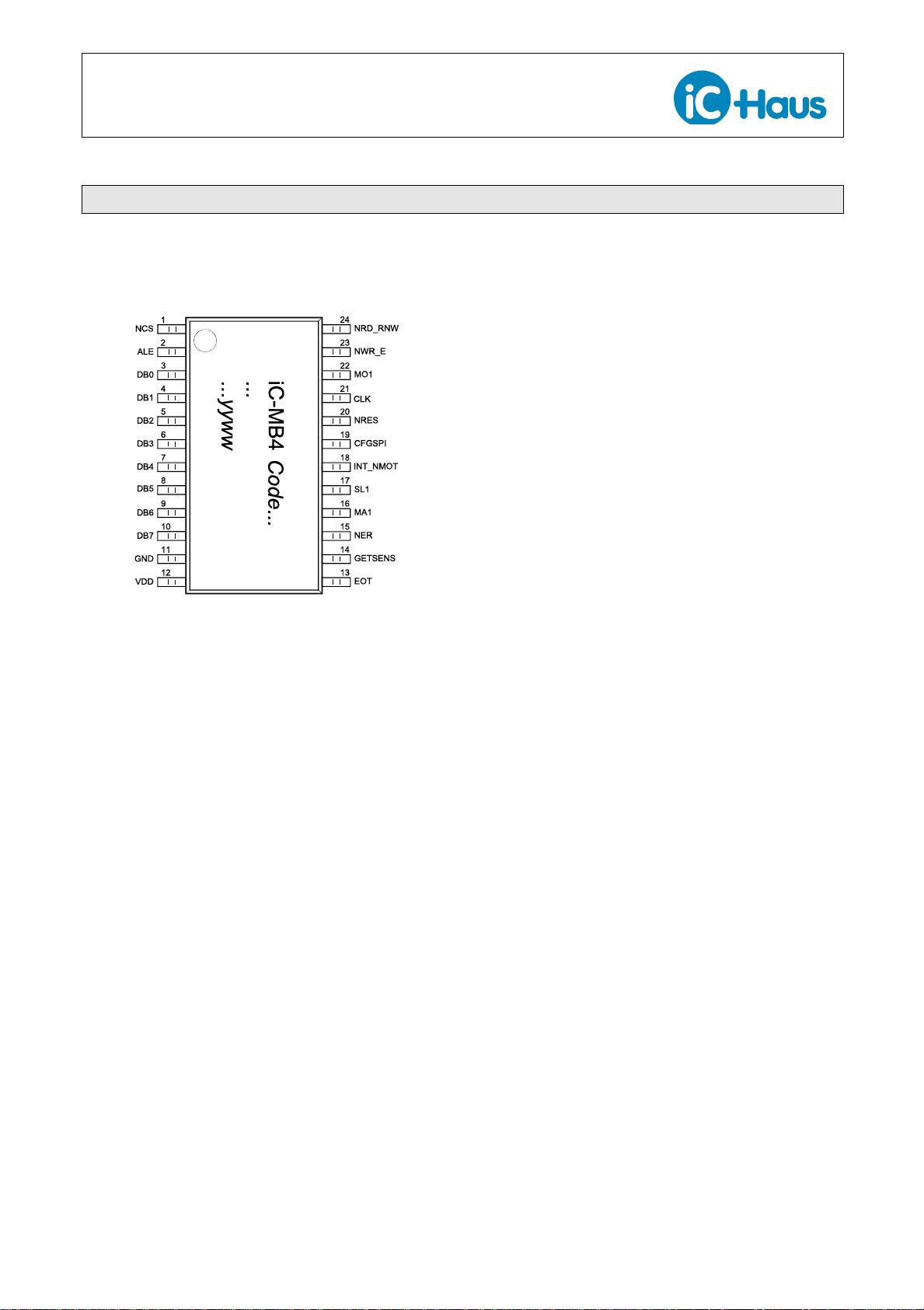

PIN CONFIGURATION QFN28 5mm x 5 mm

(topview)

...

...yyww

iC−MB4

15

16

17

18

19

20

21

232425262728 22

1

2

3

4

5

6

7

8 9 10 11 12 13 14

PIN FUNCTIONS

No. Name Function

SPI Communication Mode

(CFGSI = 1)

27 NCS SPI Chip Select Input, active low

28 ALE SPI Clock Input

1 DB0 SPI Serial Data Input

2 DB1 SPI Serial Data Output

5 DB4 SPI2 Chip Select Input, active low

6 DB5 SPI2 Clock Input

7 DB6 SPI2 Serial Data Input

8 DB7 SPI2 Serial Data Output

Data Bus Communication Mode

(CFGSPI = 0)

1 DB0 Data Bus Input/Output

2 DB1 Data Bus Input/Output

3 DB2 Data Bus Input/Output

4 DB3 Data Bus Input/Output

5 DB4 Data Bus Input/Output

6 DB5 Data Bus Input/Output

7 DB6 Data Bus Input/Output

8 DB7 Data Bus Input/Output

9 GND Ground

10 VDD +3 V . . . +5.5 V Supply Voltage

11 EOT End of transmission Output

12 GETSENS Sensor Data Request Input

13 NER Error Message Input/Output,

low active

14 n.c. not connected

15 MA1 BiSS Clock Line Output

16 MA2_NMA1 BiSS Clock Line Output Channel

2

17 SL1 BiSS Data Line Input

18 SL2_NSL1 BiSS Data Line Input Channel 2

19 INT_NMOT Communication Mode Select In-

put

(Intel = 1, Motorola = 0)

20 CFGSPI Serial/Parallel Mode Select Input

(serial SPI = 1, parallel = 0)

21 NRES Reset Input, low active

22 CLK External Clock Input

23 MO1 BiSS Data Line Output

24 MO2_NMO1 BiSS Data Line Output Channel 2

25 NWR_E Read Input, active low (Intel)

Read/Not-Write Select Input

(Motorola)

26 NRD_RNW Write Input, active low (Intel)

Enable Input, active high (Mo-

torola)

27 NCS Chip Select Input, active low

28 ALE Address Latch Enable Input

TP Thermal Pad (GND)

The Thermal Pad must be connected to GND.

剩余39页未读,继续阅读

资源评论

boilingcity_12014-10-06ic-mb4 datasheet,很有用,感谢分享

boilingcity_12014-10-06ic-mb4 datasheet,很有用,感谢分享

sxrenren2006

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功