没有合适的资源?快使用搜索试试~ 我知道了~

数字逻辑电路课程设计_4bit模9加法器_VHDL实现(含完整.docx

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 12 浏览量

2023-02-03

18:03:43

上传

评论

收藏 1.26MB DOCX 举报

温馨提示

试读

66页

数字逻辑电路课程设计_4bit模9加法器_VHDL实现(含完整.docx

资源推荐

资源详情

资源评论

电 子 科 技 大 学

UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA

数字逻辑设计

实验报告

实验题目: 4bit 模 9 加法器

学生姓名:

指导老师:

一、实验内容

设计一个 4bit 模 9 加法器。输入为两个 4bit 的二进制数,输出为两数相加

后模 9 的结果。其数学表达式为:y=(x1+x2)mod 9。

二、实验要求

1、功能性要求:

能够实现 4bit 无符号数的模 9 加法运算,即输入两个 4 比特数据时能够正确

输出其相加并模 9 运算结果。

2、算法要求:

模加法器有多种算法,可采用任意算法进行设计。

3、设计性要求:

采用全加器、半加器和基本门结构化描述。能够编写 Test Bench 文件,并利

用 Modelsim 进行仿真。在 Modelsim 仿真正确的基础上,能够生成 bit 文件并上

板验证其正确性。

4、基本上板要求:

在上板实验时,输入的两个 4bit 数采用拨码开关输入,输出采用 LED 灯进

行显示。

三、设计思路

1、整体思路:

为了实现 4bit 无符号数的模 9 加法运算,可以先将两个 4bit 的加数 a 和 b 先

分别模 9,相加之后再模 9 得到最终结果。

2、模 9 器:

先找出读入的 5bit 数与模 9 后的 4bit 数之间的关系,画出卡诺图,再根据

卡诺图得出其相应的逻辑表达式即可。设读入的 5bit 数为 carry、a、b、c、d,

模 9 后得到的 4bit 数为 w、x、y、z。则化简后得到的逻辑表达式分别为:

w = carry’ab’c’d’,

x= carry’bc + carry’a’b + carry’bd + carrya’b’c’d’,

y = carry’a’c + carry’cd + carry’abc’d’ + carrya’b’c’d’,

z= carry’a’d + carry’acd’ + carry’abd’ + carry a’b’c’d’。

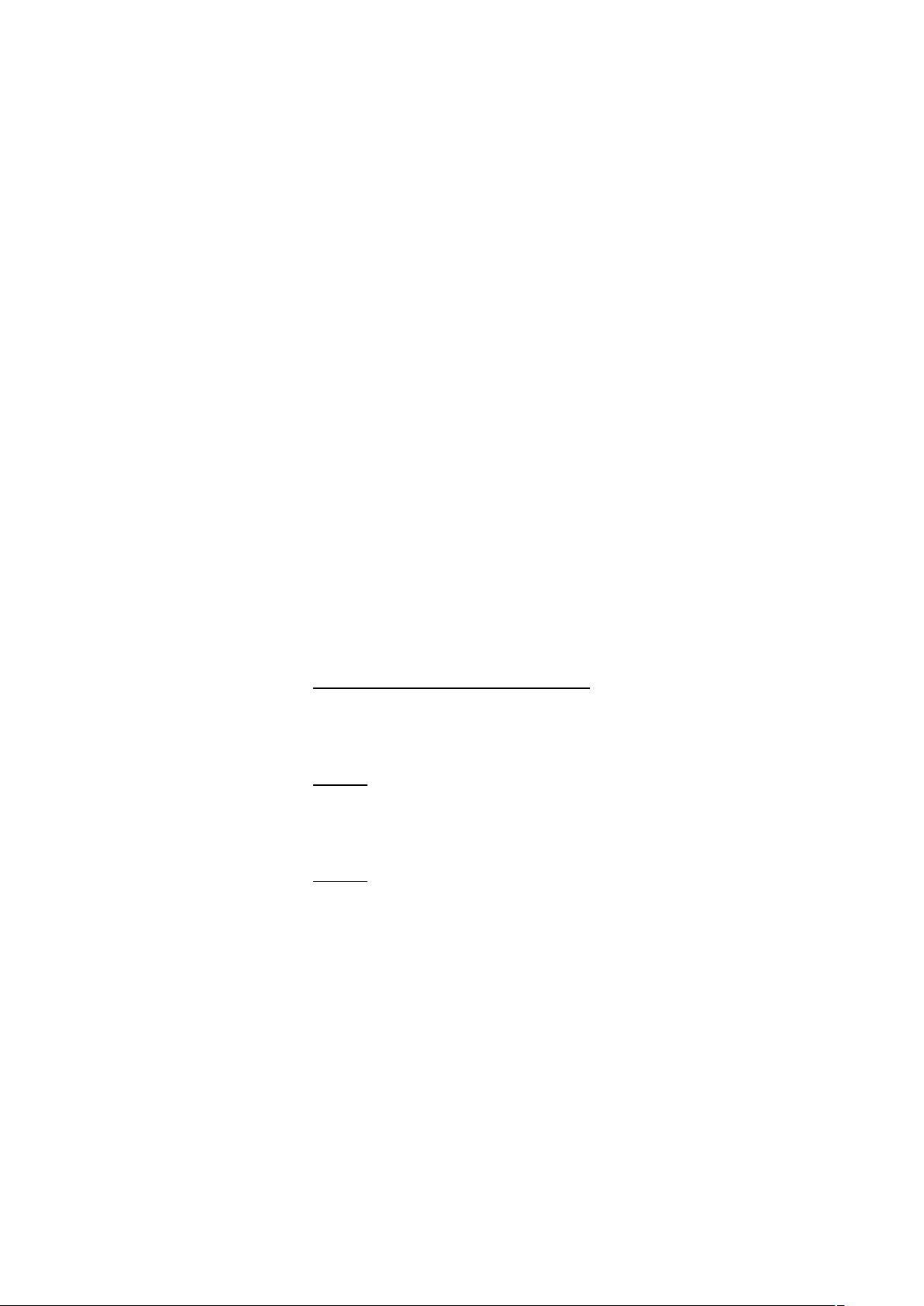

3、全加器:

全加器可以实现两个 1bit 数 a、b 和进位输入 cin 的相加,其真值表如下所

示:

这里全加器由半加器和或门构成,其原理图如下:

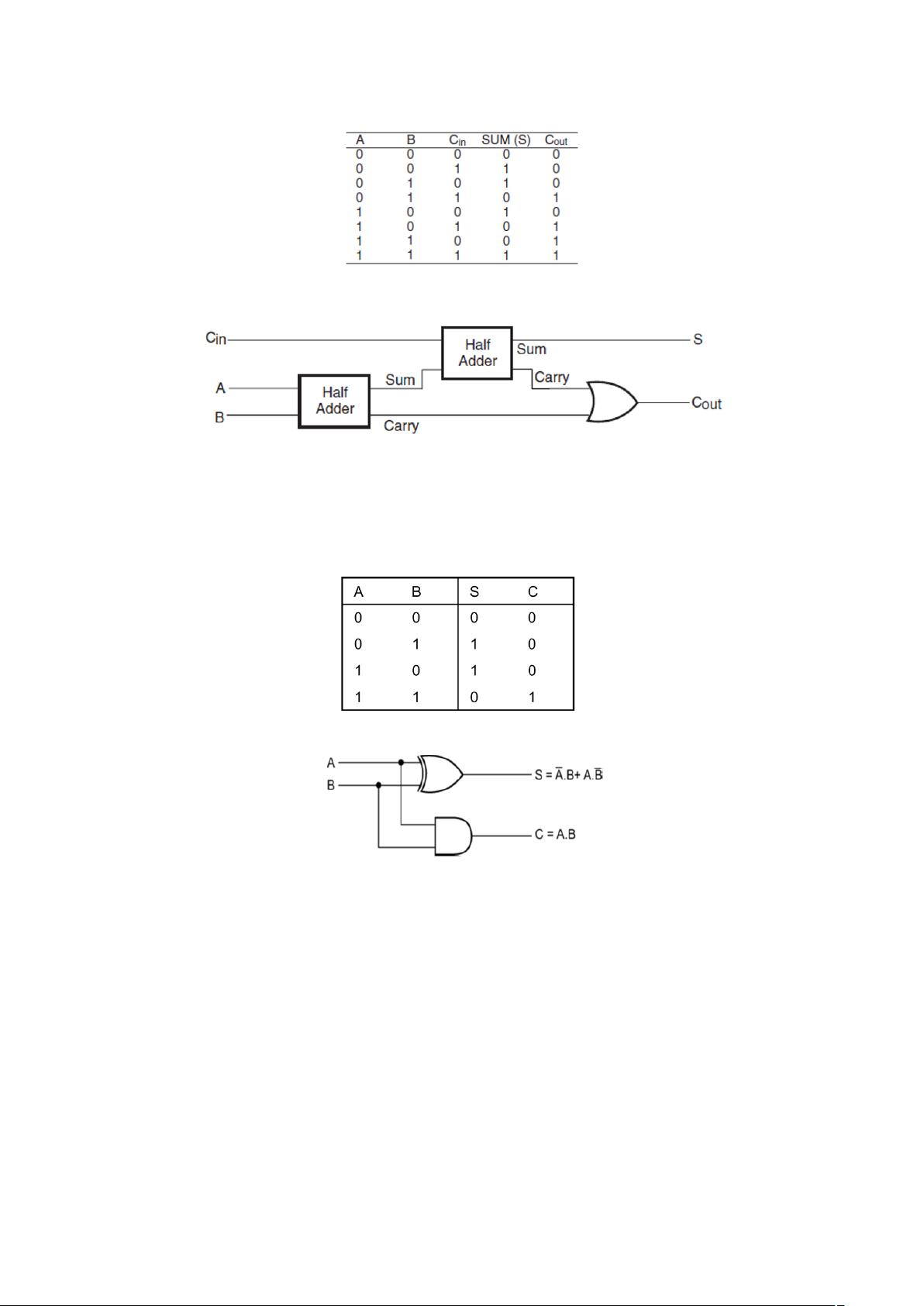

4、半加器:

半加器是全加器的基本组成单元,可以实现两个 1bit 数 a 和 b 的相加,并将

进位输出,其真值表如下:

半加器由一个异或门和一个与门构成,其原理图如下所示:

5、数码管显示:

单个数码管一共有 7 个端(不含小数点),用来表示组成一个数字的 7 个部

分,故只要找到这 7 个段和模 9 后的 4bit 数间的对应关系,将其画出卡诺图并化

简成逻辑表达式即可。设得到的 4bit 数为 a、b、c、d,则得到的 7 段 disa~disg

的表达式为:

disa=b + d + c’a’ + ac;

disb=c’ +d + b’ a’ + ab;

disc=a + b’ + c + d;

disd=ba’ + c’a’+ c’b + cb’a;

dise=d + ba’ + c’ a’;

disf=d + b’a’ + ca’ + cb’;

disg=d + ba’+ c’b+ ca’ + cb’;

四、程序设计

1、顶层:

entity main is

Port ( a1 : in STD_LOGIC;

a2 : in STD_LOGIC;

a3 : in STD_LOGIC;

a4 : in STD_LOGIC;

b1 : in STD_LOGIC;

b2 : in STD_LOGIC;

b3 : in STD_LOGIC;

b4 : in STD_LOGIC;

ans1 : out STD_LOGIC;

ans2 : out STD_LOGIC;

ans3 : out STD_LOGIC;

ans4 : out STD_LOGIC;

disA : out STD_LOGIC;

disB : out STD_LOGIC;

disC : out STD_LOGIC;

disD : out STD_LOGIC;

disE : out STD_LOGIC;

disF : out STD_LOGIC;

disG : out STD_LOGIC

);

end main;

architecture Behavioral of main is

COMPONENT fulladder

PORT(

a : IN std_logic;

b : IN std_logic;

ci : IN std_logic;

s : OUT std_logic;

co : OUT std_logic

);

END COMPONENT;

COMPONENT mod9

PORT(

carry : IN std_logic;

a : IN std_logic;

b : IN std_logic;

c : IN std_logic;

d : IN std_logic;

w : OUT std_logic;

x : OUT std_logic;

y : OUT std_logic;

z : OUT std_logic

);

END COMPONENT;

COMPONENT dis

PORT(

a : IN std_logic;

b : IN std_logic;

c : IN std_logic;

d : IN std_logic;

disa : OUT std_logic;

disb : OUT std_logic;

disc : OUT std_logic;

disd : OUT std_logic;

dise : OUT std_logic;

disf : OUT std_logic;

disg : OUT std_logic

);

END COMPONENT;

signal

c1,c2,c3,c4,s1,s2,s3,s4,ans11,ans22,ans33,ans44,a11,a22,a33,a44,b11,b22,b33,b44,temp :std_logi

c;

begin

--mod9_a--

temp <= '0';

Inst_mod9_a: mod9 PORT MAP(

carry => temp, --carry 是最高位

a => a4,

b => a3,

c => a2,

d => a1, --d 是最低位

w => a44, --w 是最高位

x => a33,

y => a22,

z => a11 --z 是最低位

);

剩余65页未读,继续阅读

资源评论

猫一样的女子245

- 粉丝: 95

- 资源: 2万+

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- postgresql-42.7.3.jar

- 2024-05-21 20-36-43.mkv

- 基于QT+C++的智能云监护仪项目,能够实时显示使用者心电、血氧、血压波形及其它各种参数+源码(毕业设计&课程设计&项目开发)

- 基于java开发的app接收硬件端传输的心音信号,具有显示心音波形,发出心音的功能+源码(毕业设计&课程设计&项目开发)

- Python 程序语言设计模式思路-行为型模式:职责链模式:将请求从一个处理者传递到下一个处理者

- 9241703124789646.16健身系统2.apk

- postgresql-16.3-1-windows-x64.exe

- Python 程序语言设计模式思路-结构型模式:装饰器讲解及利用Python装饰器模式实现高效日志记录和性能测试

- 基于YOLOv5和DeepSORT的多目标跟踪仿真与记录

- Python 程序语言设计模式思路-创建型模式:原型模式:通过复制现有对象来创建新对象,面向对象编程

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功