The ARM Instruction Set - ARM University Program - V1.0 1

The ARM Instruction Set

ARM

Advanced RISC Machines

The ARM Instruction Set - ARM University Program - V1.0 2

Processor Modes

* The ARM has six operating modes:

• User (unprivileged mode under which most tasks run)

• FIQ (entered when a high priority (fast) interrupt is raised)

• IRQ (entered when a low priority (normal) interrupt is raised)

• Supervisor (entered on reset and when a Software Interrupt instruction is

executed)

• Abort (used to handle memory access violations)

• Undef (used to handle undefined instructions)

* ARM Architecture Version 4 adds a seventh mode:

• System (privileged mode using the same registers as user mode)

The ARM Instruction Set - ARM University Program - V1.0 3

* ARM has 37 registers in total, all of which are 32-bits long.

• 1 dedicated program counter

• 1 dedicated current program status register

• 5 dedicated saved program status registers

• 30 general purpose registers

* However these are arranged into several banks, with the accessible

bank being governed by the processor mode. Each mode can access

• a particular set of r0-r12 registers

• a particular r13 (the stack pointer) and r14 (link register)

• r15 (the program counter)

• cpsr (the current program status register)

and privileged modes can also access

• a particular spsr (saved program status register)

The Registers

The ARM Instruction Set - ARM University Program - V1.0 4

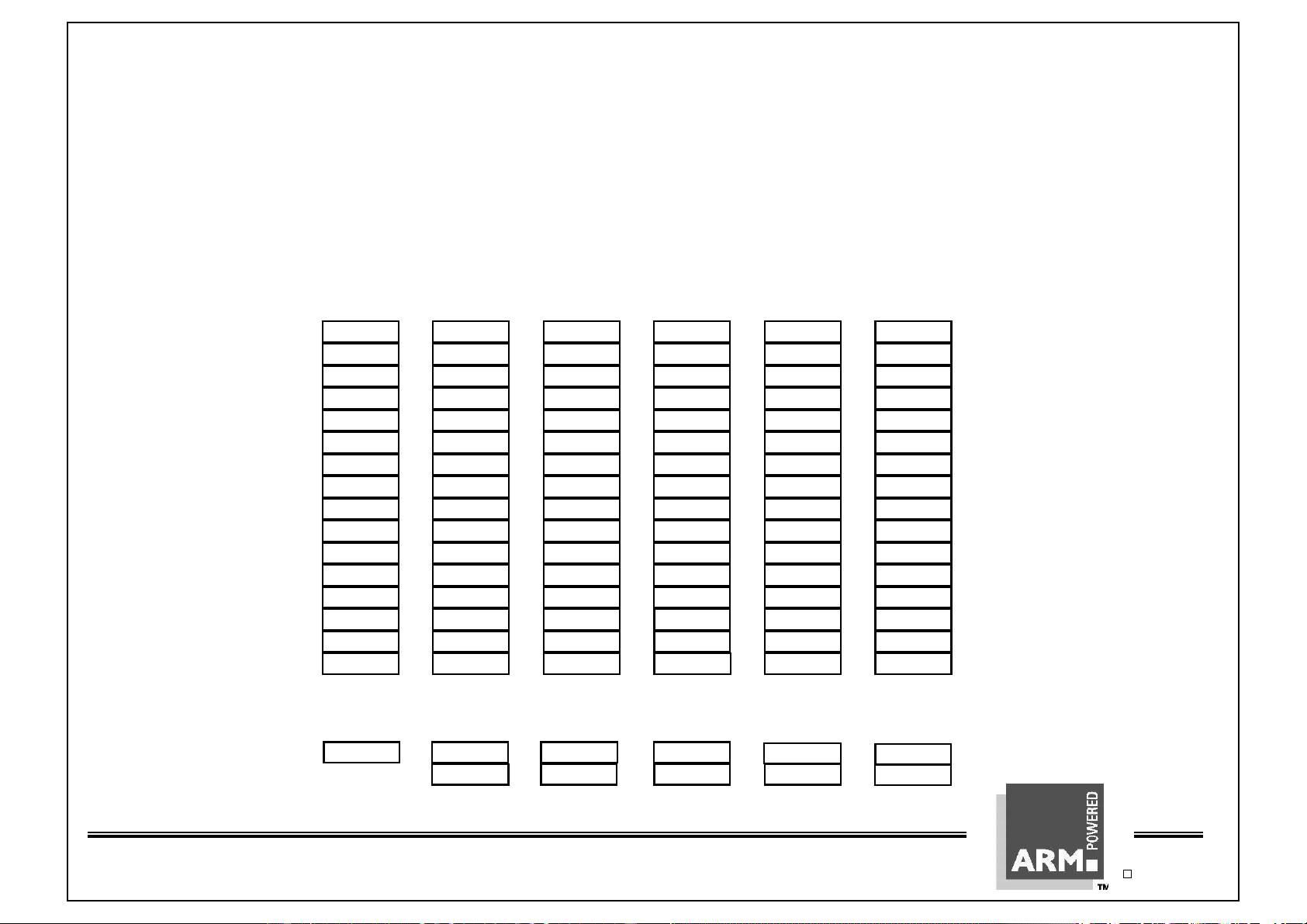

Register Organisation

General registers and Program Counter

Program Status Registers

r15 (pc)

r14 (lr)

r13 (sp)

r14_svc

r13_svc

r14_irq

r13_irq

r14_abt

r13_abt

r14_undef

r13_undef

User32 / System

FIQ32 Supervisor32 Abort32 IRQ32 Undefined32

cpsr

sprsr_fiqsprsr_fiqsprsr_fiq spsr_abtspsr_svcsprsr_fiqsprsr_fiqspsr_fiq sprsr_fiqsprsr_fiqsprsr_fiqsprsr_fiqsprsr_fiqspsr_irq

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r7

r4

r5

r2

r1

r0

r3

r6

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r15 (pc) r15 (pc) r15 (pc) r15 (pc) r15 (pc)

cpsr

cpsr

cpsrcpsrcpsr

r14_fiq

r13_fiq

r12_fiq

r10_fiq

r11_fiq

r9_fiq

r8_fiq

sprsr_fiqsprsr_fiqsprsr_fiqsprsr_fiqsprsr_fiqspsr_undef

The ARM Instruction Set - ARM University Program - V1.0 5

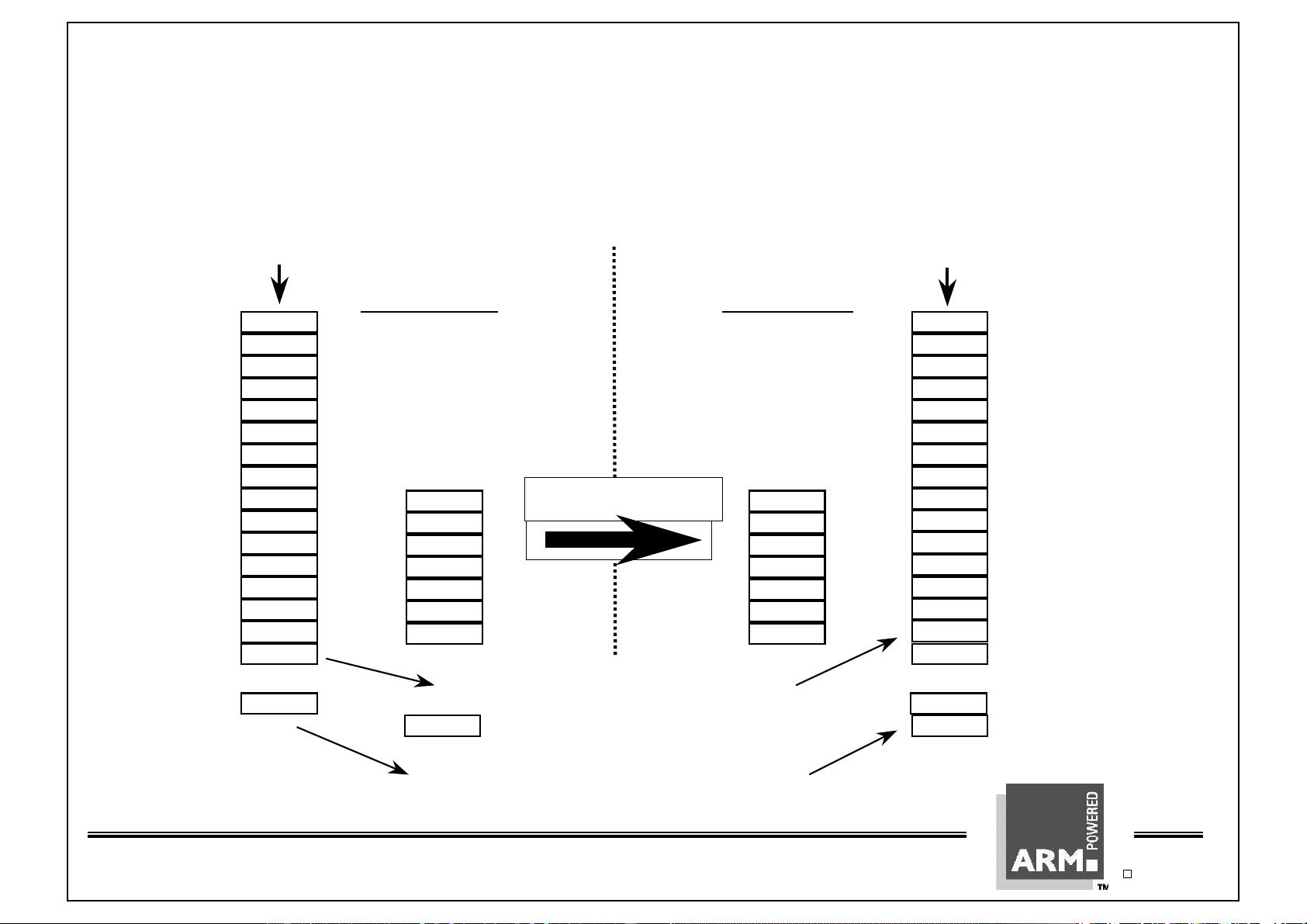

Register Example:

User to FIQ Mode

spsr_fiq

cpsr

r7

r4

r5

r2

r1

r0

r3

r6

r15 (pc)

r14_fiq

r13_fiq

r12_fiq

r10_fiq

r11_fiq

r9_fiq

r8_fiq

r14 (lr)

r13 (sp)

r12

r10

r11

r9

r8

User mode CPSR copied to FIQ mode SPSR

cpsr

r15 (pc)

r14 (lr)

r13 (sp)

r12

r10

r11

r9

r8

r7

r4

r5

r2

r1

r0

r3

r6

r14_fiq

r13_fiq

r12_fiq

r10_fiq

r11_fiq

r9_fiq

r8_fiq

Return address calculated from User mode

PC value and stored in FIQ mode LR

Registers in use

Registers in use

EXCEPTION

User Mode FIQ Mode

spsr_fiq