没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

AS3992

UHF RFID Single Chip Reader EPC Class1 Gen2 Compatible

www.austriamicrosystems.com/AS3992 Revision 1.0 1 - 52

Data Sheet

1 General Description

The AS3992 UHF Gen2 Reader chip is an integrated analog front-

end and provides protocol handling for ISO180006c/b 900MHz RFID

reader systems. Equipped with multiple built-in programming

options, the device is suitable for a wide range of UHF RFID

applications.

The AS3992 is pin to pin and firmware compatible with the previous

AS3990/91 IC's. It offers improved receive sensitivity to -86dB,

programmable Rx Dense Reader Mode (DRM) filters on chip and

pre-distortion. Fully scalable, the AS3992 is ideal for longer range

and higher power applications.

Offering DRM filtering on chip, combined with improved sensitivity

and pre-distortion allows the AS3992 to be the only true world wide

shippable IC. The reader configuration is achieved through setting

control registers allowing fine tuning of different reader parameters.

Parallel or serial interface can be selected for communication

between the host system (MCU) and the reader IC. When hardware

coders and decoders are used for transmission and reception, data

is transferred via 24 bytes FIFO register. In case of direct

transmission or reception, coders and decoders are bypassed and

the host system can service the analog front end in real time.

The transmitter generates 20dBm output power into 50Ω load and is

capable of ASK or PR-ASK modulation. The integrated supply

voltage regulators ensure supply rejection of the complete reader

system.

The transmission system comprises low level data coding. Automatic

generation of FrameSync, Preamble, and CRC is supported.

The receiver system allows AM and PM demodulation. The receiver

also comprises automatic gain control option (patent pending) and

selectable gain and signal bandwidth to cover a range of input link

frequency and bit rate options. The signal strength of AM and PM

modulation is measured and can be accessed in RSSI register. The

receiver output is selectable between digitized sub-carrier signal and

any of integrated sub-carrier decoders. Selected decoders deliver bit

stream and data clock as outputs.

The receiver system also comprises framing system. This system

performs the CRC check and organizes the data in bytes. Framed

data is accessible to the host system through a 24 byte FIFO

register.

To support external MCU and other circuitry a 3.3V regulated supply

and clock outputs are available. The regulated supply has 20mA

current capability.

The AS3992 is available in a 64-pin QFN (9mm x 9mm), ensuring

the smallest possible footprint.

2 Key Features

ISO18000-6C (EPC Gen2) full protocol support

ISO18000-6A,B compatibility in direct mode

Programmable Dense Reader Mode filters on chip allowing a

true World Wide Shippable device.

Improved receive sensitivity to -86dBm

On chip pre-distortion meaning improved external PA efficiency

Integrated low level transmission coding, Integrated low level

decoders

Integrated data framing, Integrated CRC checking

Parallel 8-bit or serial 4-pin SPI interface to MCU using 24 bytes

FIFO

Voltage range for communication to MCU between 1.8V and

5.5V

Can be powered by USB with no need for step conversion from

4.1 to 5.5 Volt.

Selectable clock output for MCU

Integrated supply voltage regulator (20mA), which can be used

to supply MCU and other external circuitry

Integrated supply voltage regulator for the RF output stage,

providing rejection to supply noise

Internal power amplifier (20dBm) for short range applications

Modulator using ASK or PR-ASK modulation

Adjustable ASK modulation index

AM & PM demodulation ensuring no “communication holes”

with automatic I/Q selection

Selectable reception gain, Reception automatic gain control

AD converter for measuring TX power using external RF power

detector

DA converter for controlling external power amplifier

Frequency hopping support

On-board VCO and PLL covering complete RFID frequency

range 840MHz to 960MHz

Oscillator using 20MHz crystal

Power down, standby and active mode available

3 Applications

The device is an ideal solution for UHF RFID reader systems and

hand-held UHF RFID readers.

www.austriamicrosystems.com/AS3992 Revision 1.0 2 - 52

AS3992

Data Sheet - Applications

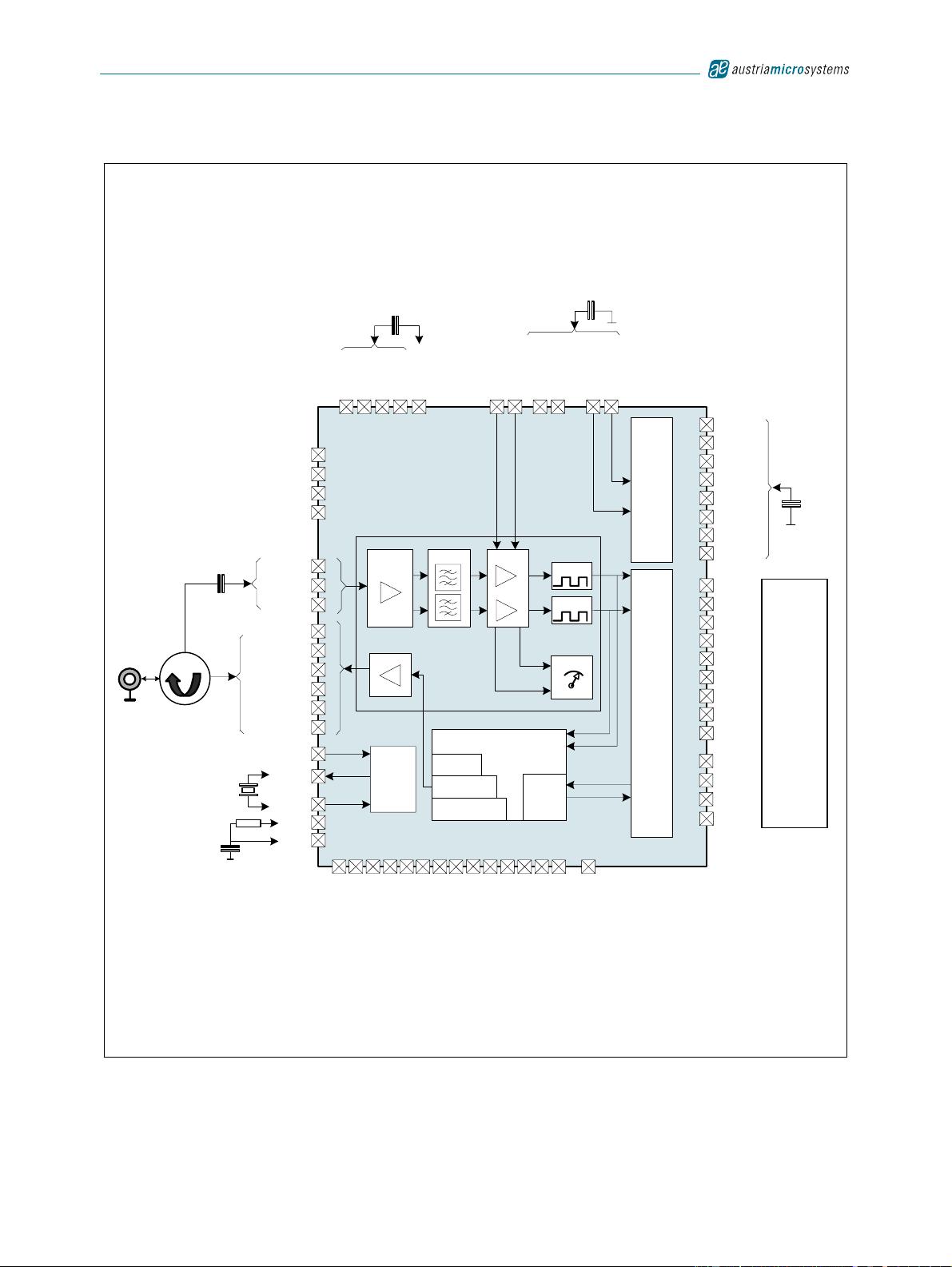

Figure 1. AS3992 Block Diagram

AS3992

Directional unit

COMN_A

COMP_B

COMN_B

VDD_5LFI

VSS

VSS

MIX_INP

MIX_INN

MIXS_IN

VSN_MIX

CBIB

CBV5

VEXT

VEXT2

RFOUTN_2

RFOUTN_1

RFOUTP_2

RFOUTP_1

VSN_1

VSN_2

VSN_3

VSN_4

VSN_5

VSN_D

RFOPX

RFONX

VSN_RFP

OSCO

OSCI

VSN_A

EXT_IN

VSN_CP

COMP_A

EXP_PAD

4xC

2xC

IQ Down-

Conversion

Mixer

RF Out

24 Byte

FIFO

EPC Gen 2 Protocol

Handling

CRC

GEN-2

Frame Gen

OAD

OAD_2

ADC

DAC

VCO

CP

31

30

58

4

7

9

10

27

28

20

21

32

33

56

36

37

60

62

6

8111214222324

25

26 29 35 55 57 65

64

2 1 3 5 16 17

RSSI

Digitizer

Digitizer

Analog

Front-end

Gain FilterDRM Filter

Oscillator

& Timing

System

MCU Interface

EN

IRQ

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

CLSYS

CLK

VDD_IO

VDD_D

VDD_RF

VDD_B

AGD

VDD_A

VDDLF

VDD_RFP

7xC

Micro

controller

Supply Regulators &

References

49

40

39

50

48

47

46

45

44

43

42

41

51

VOSC

34

61

63

59

54

19

18

38

VDD_MIX

VDD_TXPAB

13 15

CD1

CD2

53 52

www.austriamicrosystems.com/AS3992 Revision 1.0 3 - 52

AS3992

Data Sheet - Contents

Contents

1 General Description.................................................................................................................................................................. 1

2 Key Features............................................................................................................................................................................. 1

3 Applications............................................................................................................................................................................... 1

4 Pin Assignments....................................................................................................................................................................... 5

4.1 Pin Descriptions.................................................................................................................................................................................... 5

5 Absolute Maximum Ratings...................................................................................................................................................... 8

6 Electrical Characteristics........................................................................................................................................................... 9

7 Detailed Description................................................................................................................................................................ 11

7.1 Supply................................................................................................................................................................................................. 11

7.1.1 Power Modes............................................................................................................................................................................. 12

7.2 Host Communication .......................................................................................................................................................................... 12

7.3 VCO and PLL ..................................................................................................................................................................................... 13

7.3.1 VCO and External RF Source.................................................................................................................................................... 13

7.3.2 PLL ............................................................................................................................................................................................ 13

7.4 Chip Status Control ............................................................................................................................................................................ 13

7.5 Protocol Control.................................................................................................................................................................................. 13

7.6 Option Registers Preset ..................................................................................................................................................................... 14

7.7 Transmitter.......................................................................................................................................................................................... 14

7.7.1 Normal Mode ............................................................................................................................................................................. 14

7.7.2 Direct Mode ............................................................................................................................................................................... 15

7.7.3 Modulator................................................................................................................................................................................... 16

7.7.4 Amplifier..................................................................................................................................................................................... 16

7.7.5 TX Pre-Distortion ....................................................................................................................................................................... 17

7.8 Receiver ............................................................................................................................................................................................. 17

7.8.1 Input Mixer................................................................................................................................................................................. 17

7.8.2 DRM RX Filter............................................................................................................................................................................ 17

7.8.3 RX Filter Calibration................................................................................................................................................................... 18

7.8.4 Fast AC Coupling....................................................................................................................................................................... 18

7.8.5 RX Gain ..................................................................................................................................................................................... 19

7.8.6 Received Signal Strength Indicator (RSSI)................................................................................................................................ 19

7.8.7 Reflected RF Level Indicator ..................................................................................................................................................... 19

7.8.8 Normal Mode ............................................................................................................................................................................. 19

7.8.9 Direct Mode ............................................................................................................................................................................... 20

7.8.10 Normal Mode With Mixer DC Level Output and Enable RX Output Available......................................................................... 21

7.9 ADC / DAC ......................................................................................................................................................................................... 21

7.9.1 DA Converter............................................................................................................................................................................. 21

7.9.2 AD Converter............................................................................................................................................................................. 21

7.10 Reference Oscillator......................................................................................................................................................................... 21

8 Application Information ........................................................................................................................................................... 22

8.1 Configuration Registers Address Space............................................................................................................................................. 22

8.2 Main Configuration Registers ............................................................................................................................................................. 24

8.3 Control Registers - Low Level Configuration Registers...................................................................................................................... 25

8.4 Status Registers ................................................................................................................................................................................. 29

8.5 Test Registers..................................................................................................................................................................................... 32

8.6 PLL, Modulator, DAC, and ADC Registers......................................................................................................................................... 34

www.austriamicrosystems.com/AS3992 Revision 1.0 4 - 52

AS3992

Data Sheet - Contents

8.7 RX Length Registers .......................................................................................................................................................................... 37

8.8 FIFO Control Registers....................................................................................................................................................................... 38

8.9 Direct Commands............................................................................................................................................................................... 39

8.9.1 Idle (80)...................................................................................................................................................................................... 40

8.9.2 Hop to Main Frequency (84)...................................................................................................................................................... 40

8.9.3 Hop to Auxiliary Frequency (85) ................................................................................................................................................ 40

8.9.4 Trigger AD Conversion (87)....................................................................................................................................................... 40

8.9.5 Trigger RX Filter Calibration (88)............................................................................................................................................... 40

8.9.6 Decrease RX Filter Calibration Data (89) .................................................................................................................................. 40

8.9.7 Increase RX Filter Calibration Data (8A) ................................................................................................................................... 40

8.9.8 Reset FIFO (8F)......................................................................................................................................................................... 40

8.9.9 Transmission With CRC (90)..................................................................................................................................................... 40

8.9.10 Transmission With CRC Expecting Header Bit (91) ................................................................................................................ 41

8.9.11 Transmission Without CRC (92).............................................................................................................................................. 41

8.9.12 Delayed Transmission With CRC (93)..................................................................................................................................... 41

8.9.13 Delayed Transmission Without CRC (94)................................................................................................................................ 41

8.9.14 Block RX (96)........................................................................................................................................................................... 41

8.9.15 Enable RX (97) ........................................................................................................................................................................ 41

8.10 EPC GEN2 Specific Commands ...................................................................................................................................................... 41

8.10.1 Query (98)................................................................................................................................................................................ 41

8.10.2 QueryRep (99)......................................................................................................................................................................... 41

8.10.3 QueryAdjustUp (9A)................................................................................................................................................................. 41

8.10.4 QueryAdjustNic (9B)................................................................................................................................................................ 41

8.10.5 QueryAdjustDown (9C)............................................................................................................................................................ 42

8.10.6 ACK (9D) ................................................................................................................................................................................. 42

8.10.7 NAK (9E).................................................................................................................................................................................. 42

8.10.8 ReqRN (9F) ............................................................................................................................................................................. 42

8.11 Reader Communication Interface..................................................................................................................................................... 42

8.12 Parallel Interface Communication..................................................................................................................................................... 44

8.13 Serial Interface Communication ....................................................................................................................................................... 46

8.13.1 Timing Diagrams...................................................................................................................................................................... 47

8.13.2 Timing Parameters .................................................................................................................................................................. 48

8.14 FIFO ................................................................................................................................................................................................. 48

9 Package Drawings and Markings ........................................................................................................................................... 49

10 Ordering Information............................................................................................................................................................. 51

www.austriamicrosystems.com/AS3992 Revision 1.0 5 - 52

AS3992

Data Sheet - Pin Assignments

4 Pin Assignments

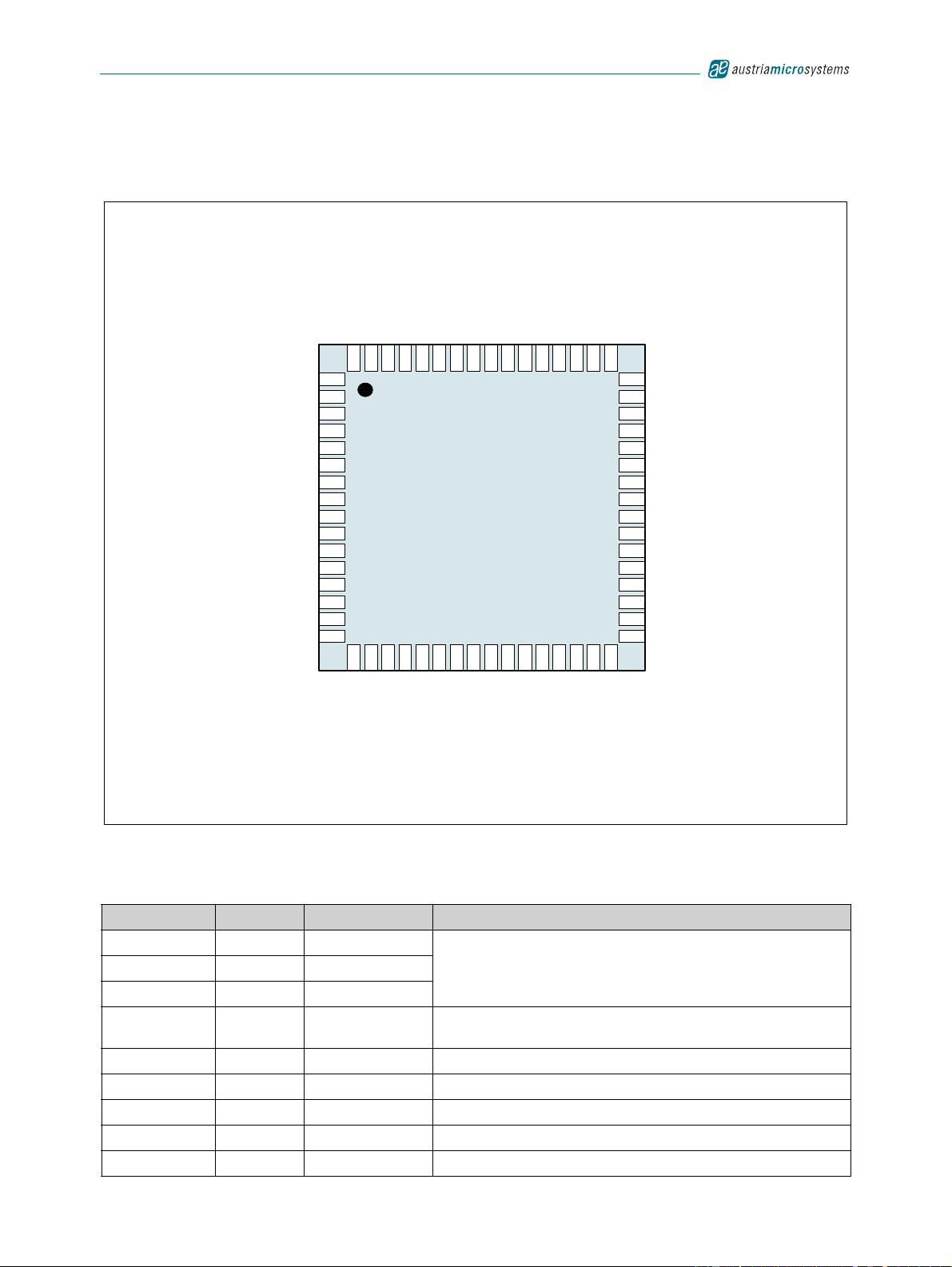

Figure 2. Pin Assignments (Top View)

4.1 Pin Descriptions

Table 1. Pin Descriptions

Pin Name Pin Number Pin Type Description

COMN_A 1 Bidirectional

Connect de-coupling capacitor to VDD_5LFI

COMP_B 2 Bidirectional

COMN_B 3 Bidirectional

DAC 4 Output

DAC output for external amplifier support, Output Resistance of DAC pin is

1kΩ

VDD_5LFI 5 Supply Input

Positive supply for LF input stage, connect to VDD_MIX

VSS 6 Supply Input

Substrate

MIX_INP 7 Input

Differential mixer positive input

VSS 8 Supply Input

Substrate

MIX_INN 9 Input

Differential mixer negative input

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

39

38

37

36

35

34

33

46

45

44

43

42

41

40

48

47

28

29

30

31

32

23

24

25

26

27

18

19

20

21

22

17

53

52

51

50

49

58

57

56

55

54

63

62

61

60

59

64

AS3992

RFOUTN_2

VSN_D

OAD2

OAD

RFONX

VSN_2

VSN_3

VSN_4

VSN_5

RFOUTN_1

VDD_RF

VDD_B

RFOUTP_1

RFOUTP_2

VSN_1

VEXT2

CD1

CD2

VDD_IO

CLK

CLSYS

ADC

VSN_CP

EXT_IN

VSN_A

AGD

VDDLF

CP

VOSC

VCO

VDD_A

COMP_A

EN

VDD_D

OSCO

OSCI

VSN_RFP

VDD_RFP

RFOPX

IO5

IO4

IO3

IO2

IO1

IO0

IRQ

IO7

IO6

COMN_A

COMP_B

COMN_B

DAC

VDD_5LFI

VSS

MIX_INP

VSS

MIX_INN

MIXS_IN

VSN_MIX

CBIB

VDD_MIX

CBV5

VDD_TXPAB

VEXT

剩余51页未读,继续阅读

资源评论

ZHIMATANG272013-05-21很好 对我的帮助很大 正好在学习这个项目

ZHIMATANG272013-05-21很好 对我的帮助很大 正好在学习这个项目 wwrwrews2015-04-21资源很好用,值得一看非常!

wwrwrews2015-04-21资源很好用,值得一看非常!

sparkle_q

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于matlab实现夜间车牌识别程序(1).rar

- 基于matlab实现图像处理,本程序使用背景差分法对来往车辆进行检测和跟踪.rar

- 基于matlab实现视频监控中车型识别代码,自己写的,希望和大家多多交流.rar

- sdk.config

- 基于matlab实现配电网三相潮流计算方法,对几种常用的配电网潮流计算方法进行了对比分析.rar

- 基于matlab实现配电网潮流 经典33节点 前推回代法潮流计算 回代电流 前推电压 带注释.rar

- 基于matlab实现模拟退火遗传算法的车辆调度问题研究,用MATLAB语言加以实现.rar

- 基于matlab实现蒙特卡洛的的移动传感器节点定位算法仿真代码.rar

- 华中数控系统818用户说明书

- 基于matlab实现卡尔曼滤波器完成多传感器数据融合 对多个机器人的不同传感器数据进行融合估计足球精确位置.rar

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功