没有合适的资源?快使用搜索试试~ 我知道了~

verilog HDL硬件描述语言(入门级)

温馨提示

试读

40页

提供给初学verilog HDL语言的学生或相关工作人员的一本不错的教材(pdf版)

资源推荐

资源详情

资源评论

1

Hardware Description LanguageHDL

Verilog HDLVHDL

Netlist

ASICEPLDFPGA

IversonHDL

HDLIEEEVerilog HDLVHDL

Verilog HDLC

Verilog HDL

l Verilog HDL

l

I/O

l

l

Verilog HDL

2

Verilog HDL

Verilog HDL

ALTERAMAX+PLUS IIMAX+PLUS II

Verilog HDL

Verilog HDL

inputoutputinout

assign

alwaysinitial

endmodule

module counter (out, cout, data, load, cin, clk);

parameter count_bits=4

output [count_bits:1] out;

output cout;

input load, cin, clk;

3

input [count_bits:1] data;

reg [count_bits:1] out;

assign cout=&out&cin;

always @(posedge clk)

begin

if (load) out= data;

else out = out + cin;

end

endmodule

Verilog HDL

Verilog HDL

inputoutputinout

Verilog HDL

endmodule

///**/

Verilog HDL

Verilog HDL

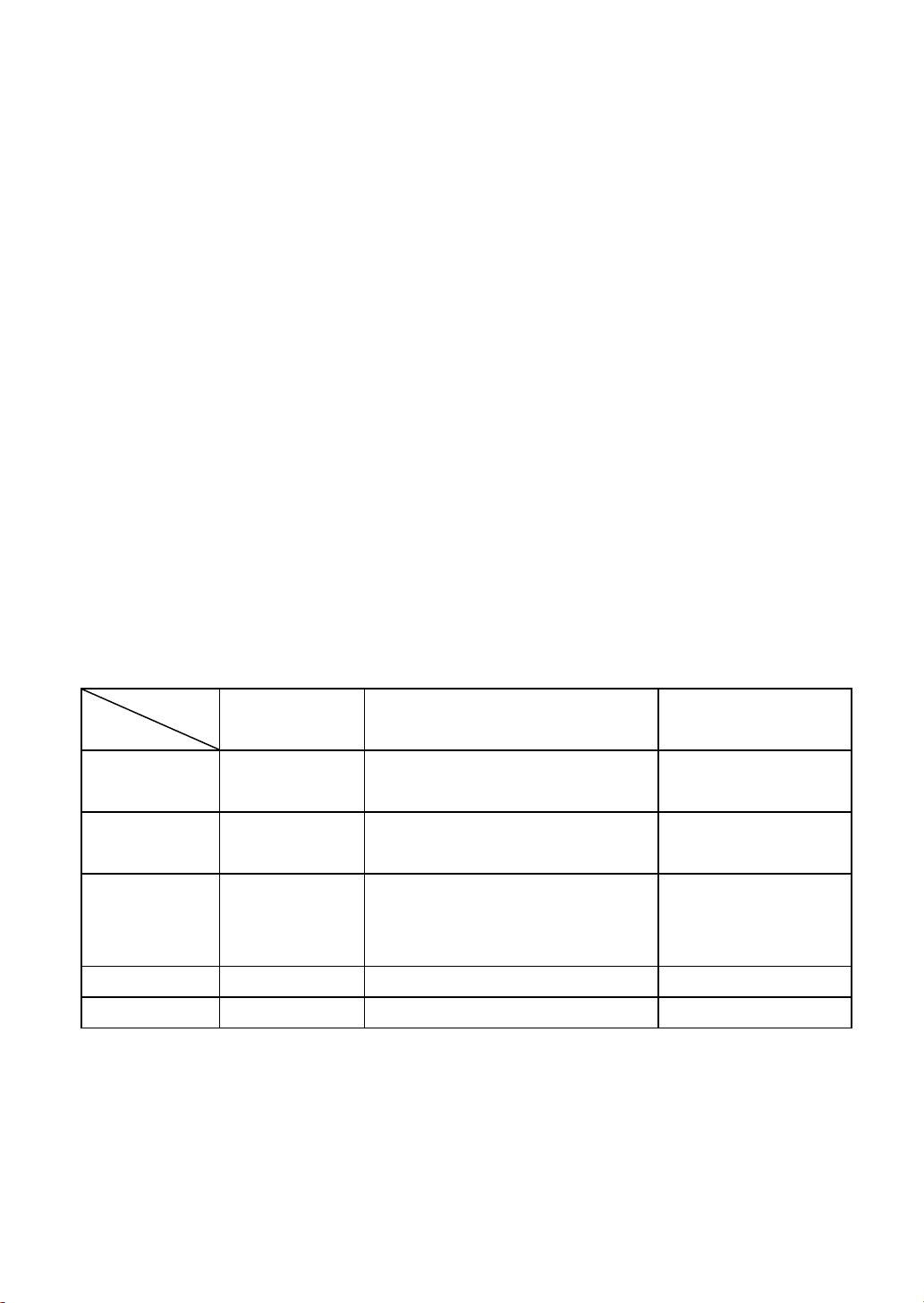

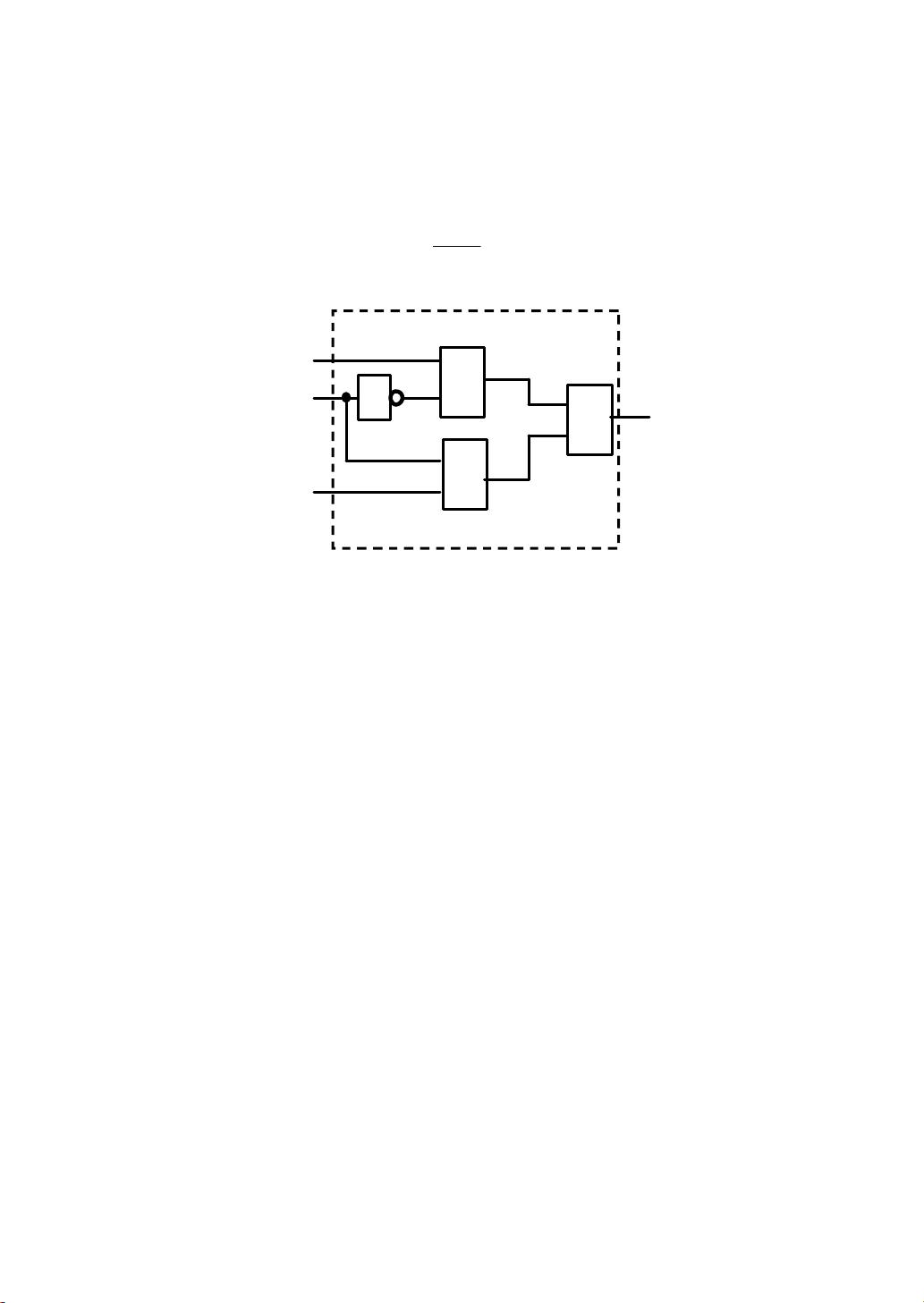

notG1and

G2G3orG4notandorVerilog HDL

module mux2_1 (A, B, select, OUT);

input A, B, select;

output OUT;

wire y1,y2,y3;

4

not G1(y1,select);

and G2(y2,A,y1);

and G3(y3,B,select);

or G4(OUT,y2,y3);

7.1 BselectAselectout •+•=

assign

module mux2x1_df (A, B, select, OUT);

input A, B, select;

output OUT;

assign OUT = select ? B : A;

endmodule

always

module mux2x1_bh(A, B, select, OUT);

input A, B, select;

output OUT;

&

1

&

1

select

A

B

OUT

y2

y3

G1

G2

G3

G4

y1

5

reg OUT;

always @ (select or A or B) selectA B

if (select = = 0) OUT = A;

else OUT = B;

endmodule

assignalways

Verilog HDL

Verilog HDL

Verilog HDL

Verilog HDL

Verilog HDL

0

1

x

z

erilog HDL

Verilog HDL

'

剩余39页未读,继续阅读

资源评论

benqiangchan2012-12-28学习verilog知识的基础读物,不错

benqiangchan2012-12-28学习verilog知识的基础读物,不错

sleep12

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功