没有合适的资源?快使用搜索试试~ 我知道了~

TMS320C66X datasheet DSP

需积分: 9 5 下载量 159 浏览量

2018-08-31

10:37:03

上传

评论 1

收藏 2.19MB PDF 举报

温馨提示

TMS320C66X datasheet The TMS320C6678 DSP is a highest-performance fixed/floating-point DSP that is based on TI's KeyStone multicore architecture. Incorporating the new and innovative C66x DSP core, this device can run at a core speed of up to 1.4 GHz. For developers of a broad range of applications, such as mission-critical systems, medical imaging, test and automation, and other applications requiring high performance, TI's TMS320C6678 DSP offers 11.2 GHz cumulative DSP and enables a platform that is power-efficient and easy to use. In addition, it is fully backward compatible with all existing C6000 family fixed and floating point DSPs.

资源推荐

资源详情

资源评论

Multicore Fixed and Floating-Point Digital Signal Processor

TMS320C6678

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and

other important disclaimers. PRODUCTION DATA.

Check for Evaluation Modules (EVM): TMS320C6678

SPRS691E—November 2010—Revised March 2014

1 TMS320C6678 Features and Description

1.1 Features

• Eight TMS320C66x™ DSP Core Subsystems (C66x

CorePacs), Each with

– 1.0 GHz, 1.25 GHz, or 1.4 GHz C66x

Fixed/Floating-Point CPU Core

› 44.8 GMAC/Core for Fixed Point @ 1.4 GHz

› 22.4 GFLOP/Core for Floating Point @ 1.4 GHz

–Memory

› 32K Byte L1P Per Core

› 32K Byte L1D Per Core

› 512K Byte Local L2 Per Core

• Multicore Shared Memory Controller (MSMC)

– 4096KB MSM SRAM Memory Shared by Eight DSP

C66x CorePacs

– Memory Protection Unit for Both MSM SRAM and

DDR3_EMIF

• Multicore Navigator

– 8192 Multipurpose Hardware Queues with Queue

Manager

– Packet-Based DMA for Zero-Overhead Transfers

• Network Coprocessor

– Packet Accelerator Enables Support for

› Transport Plane IPsec, GTP-U, SCTP, PDCP

› L2 User Plane PDCP (RoHC, Air Ciphering)

› 1-Gbps Wire-Speed Throughput at 1.5 MPackets

Per Second

– Security Accelerator Engine Enables Support for

› IPSec, SRTP, 3GPP, WiMAX Air Interface, and

SSL/TLS Security

› ECB, CBC, CTR, F8, A5/3, CCM, GCM, HMAC, CMAC,

GMAC, AES, DES, 3DES, Kasumi, SNOW 3G, SHA-1,

SHA-2 (256-bit Hash), MD5

› Up to 2.8 Gbps Encryption Speed

•Peripherals

– Four Lanes of SRIO 2.1

› 1.24/2.5/3.125/5 GBaud Operation Supported Per

Lane

› Supports Direct I/O, Message Passing

› Supports Four 1×, Two 2×, One 4×, and Two 1× +

One 2× Link Configurations

–PCIe Gen2

› Single Port Supporting 1 or 2 Lanes

›Supports Up To 5 GBaud Per Lane

–HyperLink

› Supports Connections to Other KeyStone

Architecture Devices Providing Resource

Scalability

› Supports up to 50 Gbaud

– Gigabit Ethernet (GbE) Switch Subsystem

›Two SGMII Ports

› Supports 10/100/1000 Mbps Operation

– 64-Bit DDR3 Interface (DDR3-1600)

› 8G Byte Addressable Memory Space

– 16-Bit EMIF

– Two Telecom Serial Ports (TSIP)

› Supports 1024 DS0s Per TSIP

› Supports 2/4/8 Lanes at 32.768/16.384/8.192 Mbps

Per Lane

–UART Interface

–I

2

C Interface

–16 GPIO Pins

–SPI Interface

– Semaphore Module

– Sixteen 64-Bit Timers

– Three On-Chip PLLs

• Commercial Temperature:

– 0°C to 85°C

• Extended Temperature:

–-40°C to 100°C

2 TMS320C6678 Features and Description Copyright 2014 Texas Instruments Incorporated

SPRS691E—March 2014

Multicore Fixed and Floating-Point Digital Signal Processor

TMS320C6678

Submit Documentation Feedback

1.2 Applications

• Mission-Critical Systems

• High-Performance Computing Systems

• Communications

•Audio

• Video Infrastructure

•Imaging

•Analytics

•Networking

• Media Processing

• Industrial Automation

• Automation and Process Control

1.3 KeyStone Architecture

TI’s KeyStone Multicore Architecture provides a high-performance structure for integrating RISC and DSP cores

with application-specific coprocessors and I/O. KeyStone is the first of its kind that provides adequate internal

bandwidth for nonblocking access to all processing cores, peripherals, coprocessors, and I/O. This is achieved with

four main hardware elements: Multicore Navigator, TeraNet, Multicore Shared Memory Controller, and

HyperLink.

Multicore Navigator is an innovative packet-based manager that controls 8192 queues. When tasks are allocated to

the queues, Multicore Navigator provides hardware-accelerated dispatch that directs tasks to the appropriate

available hardware. The packet-based system on a chip (SoC) uses the two Tbps capacity of the TeraNet switched

central resource to move packets. The Multicore Shared Memory Controller enables processing cores to access

shared memory directly without drawing from TeraNet’s capacity, so packet movement cannot be blocked by

memory access.

HyperLink provides a 50-Gbaud chip-level interconnect that allows SoCs to work in tandem. Its low-protocol

overhead and high throughput make HyperLink an ideal interface for chip-to-chip interconnections. Working with

Multicore Navigator, HyperLink dispatches tasks to tandem devices transparently and executes tasks as if they are

running on local resources.

1.4 Device Description

The TMS320C6678 DSP is a highest-performance fixed/floating-point DSP that is based on TI's KeyStone multicore

architecture. Incorporating the new and innovative C66x DSP core, this device can run at a core speed of up to

1.4 GHz. For developers of a broad range of applications, such as mission-critical systems, medical imaging, test and

automation, and other applications requiring high performance, TI's TMS320C6678 DSP offers 11.2 GHz

cumulative DSP and enables a platform that is power-efficient and easy to use. In addition, it is fully backward

compatible with all existing C6000 family fixed and floating point DSPs.

TI's KeyStone architecture provides a programmable platform integrating various subsystems (C66x cores, memory

subsystem, peripherals, and accelerators) and uses several innovative components and techniques to maximize

intra-device and inter-device communication that allows the various DSP resources to operate efficiently and

seamlessly. Central to this architecture are key components such as Multicore Navigator that allows for efficient data

management between the various device components. The TeraNet is a non-blocking switch fabric enabling fast and

contention-free internal data movement. The multicore shared memory controller allows access to shared and

external memory directly without drawing from switch fabric capacity.

Multicore Fixed and Floating-Point Digital Signal Processor

Copyright 2014 Texas Instruments Incorporated TMS320C6678 Features and Description 3

SPRS691E—March 2014

TMS320C6678

Submit Documentation Feedback

For fixed-point use, the C66x core has 4× the multiply accumulate (MAC) capability of C64x+ cores. In addition,

the C66x core integrates floating point capability and the per-core raw computational performance in an

industry-leading 44.8 GMACS/core and 22.4 GFLOPS/core (@1.4 GHz operating frequency). It can execute 8

single-precision floating point MAC operations per cycle and can perform double- and mixed-precision operations,

and is IEEE754 compliant. The C66x core incorporates 90 new instructions (compared to the C64x+ core) targeted

for floating point and vector math oriented processing. These enhancements yield sizeable performance

improvements in popular DSP kernels used in signal processing, mathematical, and image acquisition functions.

The C66x core is backwards code-compatible with TI's previous generation C6000 fixed and floating point DSP

cores, ensuring software portability and shortened software development cycles for applications migrating to faster

hardware.

The C6678 DSP integrates a large amount of on-chip memory. In addition to 32KB of L1 program and data cache,

there is 512KB of dedicated memory per core that can be configured as mapped RAM or cache. The device also

integrates 4096KB of Multicore Shared Memory that can be used as a shared L2 SRAM and/or shared L3 SRAM. All

L2 memories incorporate error detection and error correction. For fast access to external memory, this device

includes a 64-bit DDR-3 external memory interface (EMIF) running at 1600 MHz and has ECC DRAM support.

This family supports a plethora of high speed standard interfaces including RapidIO ver 2, PCI Express Gen2, and

Gigabit Ethernet, as well as an integrated Ethernet switch. It also includes I

2

C, UART, Telecom Serial Interface Port

(TSIP), and a 16-bit EMIF, along with general purpose CMOS IO. For high throughput, low latency communication

between devices or with an FPGA, this device also sports a 50-Gbaud full-duplex interface called HyperLink. Adding

to the network awareness of this device is a network co-processor that includes both packet and optional security

acceleration. The packet accelerator can process up to 1.5 M packets/s and enables a single IP address to be used for

the entire multicore C6678 device. It also provides L2 to L4 classification, along with checksum and QoS capabilities.

The C6678 device has a complete set of development tools, which includes: an enhanced C compiler, an assembly

optimizer to simplify programming and scheduling, and a Windows® debugger interface for visibility into source

code execution.

4 TMS320C6678 Features and Description Copyright 2014 Texas Instruments Incorporated

SPRS691E—March 2014

Multicore Fixed and Floating-Point Digital Signal Processor

TMS320C6678

Submit Documentation Feedback

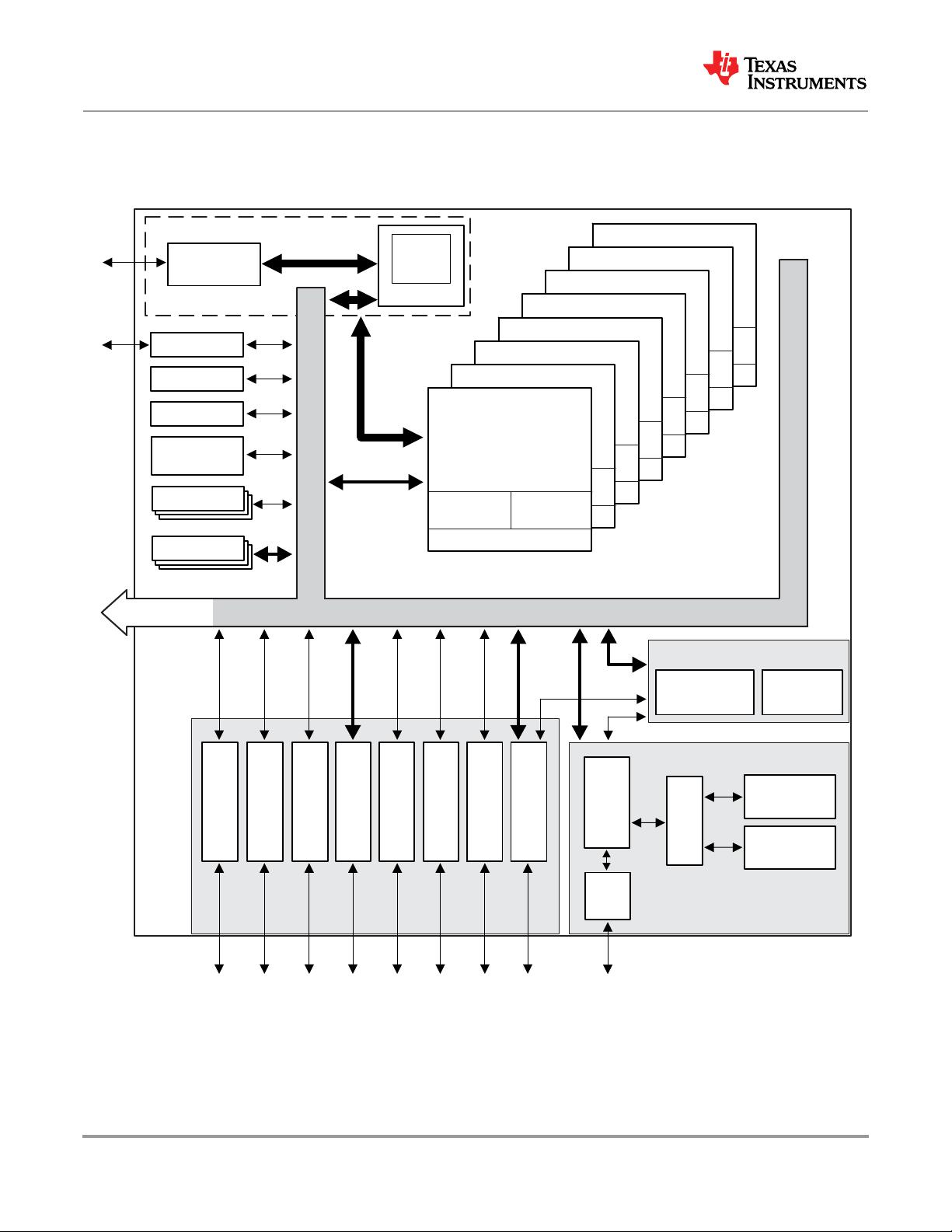

1.5 Functional Block Diagram

Figure 1-1 shows the functional block diagram of the TMS320C6678 device.

Figure 1-1 Functional Block Diagram

8 Cores @ up to 1.4 GHz

Power

Management

Debug & Trace

Boot ROM

Semaphore

SRIO 4´

PCIe 2´

UART

TSIP ´2

SPI

IC

2

Packet

DMA

Multicore Navigator

Queue

Manager

GPIO

´3

PLL

EDMA

´3

EMIF 16

4MB

MSM

SRAM

64-Bit

DDR3 EMIF

Memory Subsystem

MSMC

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

C66x™

CorePac

32KB L1

P-Cache

32KB L1

D-Cache

512KB L2 Cache

TeraNet

HyperLink

TeraNet

Network Coprocessor

Switch

Ethernet

Switch

SGMII

2

´

Packet

Accelerator

Security

Accelerator

6678

Multicore Fixed and Floating-Point Digital Signal Processor

Copyright 2014 Texas Instruments Incorporated TMS320C6678 Features and Description 5

SPRS691E—March 2014

TMS320C6678

Submit Documentation Feedback

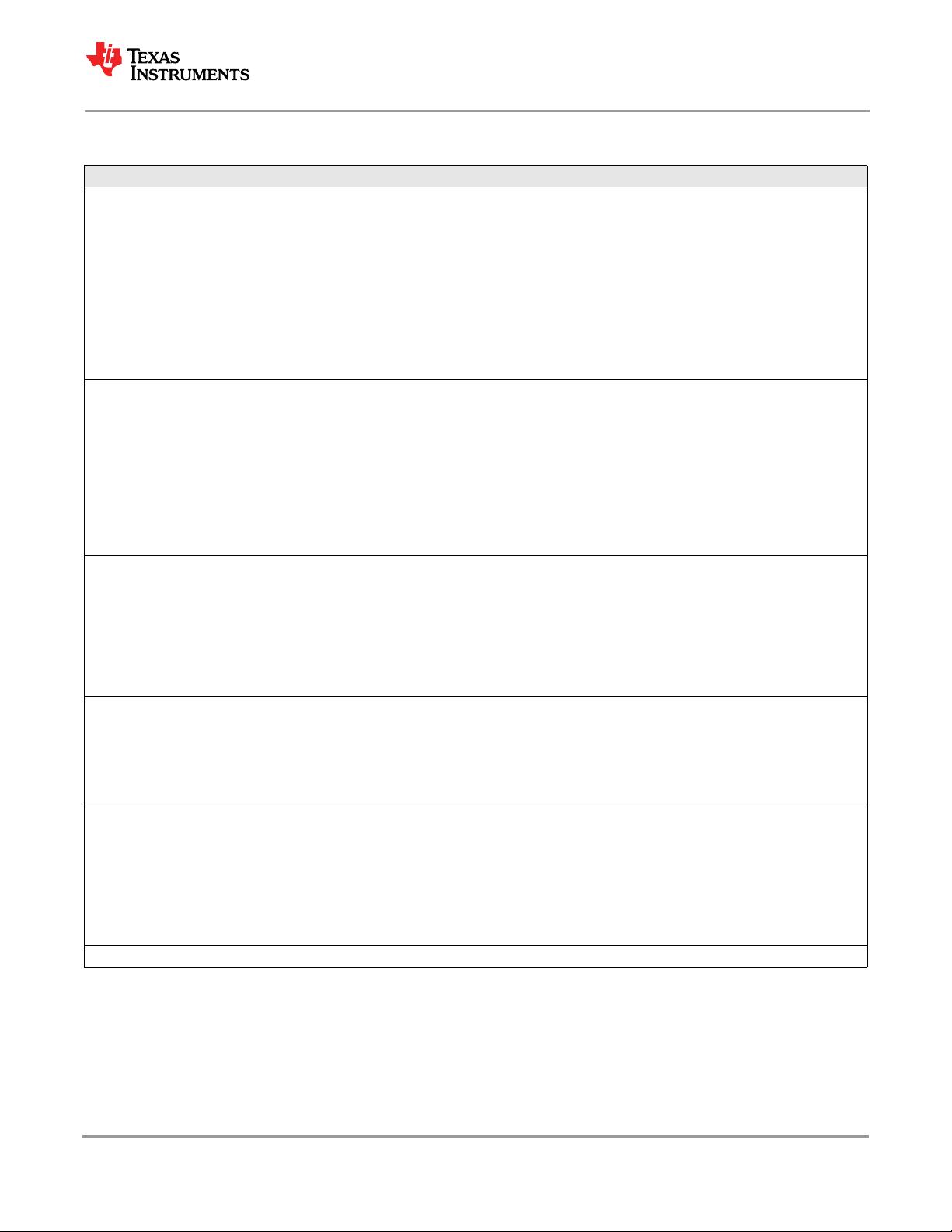

1.6 Release History

For detailed revision information, see ‘‘Revision History’’ on page 236.

Revision Date Description/Comments

SPRS691E March 2014 • Added 1.4-GHz support

• Added GYP package support

• Added DSP_SUSP_CTL register section

• Updated Core Before IO Power Sequencing diagram, changing clock signal SYSCLK1P&N to REFCLK1P&N

• Updated the Trace timing diagram

• Updated Parameter Table Index bit field in I

2

C boot configuration

• Updated PKTDMA_PRI_ALLOC register to be CHIP_MSIC_CTL register with new bit field added.

• Updated OUTPUT_DIVIDE default value and PLL clock formula in PLL Settings section

• Updated Chip Select field description in SPI boot device configuration table

• Corrections applied to EMIF16 Boot Device Configuration Bit Fields

• Restored Parameter Information section

SPRS691D April 2013 • Added Initial Startup row for CVDD in Recommended Operating Conditions table

• Added DDR3PLLCTL1 and PASSPLLCTL1 registers to Device Status Control Registers table

• Added CVDD and SmartReflex voltage parameter in SmartReflex switching table

• Added HOUT timing diagram in Host Interrupt Output section

• Added MPU Registers Reset Values section

• Corrected PASSCLK(N/P) max cycle time from 6.4 ns to 25 ns

•Corrected Reserved to be Assert local reset to all CorePacs in LRESET and NMI decoding table

• Corrected PASS PLL clock to SRIOSGMIICLK in the boot device values table for Ethernet.

• Updated the Timer numbering across the whole document

• Updated DDR3 PLL initialization sequence

SPRS691C February 2012 • Added TeraNet connection figures and added bridge numbers to the connection tables

• Changed TPCC to EDMA3CC and TPTC to EDMA3TC

• Changed chip level interrupt controller name from INTC to CIC

• Added the DDR3 PLL and PASS PLL Initialization Sequence

• Added DEVSPEED Register section

• Updated device frequency in the feature section

• Corrected the SPI, DDR3, and Hyperbridge config/data memory map addresses

• Restricted Output Divide of SECCTL Register to max value of divide by 2

SPRS691B August 2011 • Updated the timing and electrical sections of several peripherals

• Updated the core-specific and general-purpose timer numbers

• Updated the connection matrix tables in chapter 4 “System Interconnection”

• Updated device boot configuration tables and figures

• Updated DDR3 and PASS PLL timing figures

• Removed section 7.1 “Parameter Information”

SPRS691A July 2011 • Added sections: NMI and LRSET

•Added Pin Map diagrams

• Added MAINPLLCTL1, DDR3PLLCTL1 and PAPLLCTL1 registers

• Changed PLL diagrams of MAIN PLL, DDR3 PLL and PASS PLL

• Changed C66x DSP System PLL Configuration table to include 1000 MHz and 1250 MHz columns

• Corrected items in the Memory Map Summary table

• Changed all occurrences of PA_SS to Network Coprocessor

• Updated the complete Power-up sequencing section. RESETFULL must always de-assert after POR

SPRS691 November 2010 Initial release

剩余246页未读,继续阅读

资源评论

sinat_40161574

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 【world bank wroup-2025研报】世界银行-经济快速增长但贫困隔离加剧:越南能否实现公平发展的可持续发展目标?(英).pdf

- 【Fortinet-2025研报】2025年网络威胁趋势预测报告.pdf

- 【世界银行-2025研报】能源价格、能源强度和企业绩效(英).pdf

- 【深交所-2025研报】粤高速B:2024年年度报告(英文版).pdf

- 【之诺咨询-2025研报】全球云计算市场研究系列2025年第一期.pdf

- 【莱坊-2025研究报告】Sydney CBD Office Market February 2025.pdf

- 【European Central Bank-2025研报】欧洲央行-欧洲与世界经济(英).pdf

- 【未来能源研究所-2025研报】建立技术绩效保险市场的政策(英).pdf

- 【艾瑞咨询-2025研报】iR-跨境出海行业周度市场观察-2025年第7周.pdf

- 【猎聘-2025研报】2025+AI技术人才供需洞察报告-猎聘.pdf

- 基于Spring Boot的在线拍卖系统设计与实现

- 信捷XC PLC与西门子V20变频器通讯程序:实现精准控制及状态指示,附触摸屏程序与详细设置指南,信捷XC PLC与西门子V20变频器通讯程序:实现精准控制及状态指示,附触摸屏程序与详细设置指南,信捷

- 全国各个省市区 json

- https://blog.csdn.net/cb181002/article/details/146073112?spm=1001.2014.3001.5501

- 起源视频播放器安装包,刚出炉不久的视频播放器

- 厦门大学智能信息检索实验数据

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功