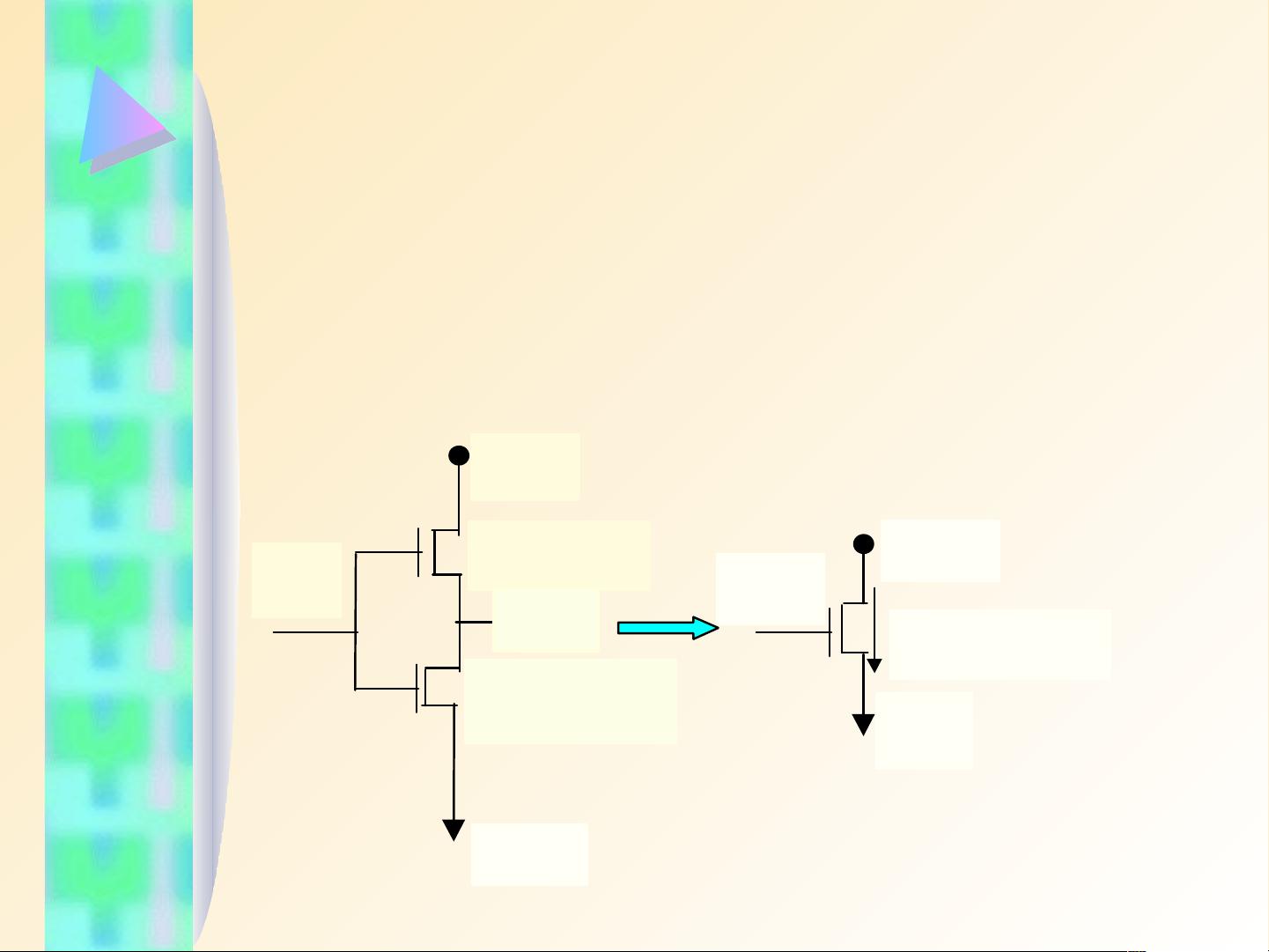

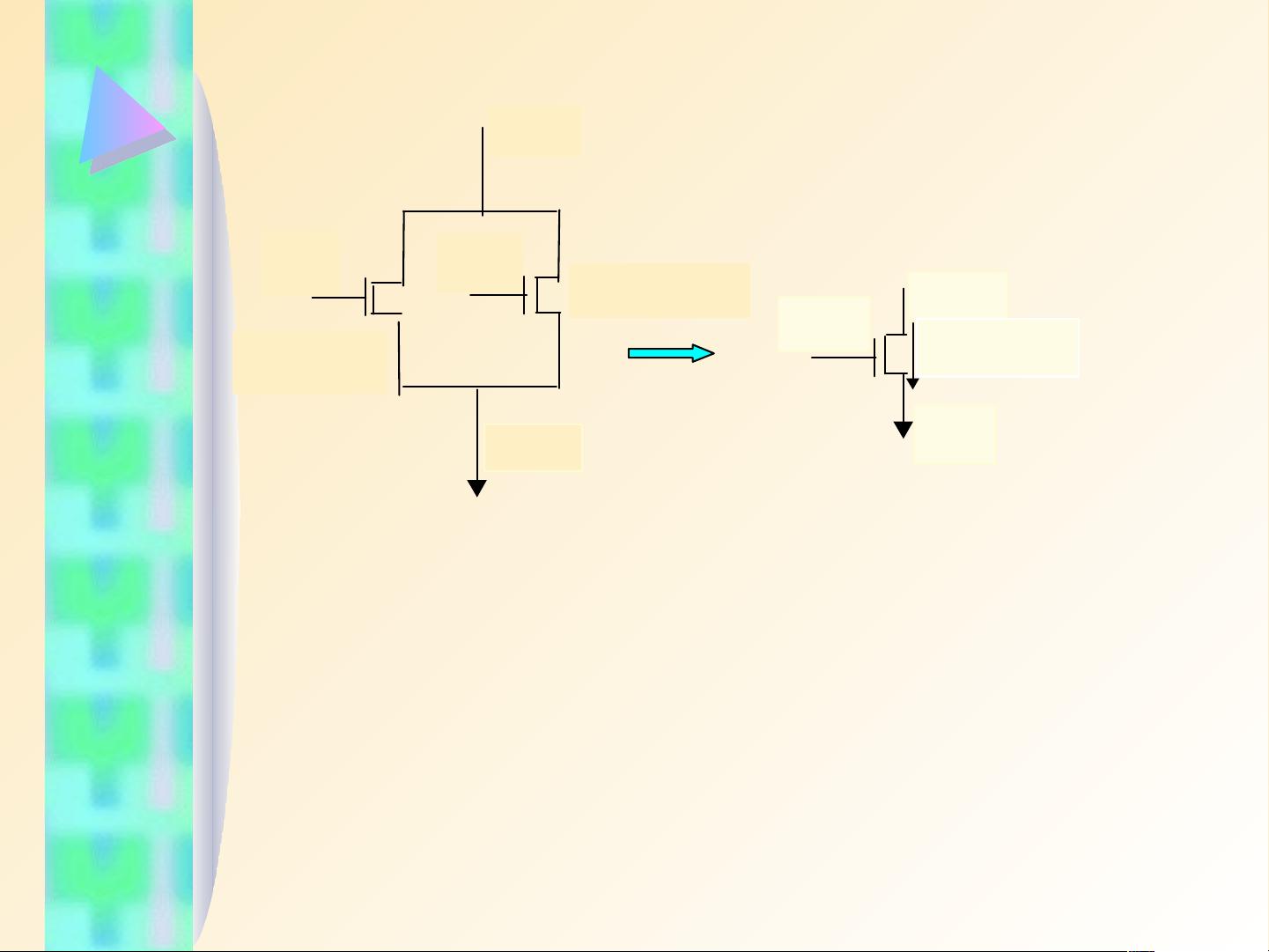

清华大学VLSI设计导论 本资源摘要信息来自清华大学VLSI设计导论课件第四章:逻辑设计技术。该章节主要介绍了MOS管的串、并联特性和逻辑门的实现。 第一节 MOS管的串、并联特性 在MOS管的串联和并联中,驱动能力是用其导电因子β来表示的,β值越大,其驱动能力越强。多个管子的串、并情况下,其等效导电因子应如何推导?在两管串联的情况下,等效导电因子可以用以下公式表示: βeff = β1 β2 / (β1 + β2) 在N个管子串联的情况下,等效导电因子可以用以下公式表示: βeff = β1 β2 … βN / (β1 + β2 + … + βN) 在两管并联的情况下,等效导电因子可以用以下公式表示: βeff = β1 + β2 在N个管子并联的情况下,等效导电因子可以用以下公式表示: βeff = β1 + β2 + … + βN 第二节 各种逻辑门的实现 逻辑门是数字电路的基本组成部分,包括与非门、或非门、与或非门等。这些逻辑门可以用MOS管来实现。 一、与非门 与非门的电路图如图所示。与非门的驱动能力可以用以下公式表示: βeffn = β’n / 2 βeffp = 2 β’p 在最坏的工作情况下,应使βeffp = β’p = βp,βeffn = β’n / 2 = βn 二、或非门 或非门的电路图如图所示。或非门的驱动能力可以用以下公式表示: βeffp = β’p / 2 βeffn = 2 β’n 在最坏的工作情况下,应使βeffp = β’p / 2 = βp,βeffn = β’n = βn 三、CMOS与或非门 CMOS与或非门的电路图如图所示。CMOS与或非门的驱动能力可以用以下公式表示: βeffp = β’p βeffn = β’n 在最坏的工作情况下,应使βeffp = β’p / 2 = βp,βeffn = β’n / 2 = βn 本章节介绍了MOS管的串、并联特性和逻辑门的实现,包括与非门、或非门和CMOS与或非门。这些知识点对于数字电路设计具有重要的参考价值。

剩余39页未读,继续阅读

- 粉丝: 3

- 资源: 10

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功