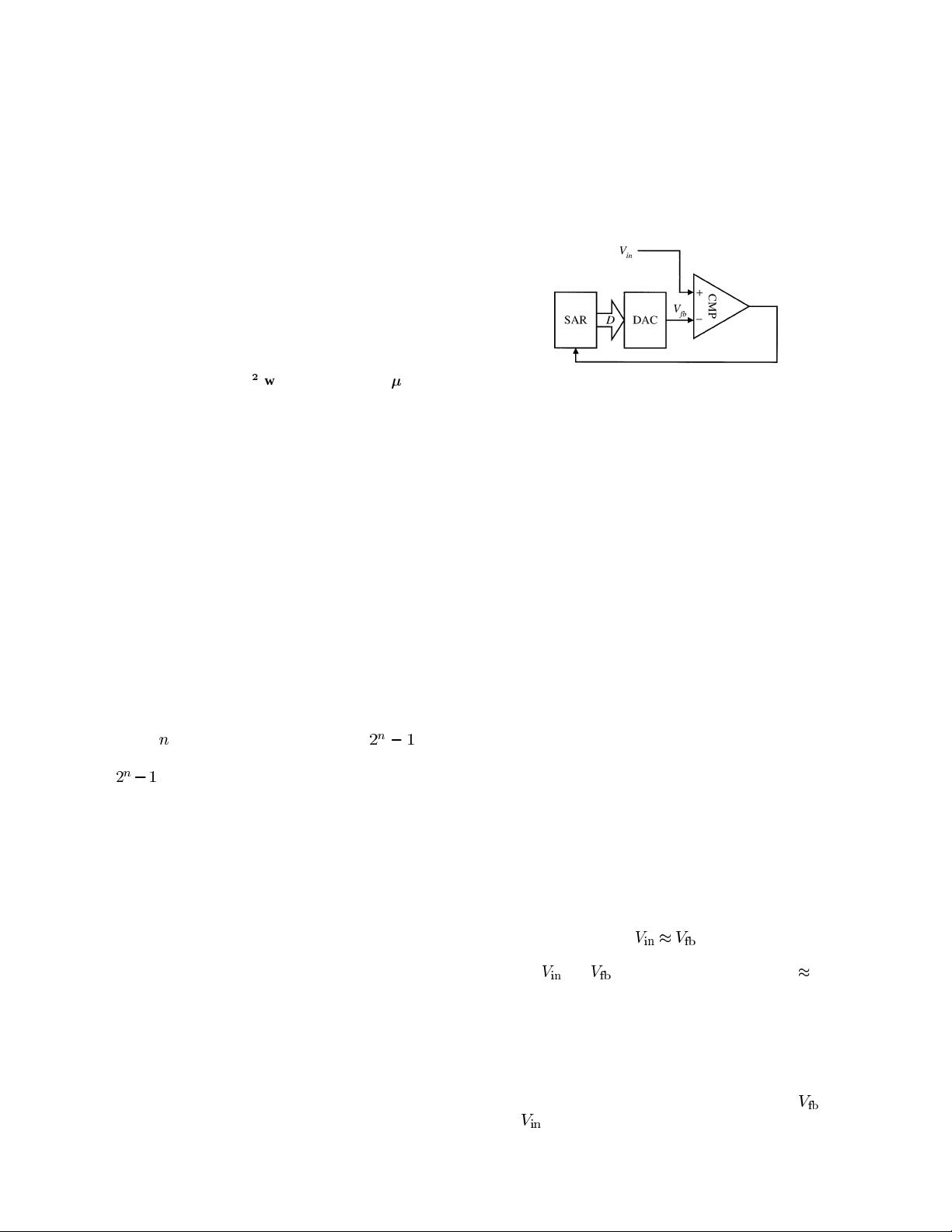

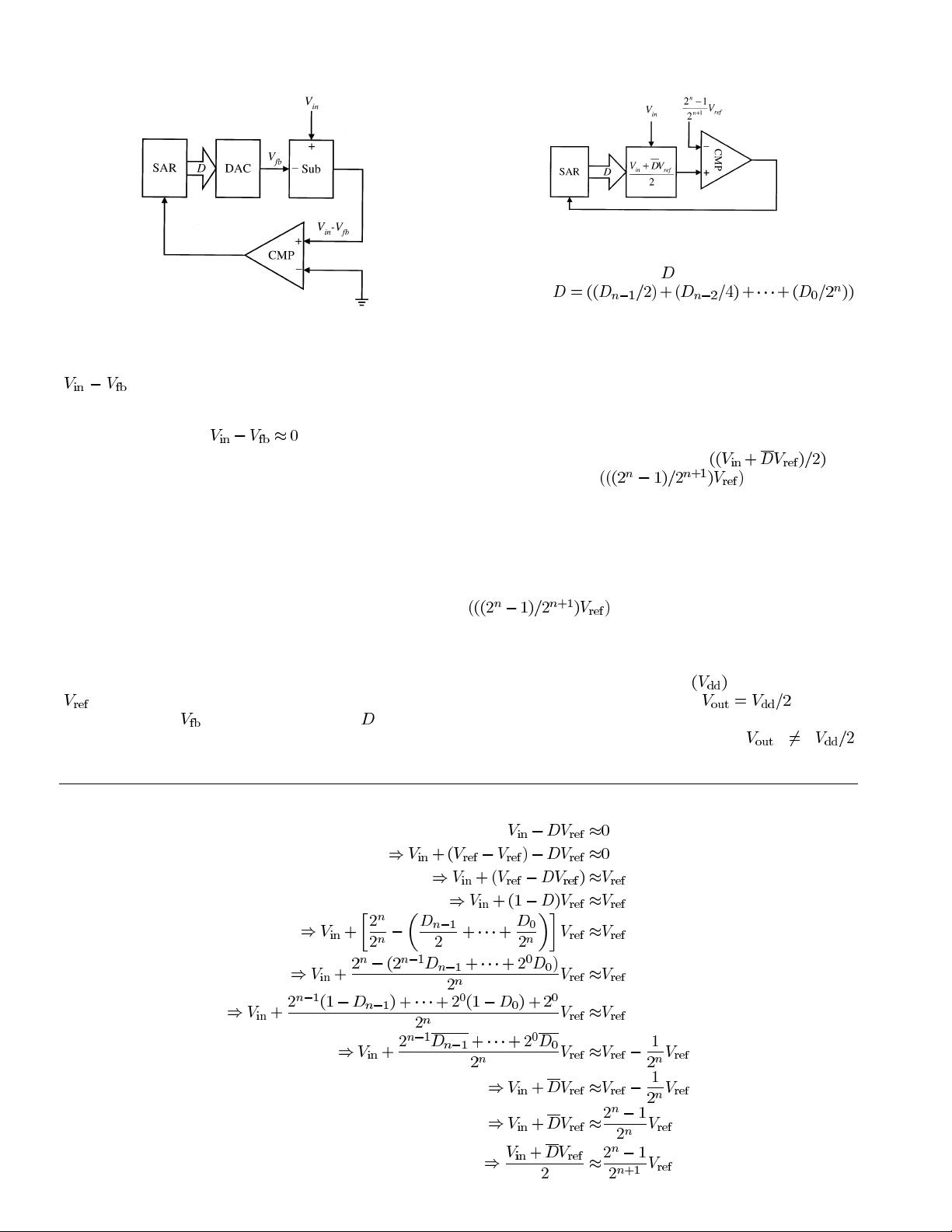

A new 6-bit 250 MS/s analog-to-digital converter (ADC) is proposed for low-power low-cost CMOS integrated systems. This design is based on an improved successive approximation ADC with a mixed-mode subtracter that minimizes the overall power consumption and system complexity. The experimental results indicate that this ADC works up to 250 MS/s with power consumption less than 30 mW at 3.3 V. Moreover, the operating voltage is scaled down to 0.8 V using a slight adjustment. The ADC occupies only 0.1 mm2 with the TSMC 0.35- m single ploy quadruple metal (SPQM) CMOS technology. This design is suitable for standard CMOS technology with low-power low-cost VLSI implementation. ### 一种新型6位250 MS/s模拟到数字转换器的设计与实现 #### 概述 本篇文章介绍了一种新型6位250 MS/s模拟到数字转换器(Analog-to-Digital Converter, ADC)的设计,该设计适用于低功耗、低成本的互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor, CMOS)集成系统。文章详细讨论了该ADC的设计原理、技术特点以及实验结果,并对其在低电压操作下的性能进行了评估。 #### 设计原理及技术特点 ##### 成功逼近型ADC架构 该ADC基于改进的成功逼近型ADC架构。成功逼近型ADC是一种常见的高速转换器,通过逐步逼近输入信号值来完成模数转换过程。本设计中的ADC采用了一种混合模式减法器(mixed-mode subtracter),该减法器能够在保持高转换速度的同时,显著降低整体功耗和系统复杂度。 ##### 混合模式减法器 混合模式减法器是该ADC的核心部分之一,它通过优化电路设计来减少功耗并简化系统结构。这种减法器结合了模拟和数字两种操作方式,在保证转换精度的同时降低了能量消耗。 ##### 低功耗与低成本 该ADC的设计目标是在保证高性能的前提下实现低功耗和低成本。通过优化电路结构和使用先进的制造工艺,使得该ADC能够在3.3 V电压下工作时的功率消耗低于30 mW,而且可以通过微调进一步将工作电压降至0.8 V,这对于电池供电的便携式设备尤其重要。 #### 实验结果与性能评估 实验结果显示,该ADC能够达到250 MS/s的采样速率,且在3.3 V电压下的功耗低于30 mW。此外,通过调整可以将工作电压降至0.8 V,这表明该ADC具有良好的电压适应性。整个转换器的尺寸仅为0.1 mm²,采用台积电0.35 μm单层多晶硅四层金属(Single Poly Quadruple Metal, SPQM)CMOS技术制造。这样的设计非常适合于标准CMOS技术下的低功耗、低成本超大规模集成电路(Very Large Scale Integration, VLSI)实现。 #### 应用场景与未来展望 由于其出色的性能指标,特别是低功耗和小尺寸特性,该ADC非常适合应用于对功耗敏感的便携式电子设备中,如移动电话、便携式媒体播放器等。同时,由于采用了标准的CMOS技术,该ADC还非常适合嵌入到系统级芯片(System-on-Chip, SoC)电路设计中,为现代电子产品的集成化提供了有力的支持。 #### 结论 本文介绍了一种基于改进成功逼近型ADC架构的新型6位250 MS/s模拟到数字转换器。该ADC通过采用混合模式减法器实现了低功耗、低成本的目标,并且在实验中展示了良好的性能。此外,该ADC还具备较低的工作电压范围,使其成为便携式电子设备的理想选择。未来,随着制造工艺的进步和技术的发展,这种类型的ADC有望在更多领域得到广泛应用。

剩余8页未读,继续阅读

- 粉丝: 0

- 资源: 2

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 大学生科创项目在线管理系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 本科设计基于java实现智能二维码门禁管理系统源码+论文(高分毕设)

- 毕业生实习与就业管理系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 3b030本科生就业推荐系统_springboot+vue0.zip

- 3b029.OA办公管理系统_springboot+vue0.zip

- 基于java的火车票订票系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于JAVA的房地产销售管理系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于Java web的药店管理系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 毕业就业信息管理系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 基于JavaWeb的鲜牛奶订购系统的设计与实现-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 洞见研报PingPong金融(跨境电商金融服务商,杭州乒乓智能技术有限公司)创投信息

- 车辆管理系统-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 高校专业实习管理系统的设计和开发-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

- 反欺诈平台的建设-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.zip

- 基于python+flask+postgreSQL技术设计并实现旅游数据可视化平台

- 火锅店管理系统-springboot毕业项目,适合计算机毕-设、实训项目、大作业学习.rar

信息提交成功

信息提交成功