没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

34页

Project2 VerilogHDL完成MIPS微系统开发(支持设备与中断) 一、设计说明 1.MIPS 微系统应包括:MIPS处理器、系统桥和 1 个定时器,32位输入设备、32 位输出设备。 2.MIPS处理器应实现MIPS-Lite3指令集。 a)MIPS-Lite3={MIPS-Lite2,ERET、MFC0、MTC0 }。 b)MIPS-Lite2={addu,subu,ori,lw,sw,beq,lui,addi,addiu,slt, j,jal,jr,lb,sb }。 c)addi应支持溢出,溢出标志写入寄存器$30中第0位。 3.MIPS处理器为多周期设计。 4.MIPS 微系统支持定时器硬件中断。 二、系统桥与设备 5.为了支持设备,MIPS 微系统需要配置系统桥。 a)需要支持 3 个设备,即定时器、32位输入设备、32 位输出设备。 b)定时器的设计规范请参看《定时器设计规范.docx》。 三、中断机制 6. 为了支持异常和中断,处理器必须实现 0 号协处理器(CP0)。为此,必须实现的CP0寄存器包括:SR、CAUSE、EPC、PrID。关于这几个寄存器,请大

资源推荐

资源详情

资源评论

计算机组成原理

课程设计报告

学 号____________________

姓 名____________________

指导教师___________________

提交日期_________________

成绩评价表

报告内容

报告结构

报告最终成绩

□丰富正确

□基本正确

□有一些问题

□问题很大

□完全符合要求

□基本符合要求

□有比较多的缺陷

□完全不符合要求

报告与 Project 功能一致性

报告图表

总体评价

□完全一致

□基本一致

□基本不一致

□符合规范

□基本符合规范

□有一些错误

□完全不正确

教师签字:____

目录

Project1 VerilogHDL 完成多周期处理器开发 ...................................................................................4

一、 数据通路结构设计图 .....................................................................................................................4

二、 模块描述..........................................................................................................................................4

(一)pc 模块 ..................................................................................................................................4

(二) npc 模块定义 ......................................................................................................................5

(三) im 模块定义 ........................................................................................................................6

(四) ir 模块定义..........................................................................................................................6

(五) gpr 模块定义.......................................................................................................................7

(六) alu 模块定义 .......................................................................................................................7

(七) ext 模块定义 .......................................................................................................................8

(八) dm 模块定义 .......................................................................................................................9

(九) controller 模块定义 ............................................................................................................9

(十) mux3_1 模块定义 .............................................................................................................10

(十一) mux323_1 模块定义 .....................................................................................................11

(十二) 寄存器模块 ...................................................................................................................11

三、 机器指令描述 ...............................................................................................................................12

四、测试程序..........................................................................................................................................14

五、测试运行结果 .................................................................................................................................15

六、 实验收获总结 ...............................................................................................................................16

Project 3 VerilogHDL 完成 MIPS 微系统开发 (支持设备与中断) ..............................................16

一、总体数据通路结构设计图 .............................................................................................................17

二、 模块描述........................................................................................................................................17

(一)pc 模块 ................................................................................................................................17

(二)npc 模块定义 ......................................................................................................................18

(三)im 模块定义 ........................................................................................................................19

(四) ir 模块定义........................................................................................................................19

(五) GPR 模块定义 ...................................................................................................................19

(六) ALU 模块定义....................................................................................................................20

(七) EXT 模块定义 ....................................................................................................................20

(八) DM 模块定义 ....................................................................................................................20

(九) controller 模块定义 ..........................................................................................................20

(十) CP0 模块 ............................................................................................................................21

(十一) Bridge 模块定义...............................................................................................................22

(十二)Timer 模块定义...............................................................................................................22

(十三) out 模块定义.................................................................................................................23

(十四) in 模块定义 ...................................................................................................................24

(十五) 寄存器模块 ...................................................................................................................24

(十六) 选择器模块 ...................................................................................................................24

三、 机器指令描述 ...............................................................................................................................24

四、 测试程序........................................................................................................................................24

j stop ................................................................................................................................................25

五、 测试运行结果 ...............................................................................................................................25

六、 实验收获总结 ...............................................................................................................................26

Project1 VerilogHDL 完成多周期处理器开发

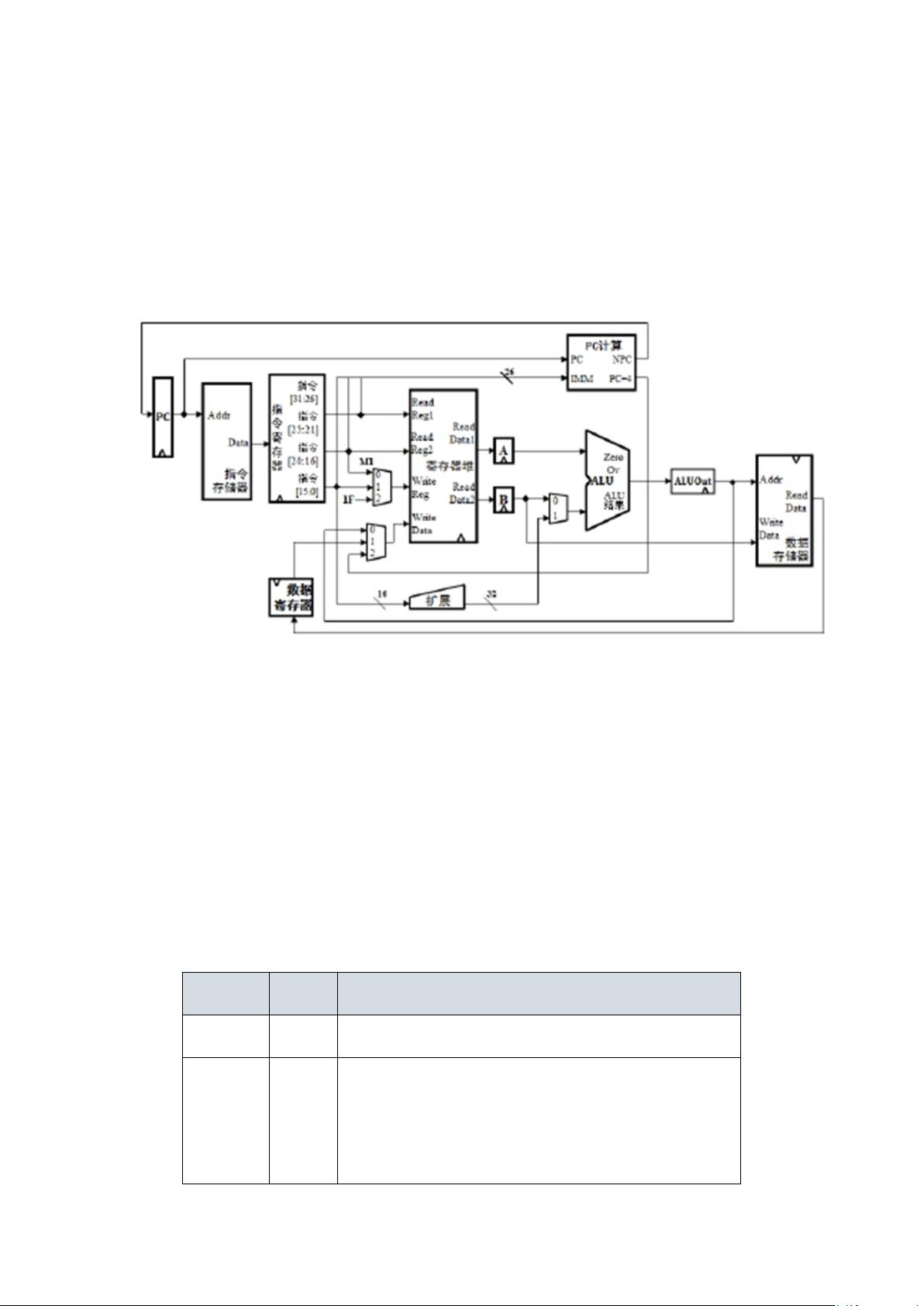

一、数据通路结构设计图

二、模块描述

(一)pc 模块

(1) 基本描述

上升沿到来的时候,若写使能有效,改变 pc 的值。

(2) 模块接口

信号名

方向

描述

clk

I

时钟信号

reset

I

复位信号

1:复位

0:不复位

剩余33页未读,继续阅读

资源评论

寒铗2024-04-29支持这个资源,内容详细,主要是能解决当下的问题,感谢大佬分享~

寒铗2024-04-29支持这个资源,内容详细,主要是能解决当下的问题,感谢大佬分享~

shcnb

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于java+MapReduce实现基于物品协同过滤算法,即电影推荐系统+源码+开发文档+算法解析(毕业设计&课程设计&项目开发

- 节点编程(整合所有节点编程代码).7z

- 企业发卡系统源码蓝色UI模板+商户+手机端+对接易支付接口版(无需授权)

- 基于java+Mahout实现协同过滤推荐算法的电影推荐系统+源码(毕业设计&课程设计&项目开发)

- 基于TC72(SPI接口)温度传感器、STM32F103C8T6、LCD1602、FREERTOS的温度采集proteus仿真

- postgresql-42.7.3.jar

- 2024-05-21 20-36-43.mkv

- 基于QT+C++的智能云监护仪项目,能够实时显示使用者心电、血氧、血压波形及其它各种参数+源码(毕业设计&课程设计&项目开发)

- 基于java开发的app接收硬件端传输的心音信号,具有显示心音波形,发出心音的功能+源码(毕业设计&课程设计&项目开发)

- Python 程序语言设计模式思路-行为型模式:职责链模式:将请求从一个处理者传递到下一个处理者

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功