没有合适的资源?快使用搜索试试~ 我知道了~

### 视频连接技术:利用TMDS I/O实现视频传输

#### 概述

过渡最小化差分信号(Transition Minimized Differential Signaling,简称TMDS)是一种用于通过数字视觉接口(Digital Visual Interface,简称DVI)和高清晰度多媒体接口(High-Definition Multimedia Interface,简称HDMI)传输视频数据的标准。这两种接口广泛应用于消费电子设备,如平板电视、个人电脑显示器、DVD播放器、台式机以及视频游戏控制台等。

#### 引言

DVI和HDMI协议在物理层使用TMDS进行通信。TMDS的吞吐量取决于所传输视频屏幕模式的串行数据速率,这反过来又决定了用于支持该吞吐量的Spartan-3A FPGA的速度等级。

#### FPGA吞吐量与视频屏幕模式

Spartan-3A FPGA集成了原生TMDS I/O,并符合差分电压标准。表1列出了每种Spartan-3A FPGA速度等级的最大吞吐量,而表2则列举了对应这些数据速率的常见视频屏幕模式。

**表1:Spartan-3A系列TMDS I/O吞吐量**

| 速度等级 | 吞吐量 |

|----------|----------|

| -5 | 700 Mb/s |

| -4 | 640 Mb/s |

**表2:常见视频屏幕模式**

| 屏幕模式 | 像素速率 | 串行数据速率 | 颜色深度 |

|-------------------|----------|-------------|----------|

| VGA (640x480@60Hz)| 25 MHz | 250 Mb/s | 24 bits |

| 480p (720x480@60Hz)| 27 MHz | 270 Mb/s | 24 bits |

| SVGA (800x600@60Hz)| 50 MHz | 500 Mb/s | 24 bits |

| XGA (1024x768@60Hz)| 65 MHz | 650 Mb/s | 24 bits |

| HDTV 720p (1280x720@60Hz)| 74.25 MHz | 742.5 Mb/s | 24 bits |

| HDTV 1080i (1920x1080@60Hz交错)| 74.25 MHz | 742.5 Mb/s | 24 bits |

**注释**:

1. 符合CEA-861-D标准。

#### TMDS视频传输协议

本节简要讨论了TMDS视频传输协议。TMDS通过差分对传输数据,这种设计可以最大限度地减少电磁干扰并提高信号质量。TMDS使用三个独立的数据通道来传输像素数据,以及一个额外的时钟/控制通道来同步这三个数据通道。每个数据通道通常支持高达3.4 Gbps的数据速率,这意味着一个完整的HDMI 1.4b信号可以达到约10.2 Gbps的总带宽。

TMDS信号传输采用8b/10b编码方案,这是一种将8位数据转换为10位符号的技术,旨在减少直流偏置和改善信号的传播特性。此外,TMDS还采用了特殊符号序列,这些序列被插入到数据流中以帮助接收端恢复时钟信号。

为了实现视频连接功能,Spartan-3A FPGA提供了一套参考设计,能够支持最高达700 Mb/s的数据流传输与接收,这适用于许多常见的视频格式,包括VGA、SVGA、XGA以及一些高清视频模式如HDTV 720p和1080i。

利用TMDS I/O接口,Spartan-3A FPGA能够在保持高质量视频信号的同时,提供高性能且经济高效的视频连接解决方案。对于那些希望在不牺牲图像质量的情况下降低成本的应用场景来说,这种集成的TMDS I/O接口是一个非常有价值的选择。

### 结论

通过使用Spartan-3A FPGA中的原生TMDS I/O接口,设计人员可以轻松实现DVI或HDMI数据流的传输和接收,同时确保视频质量和性能。这一技术不仅简化了设计过程,还降低了成本,并为消费电子产品提供了高质量的视频连接选项。

XAPP460 (v1.1) June 24, 2011 www.xilinx.com 1

© Copyright 2008–2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are

trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

Summary Transition Minimized Differential Signaling (TMDS) is a standard used for transmitting video

data over the Digital Visual Interface (DVI) and High-Definition Multimedia Interface (HDMI).

Both interfaces are commonly used by consumer electronics including flat panel TVs, PC

monitors, DVD players, PC desktops, and video game consoles.

This application note describes a set of reference designs able to transmit and receive DVI or

HDMI data streams up to 700 Mb/s using the native TMDS I/O interface featured by

Spartan®-3A FPGAs.

Introduction The DVI and HDMI protocols use TMDS at the physical level. TMDS throughput is a function of

the serial data rate of the video screen mode being transmitted. This in turn determines the

Spartan-3A FPGA speed grade that must be used to support this throughput.

FPGA Throughput and Video Screen Modes

Spartan-3A FPGAs feature native TMDS I/O with compliant differential voltage standards.

Table 1 shows the maximum throughput for each Spartan-3A FPGA speed grade.

Common video screen modes corresponding to these data rates are listed in Table 2.

Application Note: Spartan-3A Family

XAPP460 (v1.1) June 24, 2011

Video Connectivity Using TMDS I/O in

Spartan-3A FPGAs

Author: Bob Feng and Eric Crabill

Table 1: Spartan-3A Family TMDS I/O Throughput

Speed Grade Throughput

-5 700 Mb/s

-4 640 Mb/s

Table 2: Common Video Screen Modes

Screen Mode Pixel Rate

Serial Data

Rate

Color Depth

VGA (640x480@60 Hz) 25 MHz 250 Mb/s 24 bits

480p

(1)

(720x480@60 Hz) 27 MHz 270 Mb/s 24 bits

SVGA (800x600@60 Hz) 50 MHz 500 Mb/s 24 bits

XGA (1024x768@60 Hz) 65 MHz 650 Mb/s 24 bits

HDTV 720p

(1)

(1280x720@60 Hz) 74.25 MHz 742.5 Mb/s 24 bits

HDTV 1080i

(1)

(1920x1080@60 Hz interlaced) 74.25 MHz 742.5 Mb/s 24 bits

Notes:

1. Per CEA-861-D [Ref 1].

Introduction

XAPP460 (v1.1) June 24, 2011 www.xilinx.com 2

TMDS Video Transmission Protocols

This section briefly discusses the TMDS video transmission protocols. Detailed information is

available in these documents:

• A DTV Profile for Uncompressed High Speed Digital Interfaces

[Ref 1]

• Digital Visual Interface, Revision 1.0 [Ref 2]

• High-Definition Multimedia Interface Specification, Version 1.3a [Ref 3]

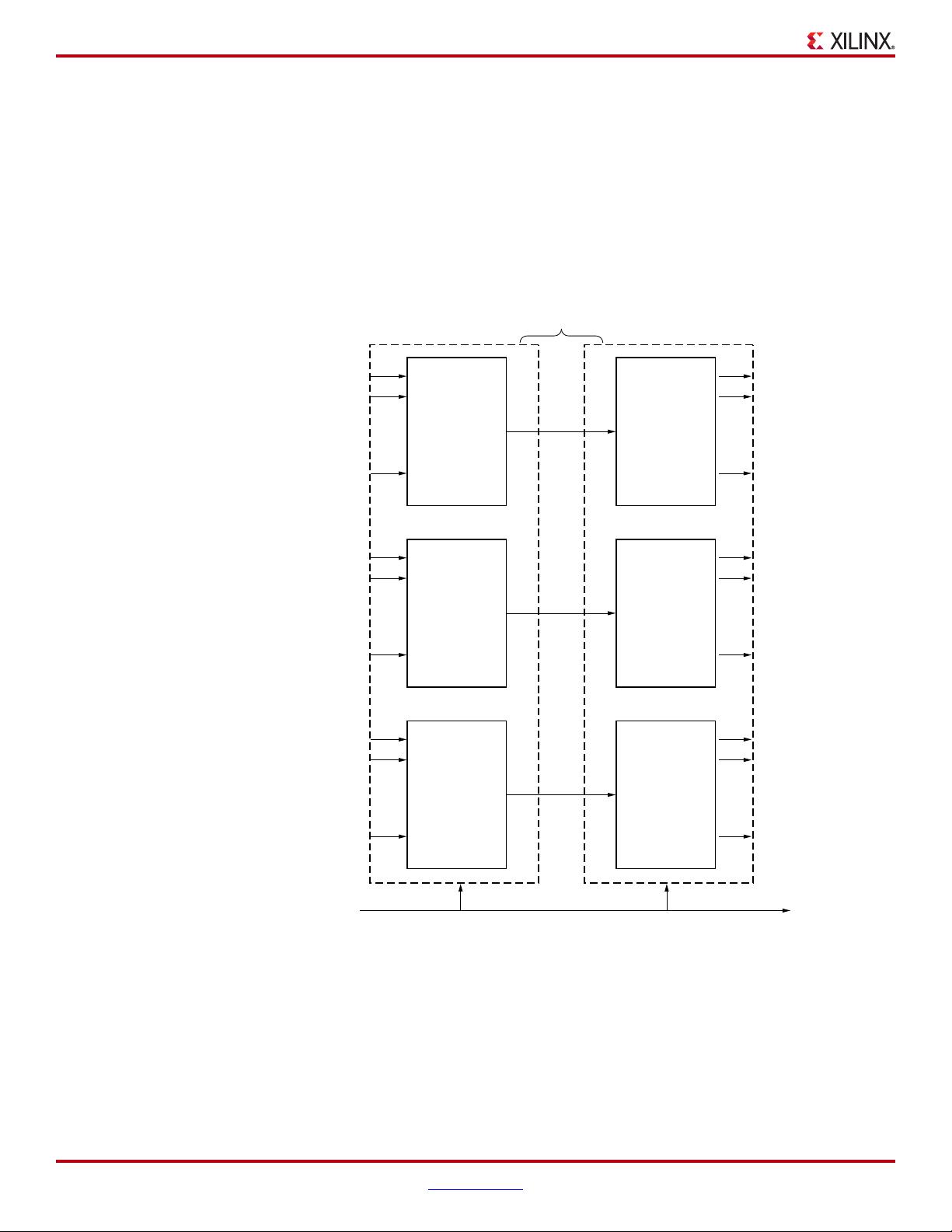

Figure 1 shows the topology for an established TMDS link between the transmitter (Source)

and receiver (Sink).

Four channels of serial data establish a single link of DVI or HDMI video transmission. In DVI,

three channels are designated for the red, green, and blue color components (RGB 4:4:4) in

each video pixel data. HDMI also uses three RGB channels by default, but they also can be

optionally used to carry Luminance and Chrominance components (YCrCb 4:4:4 and YCrCb

4:2:2). The fourth channel transmits a clock toggling at the pixel data rate.

For a pixel having 24-bit color depth, each color component originates as 8-bit data, which is

then is converted into a 10-bit symbol using an 8B/10B encoding scheme. The 10-bit symbol is

then serialized and transmitted onto one of the TMDS data channels. This 10:1 serialization

ratio results in a 10x faster bit rate than the actual pixel rate.

X-Ref Target - Figure 1

Figure 1: TMDS Link Topology

Source

Channel 0

Encoder/

Serializer

TMDS Link

Clock Channel

Pixel Clock

Channel 0

Deserializer/

Decoder

Channel 1

Encoder/

Serializer

Channel 1

Deserializer/

Decoder

Channel 2

Encoder/

Serializer

Channel 2

Deserializer/

Decoder

Sink

D[7:0]

D[1:0]

D[3:0]

(HDMI Only)

D[7:0]

D[1:0]

D[3:0]

(HDMI Only)

D[7:0]

D[1:0]

D[3:0]

D[7:0] Pixel Data, Blue

HSYNC, VSYNC

Auxiliary Data

(Audio Header)

Pixel Data, Green

CTL0, CTL1

Auxiliary Data

(Audio Packet)

Pixel Data, Red

CTL2, CTL3

Auxiliary Data

(Audio Packet)

Pixel Data, Blue

HSYNC, VSYNC

Auxiliary Data

(Audio Header)

Pixel Data, Green

CTL0, CTL1

Auxiliary Data

(Audio Packet)

Pixel Data, Red

CTL2, CTL3

Auxiliary Data

(Audio Packet)

X460_01_062008

D[1:0]

D[3:0]

D[7:0]

D[1:0]

D[3:0]

D[7:0]

D[1:0]

D[3:0]

(HDMI Only)

(HDMI Only)

(HDMI Only)

(HDMI Only)

Logic Construct

XAPP460 (v1.1) June 24, 2011 www.xilinx.com 3

During the video frame transmission, the active pixel symbol is periodically interlaced with four

distinct control tokens representing blanking intervals. These control tokens provide accurate

video line scan (HSYNC) and frame update (VSYNC) information. Control tokens are also used

to identify word boundaries for synchronization purposes.

For DVI transmission, the full video blanking period is used only to transmit control tokens. An

HDMI transmission also defines a Data Island in the blanking period to transmit packets of

audio data and auxiliary data. The auxiliary data includes InfoFrames and other descriptive

data. This is the main difference between the two protocols.

Logic Construct This section describes the use of the Spartan-3A family's built-in resources to construct a soft

DVI/HDMI transceiver. The transmitter and the receiver designs are covered separately.

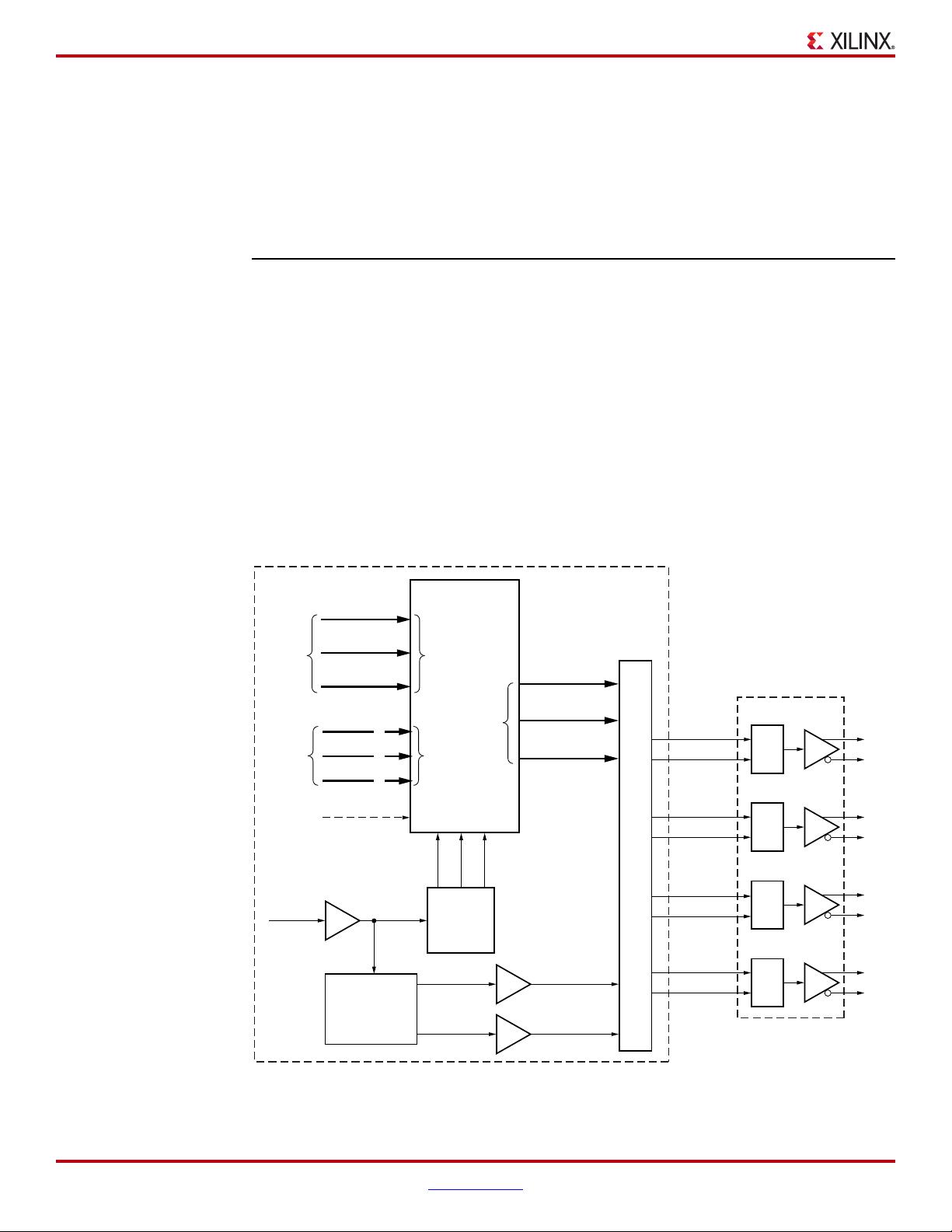

Transmitter Design

Video transmission over the TMDS link is logically divided into an encoder and serializer stage

as illustrated in Figure 2. The encoders convert pixel data from a video source, HDMI

Auxiliary/Audio data, and HSYNC and VSYNC into three 10-bit symbol streams. The serializer

performs a parallel-to-serial conversion on all three streams and then sends them out onto

three channels of differential output pairs. The serialization ratio is 10:1 per channel.

Figure 2 also shows how the transmitter is physically implemented, with the design of the

encoder and serializer logic located in the FPGA logic while the dedicated I/O Block (IOB)

contains the ODDR2 double data rate output registers and the TMDS differential output buffers.

h

X-Ref Target - Figure 2

Figure 2: TMDS Transmitter

X460_02_070908

IOB

FPGA Logic

RED[7:0]

BLUE[7:0]

GREEN[7:0]

AUX0[3:0]

AUX2[3:0]

AUX1[3:0]

RED[9:0]

BLUE[9:0]

GREEN[9:0]

VDE

HSYNC

VSYNC

CLK_P

CLK_N

RED_P

RED_N

GRN_P

GRN_N

BLU_P

BLU_N

R+

R-

G+

G-

B+

B-

CLK+

CLK-

ADE

PCLKx5

PCLKx5not

Video

Source

HDMI

Aux &

Audio

Data

30:3 Serializer

ODDR2 ODDR2ODDR2 ODDR2

TMDS

TMDS

TMDS

TMDS

BUFG

BUFG

BUFG

Encoders

TERC4 (4 bits)

10 bits out

TMDS (8 bits)

CTRL (2 bits)

Video

Timing

Controller

DCM

Logic Construct

XAPP460 (v1.1) June 24, 2011 www.xilinx.com 4

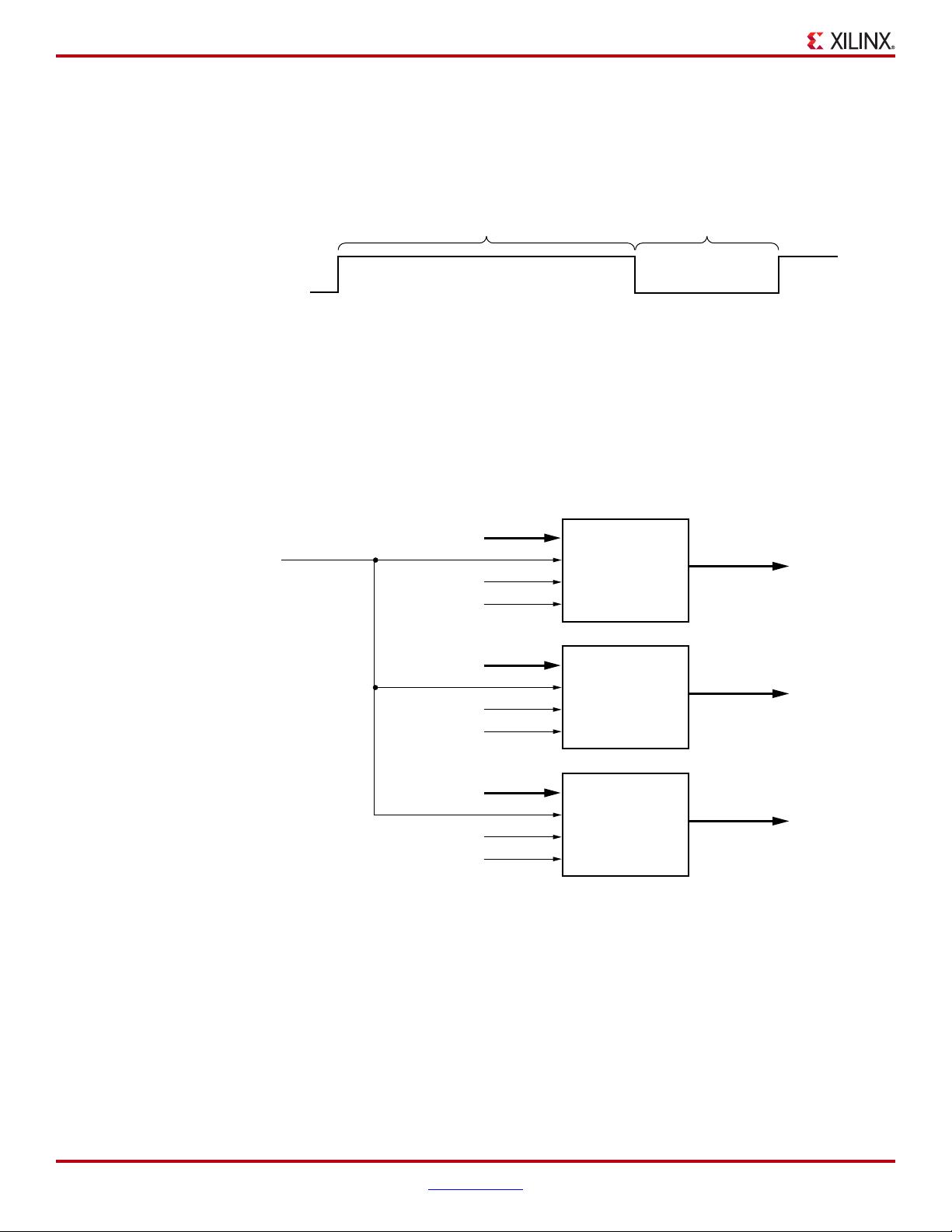

DVI Encoder

The DVI encoder outputs pixel data during the active video period and control data during the

blanking period. Figure 3 shows the relationship of Video Data Enable (VDE) to these two

states. VDE, HSYNC, and VSYNC are generated by the Video Timing Controller shown in

Figure 2.

Figure 4 shows the encoder layout for all three channels. The encoder logic is identical for all

three pixel components. The state of VDE defines the active video and the blanking periods

and enables the output of either video pixel data or control data. HSYNC and VSYNC are

encoded on the blue channel for transmission during the blanking period. Control signals C0

and C1 are encoded and output during the blanking period on the green and red channels. The

DVI specification reserves the use of control symbols C0 and C1, so these are a value of

2'b00 at the input of each encoder.

The incoming video pixel values for each channel are encoded using the TMDS encoding

algorithm defined in the DVI specification. Each 8-bit value is converted into one of 460 unique

10-bit symbols. This encoding scheme serves to achieve an approximate DC balance and limit

the number of state transitions to five or fewer per symbol.

The status of the 2-bit control bus for each channel is transmitted during the video blanking

period. This data is represented by four distinct 10-bit control tokens predefined as:

10'b1101010100, 10'b0010101011, 10'b0101010100, and 10'b1010101011. Each

token has seven or more state transitions. The difference in the number of state transitions

between video symbols and control tokens will be used to synchronize the transmitting and

receiving devices.

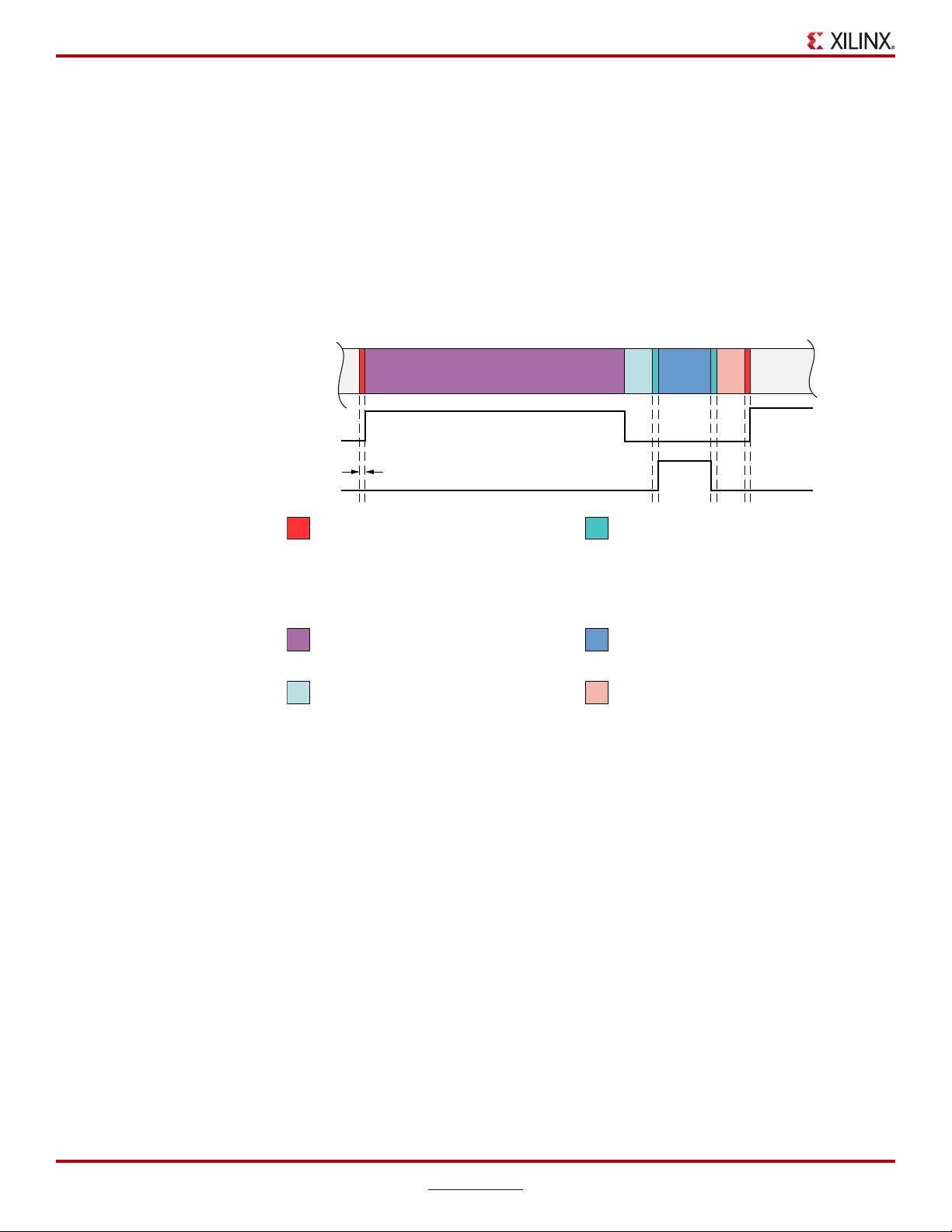

X-Ref Target - Figure 3

Figure 3: DVI Encoding Scheme

X-Ref Target - Figure 4

Figure 4: DVI Encoder Layout

X460_03_070908

VDE

Active Pixels

Each pixel represented with one

of 460 unique TMDS Symbols

Control Tokens Only

X460_04_071008

BLUE[9:0]

BLUE[7:0]

HSYNC

VDE

VSYNC

8B/10B

2B/10B

Encoder

C0

C1

GREEN[9:0]

GREEN[7:0]

C0=0

C0=0

8B/10B

2B/10B

Encoder

C0

C1

RED[9:0]

RED[7:0]

C0=0

C1=0

8B/10B

2B/10B

Encoder

C0

C1

Logic Construct

XAPP460 (v1.1) June 24, 2011 www.xilinx.com 5

HDMI Encoder

The HDMI protocol is derived from and shares many aspects with the DVI protocol, including

the physical TMDS link, the active video encoding algorithm, and the control token definitions.

HDMI carries much more data than DVI by transmitting auxiliary data (InfoFrames) and audio

data during the video blanking period. Figure 5 shows the HDMI encoding scheme for video

and audio data relative to VDE and Aux/Audio Data Enable (ADE).

The HDMI encoder converts each 8-bit pixel component into one of 460 unique 10-bit symbols

using an encoding algorithm similar to the one used by the DVI specification. A representative

flowchart describing this algorithm is shown in the HDMI 1.3 specification.

The information contained in each segment of the HDMI data stream is described in the

following paragraphs.

Active Video Data. Video pixels are encoded using the same algorithm used by DVI. Each

8-bit pixel component is converted into one of the 460 unique 10-bit symbols. A similar process

flow chart is illustrated on page 82 in HDMI specification, version 1.3.

Data Island Preamble. An advanced indication that the Data Island period (containing audio

samples and InfoFrames) will follow. Contains eight identical, consecutive control tokens on the

green and red channels only.

Data Island Guardband (Leading). Provides design with a means of synchronization between

transmitter and receiver. Guardband has a 2 pixel duration.

Active Aux/Audio Data. Auxiliary data (InfoFrame) and audio data encoded as 10-bit TERC4

symbols. The TERC4 encoding scheme consists of 16 unique 10-bit characters converted from

4-bit auxiliary or audio data. Transmitted on the green and red channels only.

X-Ref Target - Figure 5

Figure 5: HDMI Encoding Scheme

X460_05_071108

Video Preamble

Video Guardband

Data Island Guardband

Data Island Guardband

Video Guardband

Active Aux/Audio Data

Active Video Data

Data Island Preamble

Guardband duration = 2 Pixels

Video Guardband =>

Active Video Data (TMDS Code)

Active Aux/Audio Data (TERC4 code)

Video Preamble =>

Data Island Preamble =>

Data Island Guardband =>

case (TMDS Channel Number):

0:q_out[9:0] = 0b10 11 00 1100;

1:q_out[9:0] = 0b0 1 0011 00 11;

2:q_out[9:0] = 0b10 11 00 11 00;

endcase

case (TMDS Channel Number):

0:q_out[9:0] = n.a.;

1:q_out[9:0] = 0b0 1 0011 00 11;

2:q_out[9:0] = 0b0 1 00 1100 11;

endcase

{c3, c2, c1, c0} = 4’b0101 {c3, c2, c1, c0} = 4’ b0001

VDE

ADE

剩余35页未读,继续阅读

资源推荐

资源评论

2012-02-22 上传

2019-01-11 上传

2020-06-17 上传

2021-11-15 上传

110 浏览量

165 浏览量

2020-09-24 上传

2015-10-19 上传

193 浏览量

183 浏览量

2020-04-10 上传

186 浏览量

189 浏览量

175 浏览量

2020-10-16 上传

130 浏览量

167 浏览量

143 浏览量

112 浏览量

2010-09-04 上传

114 浏览量

112 浏览量

资源评论

shaouxyz

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- matlab平台的的PCB板缺陷检测.zip

- matlab平台的的SVM方法的水果识别分类.zip

- matlab平台的的答题纸答题卡识别.zip

- matlab平台的的病虫害检测系统.zip

- 基于python的多传感器数据融合故障诊断程序,三条分支

- sgp4与sdp4模型文档+一个SGP4的开源实现

- matlab平台的的车道线标定.zip

- matlab平台的的人脸+指纹融合系统.zip

- matlab平台的的路牌交通牌照识别.zip

- JAVA多线程示例代码

- matlab平台的的人脸门禁预警.zip

- matlab平台的的手写汉字识别.zip

- matlab平台的的人脸识别设计.zip

- matlab平台的的视频图像去雾.zip

- matlab平台的的手写字符识别.zip

- matlab平台的的小波变换dwt数字水印.zip

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功