Quartus II 11.0 仿真

Quartus II 是 Altera 公司开发的一款 FPGA 设计软件,提供了 complete digital circuit design flow,从设计、仿真、编译到下载。在这个过程中,仿真工具 ModelSim 扮演着非常重要的角色。本文将简单介绍 Quartus II 中自带仿真工具 ModelSim 的使用。

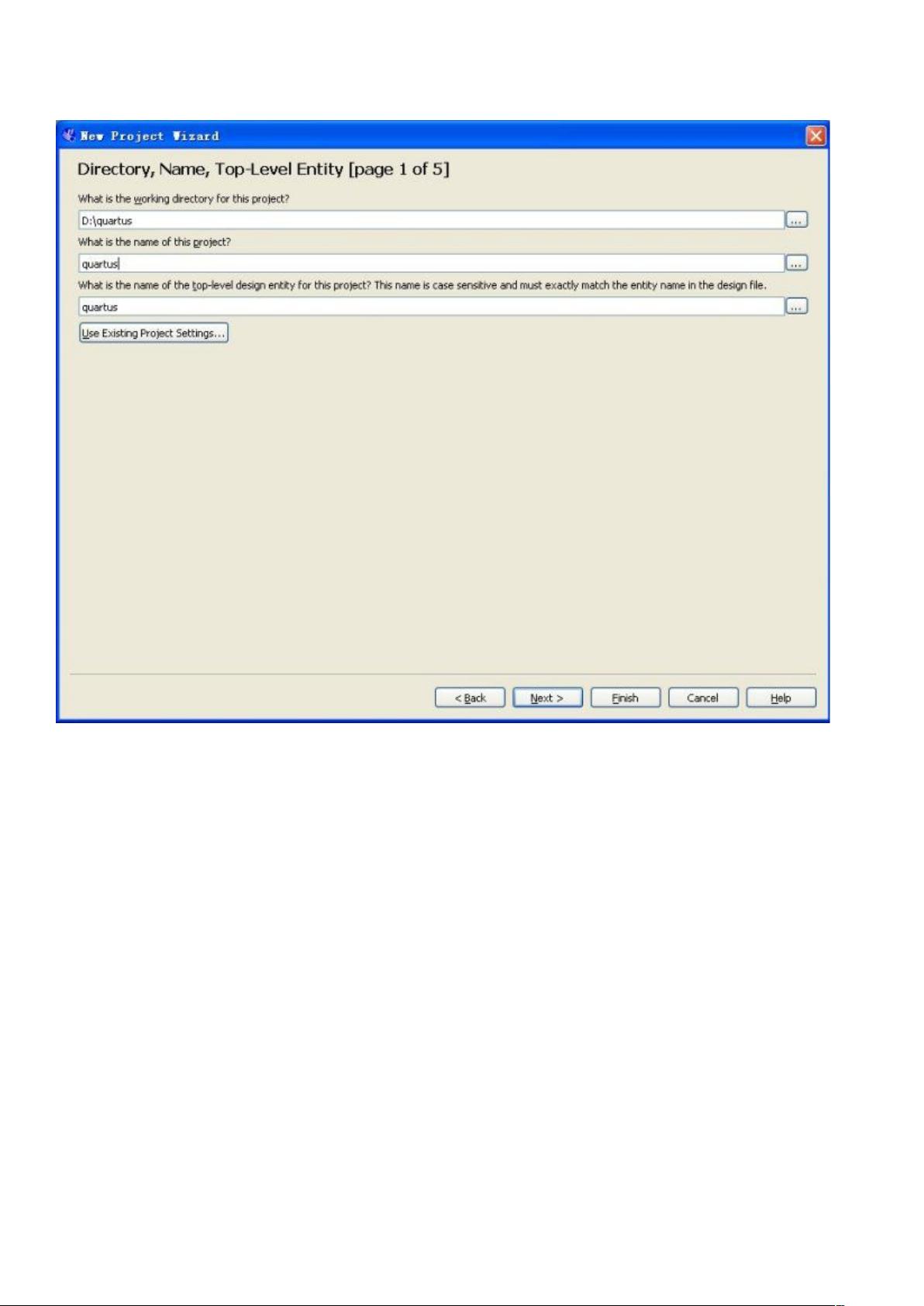

一、创建新工程

需要创建一个新的工程。点击“ NEXT”,输入保存目录和项目名称,然后点击“ NEXT”。如果已经存在文件,可以浏览并添加,如果没有,直接点击“ NEXT”。然后,选择器件,可以让软件自动选择,也可以自己指定。选择仿真软件,这一步可以跳过,后面可以设置。最终点击“ Finish” 即可。

二、加入文件

加入文件,点击“新建文件”,这里我们使用 Verilog HDL。输入代码并保存,模块名要与保存的文件名称相同,否则编译报错。输入完成后点击编译,编译完成后显示报告。

三、编写测试平台(Testbench)

编写测试平台(Testbench),输入文件还是 Verilog HDL,只不过在保存的时候把后缀名改为“.vt”。点击“ Assignments-Settings-Simulation”,tool name 选 ModelSim-Altera,Format for output netlist 选择 Verilog HDL,Time scale 选择 1ns(可以根据自己需要调整),点击 apply。

四、设置测试文件

点击“ Processing-Start-Start Test Bench Template Writer”,完成后,需要加入测试文件。在 Test bench Name 和 Top level module in test bench 中输入与之前写的 testbench 模块名相同的名称,然后在 Test bench files 里浏览文件并点击 Add。

五、启动 ModelSim仿真

所有操作完成后,点击“ Tools-Run EDA Simulation Tool-EDA RTL Simulation ”启动 ModelSim 进行功能仿真。

在整个过程中,ModelSim扮演着非常重要的角色。它可以模拟 FPGA 的行为,让设计人员可以在不需要实际 FPGA 硬件的情况下对设计进行测试和验证。同时,ModelSim 还可以与 Quartus II 集成,提供了一个完整的设计流程。

Quartus II 11.0 仿真提供了一个功能强大且灵活的仿真环境,让设计人员可以更方便、更快速地设计和验证 FPGA 设计。