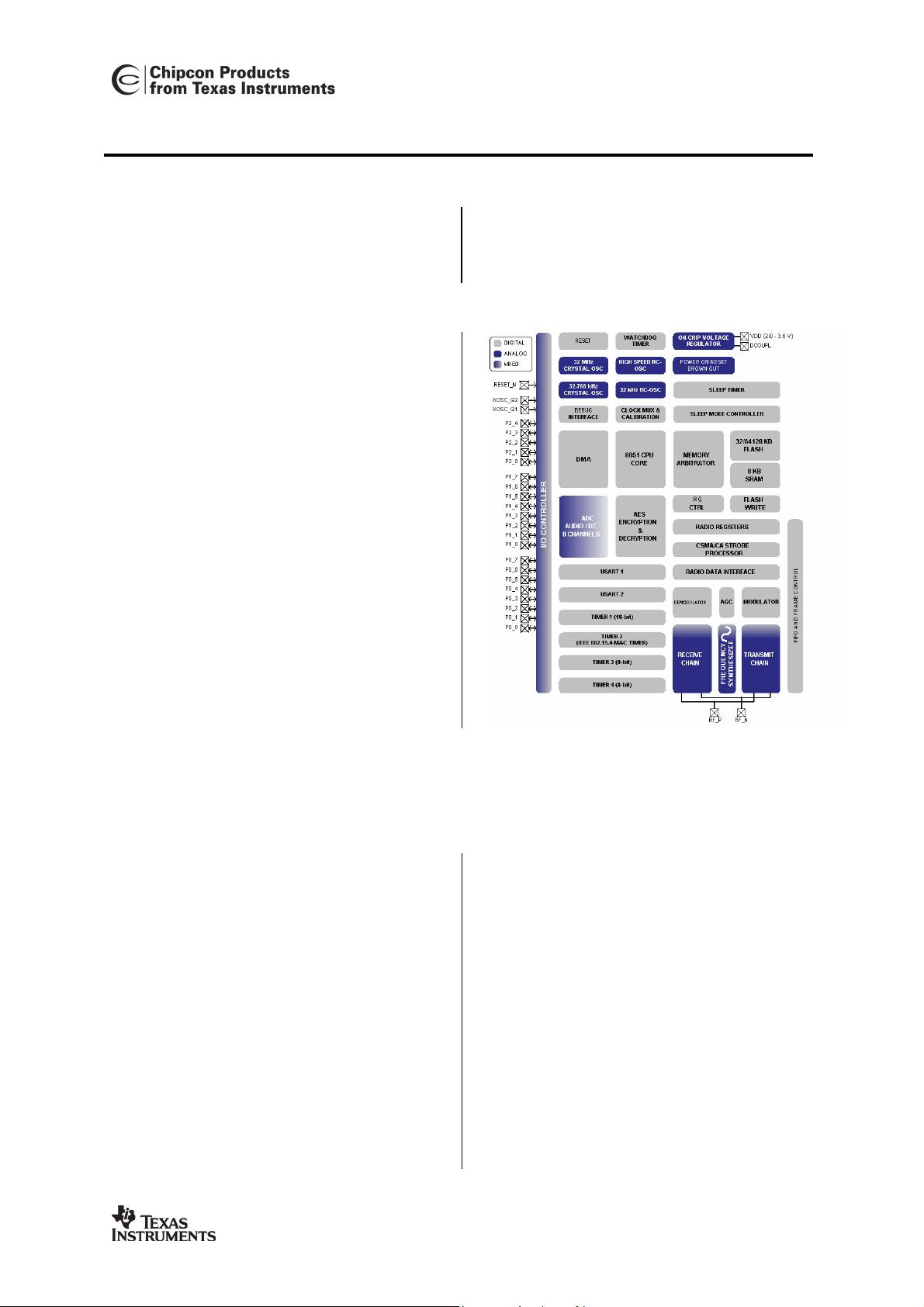

CC2430

CC2430 PRELIMINARY Data Sheet (rev. 1.03) SWRS036A Page 4 of 232

12.7 INTERRUPTS ...........................................................................................................................52

12.8 OSCILLATORS AND CLOCKS ....................................................................................................62

12.9 DEBUG INTERFACE .................................................................................................................62

12.10 RAM......................................................................................................................................66

12.11 FLASH MEMORY.....................................................................................................................66

12.12 MEMORY ARBITER .................................................................................................................66

13 PERIPHERALS........................................................................................................................69

13.1 I/O PORTS ...............................................................................................................................69

13.2 DMA CONTROLLER ............................................................................................................... 86

13.3 16-BIT TIMER, TIMER1 ...........................................................................................................98

13.4 MAC TIMER (TIMER 2) ........................................................................................................ 110

13.5 SLEEP TIMER ........................................................................................................................117

13.6 8-BIT TIMER 3 AND TIMER 4 ................................................................................................. 118

13.7 ADC.....................................................................................................................................127

13.8 RANDOM NUMBER GENERATOR........................................................................................... 133

13.9 AES COPROCESSOR.............................................................................................................. 135

13.10 POWER MANAGEMENT ......................................................................................................... 140

13.11 POWER ON RESET AND BROWN OUT DETECTOR ..................................................................144

13.12 WATCHDOG TIMER...............................................................................................................145

13.13 USART................................................................................................................................147

13.14 FLASH CONTROLLER ............................................................................................................157

14 RADIO..................................................................................................................................... 164

14.1 IEEE 802.15.4 MODULATION FORMAT ................................................................................165

14.2 COMMAND STROBES............................................................................................................. 166

14.3 RF REGISTERS...................................................................................................................... 166

14.4 INTERRUPTS .........................................................................................................................166

14.5 FIFO ACCESS........................................................................................................................ 169

14.6 DMA....................................................................................................................................170

14.7 RECEIVE MODE .....................................................................................................................170

14.8 RXFIFO OVERFLOW ............................................................................................................170

14.9 TRANSMIT MODE .................................................................................................................. 171

14.10 GENERAL CONTROL AND STATUS ......................................................................................... 172

14.11 DEMODULATOR, SYMBOL SYNCHRONIZER AND DATA DECISION......................................... 172

14.12 FRAME FORMAT ...................................................................................................................173

14.13 SYNCHRONIZATION HEADER................................................................................................. 173

14.14 LENGTH FIELD ...................................................................................................................... 174

14.15 MAC PROTOCOL DATA UNIT ................................................................................................175

14.16 FRAME CHECK SEQUENCE..................................................................................................... 175

14.17 RF DATA BUFFERING ...........................................................................................................176

14.18 ADDRESS RECOGNITION ....................................................................................................... 177

14.19 ACKNOWLEDGE FRAMES...................................................................................................... 178

14.20 RADIO CONTROL STATE MACHINE ........................................................................................179

14.21 MAC SECURITY OPERATIONS (ENCRYPTION AND AUTHENTICATION).................................181

14.22 LINEAR IF AND AGC SETTINGS ...........................................................................................181

14.23 RSSI / ENERGY DETECTION .................................................................................................181

14.24 LINK QUALITY INDICATION..................................................................................................182

14.25 CLEAR CHANNEL ASSESSMENT ............................................................................................182

14.26 FREQUENCY AND CHANNEL PROGRAMMING ........................................................................ 183

14.27 VCO AND PLL SELF-CALIBRATION ..................................................................................... 183

14.28 OUTPUT POWER PROGRAMMING .......................................................................................... 183

14.29 INPUT / OUTPUT MATCHING .................................................................................................184

14.30 TRANSMITTER TEST MODES .................................................................................................184

14.31 SYSTEM CONSIDERATIONS AND GUIDELINES ....................................................................... 186

14.32 PCB LAYOUT RECOMMENDATION .......................................................................................188

14.33 ANTENNA CONSIDERATIONS ................................................................................................189

14.34 CSMA/CA STROBE PROCESSOR .......................................................................................... 189

keda12015-04-27是CC2430的资料,根本没有CC2530

keda12015-04-27是CC2430的资料,根本没有CC2530 foolfish1012013-01-21英文的,是中文的就好咯,谢谢

foolfish1012013-01-21英文的,是中文的就好咯,谢谢 我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功