没有合适的资源?快使用搜索试试~ 我知道了~

MSP430F449 数据手册

温馨提示

试读

85页

MSP430F449 数据手册,英文的,有需要的可以下载一下,有需要的可以下载一下,有需要的可以下载一下~~~~

资源推荐

资源详情

资源评论

SLAS344A – JANUARY 2002 – REVISED FEBRUARY 2002

1

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

D Low Supply-Voltage Range, 1.8 V to 3.6 V

D Ultralow-Power Consumption:

– Active Mode: 280 µA at 1 MHz, 2.2 V

– Standby Mode: 1.1 µA

– Off Mode (RAM Retention): 0.1 µA

D Five Power Saving Modes

D Wake-Up From Standby Mode in 6 µs

D 16-Bit RISC Architecture,

125-ns Instruction Cycle Time

D 12-Bit A/D Converter With Internal

Reference, Sample-and-Hold and Autoscan

Feature

D 16-Bit Timer With Three

†

or Seven

‡

Capture/Compare-With-Shadow Registers,

Timer_B

D 16-Bit Timer With Three Capture/Compare

Registers, Timer_A

D On-Chip Comparator

D Serial Communication Interface (USART),

Select Asynchronous UART or

Synchronous SPI by Software;

Two USARTs (USART0, USART1) In

MSP430x44x Devices

One USART (USART0) In MSP430x43x

Devices

D Brownout Detector

D Supply Voltage Supervisor/Monitor With

Programmable Level Detection

D Serial Onboard Programming,

No External Programming Voltage Needed

Programmable Code Protection by Security

Fuse

D Integrated LCD Driver for Up to

160 Segments

D Family Members Include:

– MSP430F435:

16KB+256B Flash Memory,

512B RAM

– MSP430F436:

24KB+256B Flash Memory,

1KB RAM

– MSP430F437:

32KB+256B Flash Memory,

1KB RAM

– MSP430F447:

32KB+256B Flash Memory,

1KB RAM

– MSP430F448:

48KB+256B Flash Memory,

2KB RAM

– MSP430F449:

60KB+256B Flash Memory,

2KB RAM

D For Complete Module Descriptions, See

The MSP430x4xx Family User’s Guide,

Literature Number SLAU056

†

’F435, ’F436, and ’F437 devices

‡

’F447, ’F448, and ’F449 devices

description

The Texas Instruments MSP430 series is an ultralow-power microcontroller family consisting of several devices

featuring different sets of modules targeted to various applications. The microcontroller is designed to be battery

operated for use in extended-time applications. The MSP430 achieves maximum code efficiency with its 16-bit

RISC architecture, 16-bit CPU-integrated registers, and a constant generator. The digitally-controlled oscillator

provides wake-up from low-power mode to active mode in less than 6 µs. The MSP430x43x and the

MSP430x44x series are microcontroller configurations with two built-in 16-bit timers, a fast 12-bit A/D converter,

one or two universal serial synchronous/asynchronous communication interfaces (USART), 48 I/O pins, and

a liquid crystal driver (LCD) with up to 160 segments.

Typical applications include sensor systems that capture analog signals, convert them to digital values, and

process and transmit the data to a host system, or process this data and displays it on a LCD panel. The timers

make the configurations ideal for industrial control applications such as ripple counters, digital motor control,

EE-meters, hand-held meters, etc. The hardware multiplier enhances the performance and offers a broad code

and hardware-compatible family solution.

Copyright 2002, Texas Instruments Incorporated

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLAS344A – JANUARY 2002 – REVISED FEBRUARY 2002

2

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

AVAILABLE OPTIONS

PACKAGED DEVICES

T

A

PLASTIC 80-PIN QFP

(PN)

PLASTIC 100-PIN QFP

(PZ)

–40°C to 85°C

MSP430F435IPN

†

MSP430F436IPN

†

MSP430F437IPN

†

MSP430F435IPZ

MSP430F436IPZ

MSP430F437IPZ

MSP430F447IPZ

MSP430F448IPZ

MSP430F449IPZ

†

Advanced Information

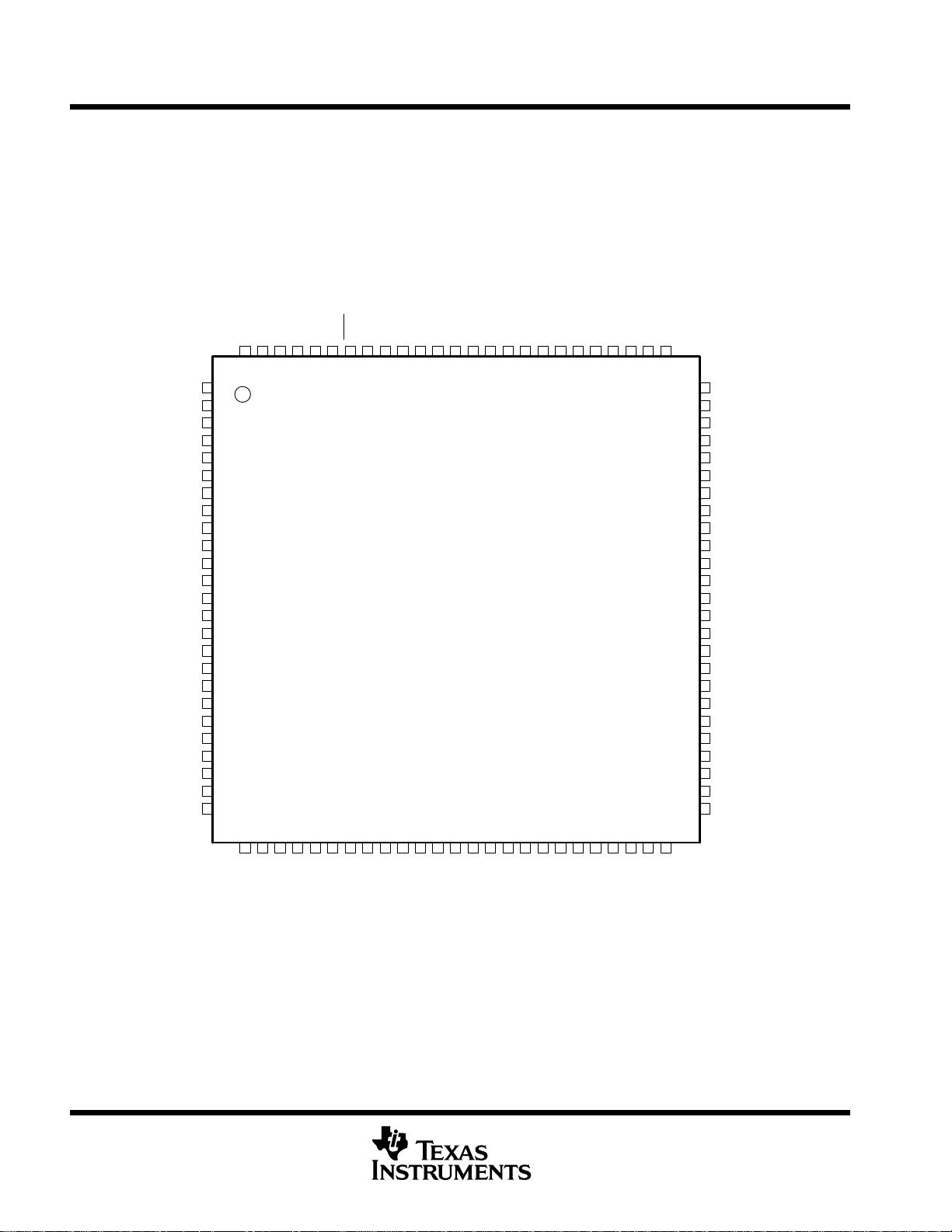

pin designation, MSP430x435IPN, MSP430x436IPN, MSP430x437IPN

†

22 23

P1.7CA1

P2.0/TA2

P2.1/TB0

P2.2/TB1

P2.3/TB2

P2.4/UTXD0

P2.5/URXD0

DV

SS2

DV

CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P3.0/STE0/S31

P3.1/SIMO0/S30

P3.2/SOMI0/S29

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

24

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

DV

CC1

P6.3/A3

P6.4/A4

P6.5/A5

P6.6/A6

P6.7/A7/SVSin

VREF+

XIN

XOUT/TCLK

VeREF+

VREF–/VeREF–

P5.1/S0

P5.0/S1

P4.7/S2

P4.6/S3

P4.5/S4

P4.4/S5

P4.3/S6

P4.2/S7

P4.1/S8

25 26 27 28

PN PACKAGE

(TOP VIEW)

TDO/TDI

79 78 77 76 7580 74

P6.1/A1

P6.0/A0

RST/NMI

TCK

TMS

P2.6/CAOUT/S19

S21

S15

S16

S17

72 71 7073

29

30 31 32 33

69 68

21

P4.0/S9

XT2OUT

67 66 65 64

34 35 36 37

S22

S23

P3.7/S24

P3.6/S25

P1.0/TA0

P1.1/TA0/MCLK

P1.2/TA1

P1.3/TBOUTH/SVSOUT

AV

P3.5/S26

P3.4/S27

38 39 40

P1.4/TBCLK/SMCLK

P1.5/TACLK/ACLK

63 62 61

TDI

XT2IN

P1.6/CA0

S10

S20

P3.3/UCLK0/S28

S11

S12

S13

S14

P2.7/ADC12CLK/S18

P6.2/A2

CC

DV

SS1

AV

SS

MSP430F435IPN

MSP430F436IPN

MSP430F437IPN

SLAS344A – JANUARY 2002 – REVISED FEBRUARY 2002

3

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

pin designation, MSP430x435IPZ, MSP430x436IPZ, MSP430x437IPZ

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

P1.7/CA1

P6.1/A1

P6.0/A0

RST/NMI

XT2IN

XT2OUT

P1.3/TBOUTH/SVSOUT

P1.4/TBCLK/SMCLK

P1.5/TACLK/ACLK

P1.6/CA0

P2.3/TB2

S14

S15

S16

S17

S18

S20

S25

S26

S27

S28

S29

S31

P4.7/S34

S30

PZ PACKAGE

(TOP VIEW)

P1.0/TA0

TDI

TDO/TDI

S21

SS1

DV

P6.2/A2

P1.2/TA1

S24

P4.6/S35

DV

CC1

P6.3/A3

P6.4/A4

P6.5/A5

P6.6/A6

P6.7/A7/SVSin

VREF+

XIN

XOUT/TCLK

VeREF+

VREF–/VeREF–

P5.1/S0

P5.0/S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

P2.4/UTXD0

P2.5/URXD0

P2.6/CAOUT

P2.7/ADC12CLK

P3.0/STE0

P3.1/SIMO0

P3.2/SOMI0

P3.3/UCLK0

P3.4

P3.5

P3.6

P3.7

P4.0

P4.1

DV

SS2

DV

CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P4.2/S39

S19

S22

S23

S33

S32

P4.5/S36

P4.4/S37

P4.3/S38

CC

AV

SS

AV

TCK

TMS

P1.1/TA0/MCLK

P2.0/TA2

P2.1/TB0

P2.2/TB1

MSP430F435IPZ

MSP430F436IPZ

MSP430F437IPZ

SLAS344A – JANUARY 2002 – REVISED FEBRUARY 2002

4

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

pin designation, MSP430x447IPZ, MSP430x448IPZ, MSP430x449IPZ

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

P1.7/CA1

P6.1/A1

P6.0/A0

RST/NMI

XT2IN

XT2OUT

P1.3/TBOUTH/SVSOUT

P1.4/TBCLK/SMCLK

P1.5/TACLK/ACLK

P1.6/CA0

P2.3/TB2

S14

S15

S16

S17

S18

S20

S25

S26

S27

S28

S29

S31

P4.7/S34

S30

PZ PACKAGE

(TOP VIEW)

P1.0/TA0

TDI

TDO/TDI

S21

SS1

DV

P6.2/A2

P1.2/TA1

S24

P4.6/S35

DV

CC1

P6.3/A3

P6.4/A4

P6.5/A5

P6.6/A6

P6.7/A7/SVSin

VREF+

XIN

XOUT/TCLK

VeREF+

VREF–/VeREF–

P5.1/S0

P5.0/S1

S2

S3

S4

S5

S6

S7

S8

S9

S10

S11

S12

S13

P2.4/UTXD0

P2.5/URXD0

P2.6/CAOUT

P2.7/ADC12CLK

P3.0/STE0

P3.1/SIMO0

P3.2/SOMI0

P3.3/UCLK0

P3.4/TB3

P3.5/TB4

P3.6/TB5

P3.7/TB6

P4.0/UTXD1

P4.1/URXD1

DV

SS2

DV

CC2

P5.7/R33

P5.6/R23

P5.5/R13

R03

P5.4/COM3

P5.3/COM2

P5.2/COM1

COM0

P4.2/STE1/S39

S19

S22

S23

S33

S32

P4.5/UCLK1/S36

P4.4/SOMI1/S37

4.3/SIMO1/S38

CC

AV

SS

AV

TCK

TMS

P1.1/TA0/MCLK

P2.0/TA2

P2.1/TB0

P2.2/TB1

MSP430F447IPZ

MSP430F448IPZ

MSP430F449IPZ

SLAS344A – JANUARY 2002 – REVISED FEBRUARY 2002

5

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

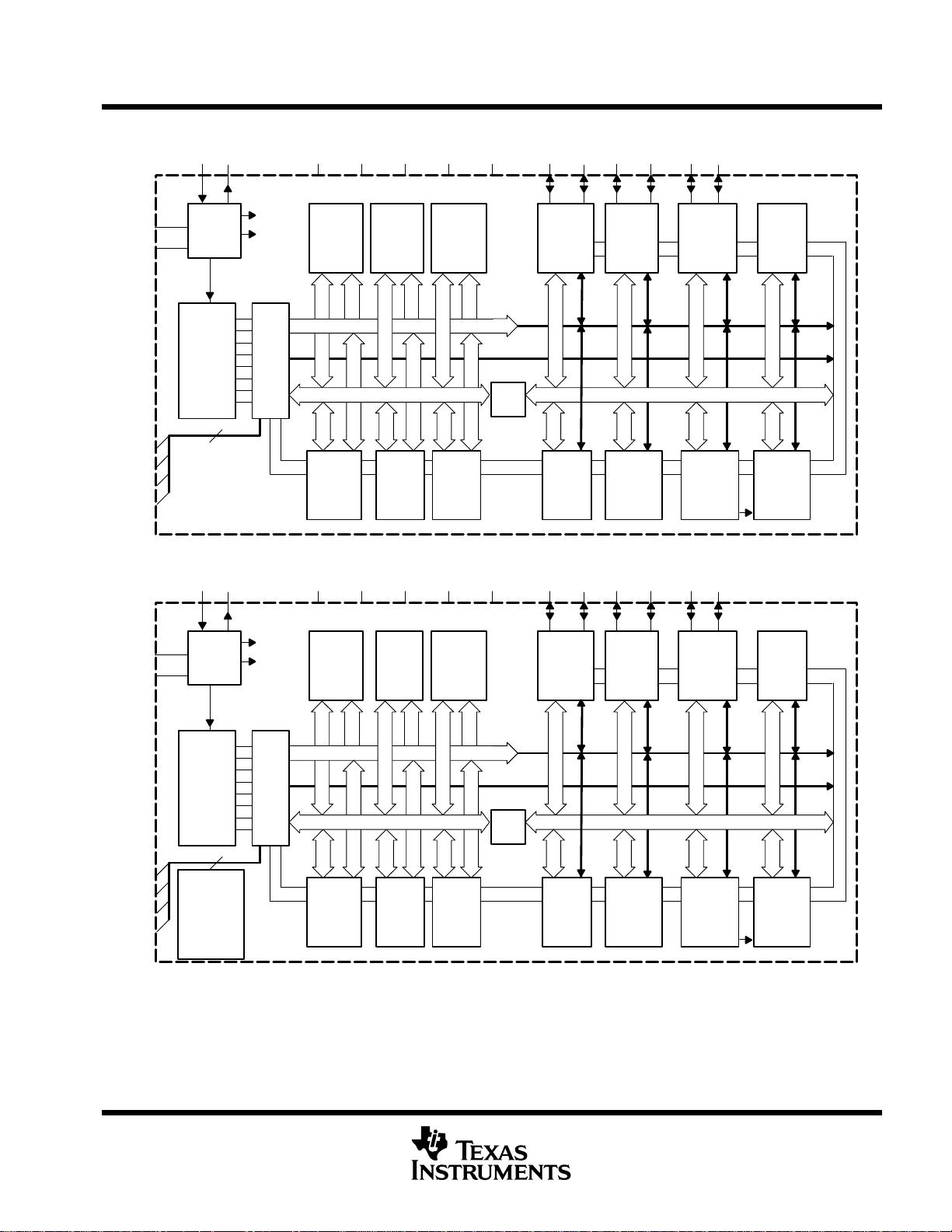

MSP430x43x functional block diagrams

Oscillator

FLL+

ACLK

SMCLK

512 B RAM I/O Port 5/6 I/O Port 3/4

16 I/Os

USART0

CPU

Incl. 16 Reg.

Test

JTAG

Bus

Conv

Comparator

Watchdog Timer_B3

Timer

15 / 16 Bit

3 CC–Reg

MDB, 8 Bit

MCB

XIN XOUT/TCLK AVCC AVSS RST/NMI P3 P4 P1 P2

XT2IN

XT2OUT

TMS

TCK

16 kB Flash

24 kB Flash

12 Bit ADC

8 Channels

<10

Timer_A3

Emulation

Module

MDB, 16 Bit

MAB, 16 Bit

MCLK

4

TDI

TDO/TDI

Shadow

Reg.

3 CC-Reg.

32 kB Flash

1 kB RAM

1 kB RAM µs Conv.

P5 P6DVSSDVCC

A

16 I/Os, With

I/O Port 1/2

Interrupt

Capability

UART or

SPI

Function

LCD

160

Segments

1,2,3,4 MUX

Basic

Timer1

1 Interrupt

Vector

POR

SVS

Brownout

f

LCD

MAB,

4 Bit

MSP430x44x functional block diagrams

Oscillator

FLL+

ACLK

SMCLK

2 kB RAM

I/O Port 5/6 I/O Port 3/4

16 I/Os

USART0

CPU

Incl. 16 Reg.

Test

JTAG

Bus

Conv

Comparator

Watchdog Timer_B7

Timer

15 / 16 Bit

7 CC-Reg.

MDB, 8 Bit

MCB

XIN XOUT/TCLK AVCC AVSS RST/NMI P3 P4 P1 P2

XT2IN

XT2OUT

TMS

TCK

60 kB Flash

48 kB Flash

12 Bit ADC

8 Channels

<10

Timer_A3

Emulation

Module

MDB, 16 Bit

MAB, 16 Bit

MCLK

4

TDI

TDO/TDI

Shadow

Reg.

3 CC-Reg.

32 kB Flash

2 kB RAM

1 kB RAM

µs Conv.

P5 P6

USART1

DVSSDVCC

Multipy

MPY, MPYS

MAC,MACS

8×8 Bit

8×16 Bit

16×8 Bit

16×16 Bit

A

16 I/Os, With

I/O Port 1/2

Interrupt

Capability

UART or

SPI

Function

LCD

160

Segments

1,2,3,4 MUX

Basic

Timer1

1 Interrupt

Vector

POR

SVS

Brownout

f

LCD

MAB,

4 Bit

剩余84页未读,继续阅读

资源评论

you1mima2012-10-23不错的资源,物联网第一芯片资料

you1mima2012-10-23不错的资源,物联网第一芯片资料

1______1

- 粉丝: 58

- 资源: 258

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 功率拓扑快速参考指南-ti,TI官方出品

- 开关电源拓朴图表,各种电路拓扑表格

- 登录和注册 前端:vue3+iview plus +axios 后台:spring boot +mybatis

- 软件测试入门简介:从基础到实践的全面介绍

- 2024CDA Level Ⅰ 认证考试大纲

- YOLO 数据集:淋巴病灶检测(1类别,包含训练集、验证集)

- 基于AT91RM9200处理器+XC3S250E(FPGA)+AD5322采集板Cadence ORCAD(硬件原理图+PCB)

- java+vue2实现zebra打印机,js实现

- J-link烧录软件,用于hex文件烧录

- VB打开时间同步页面/Internet时间设置.vbs

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功