没有合适的资源?快使用搜索试试~ 我知道了~

设计和实现相对简单 CPU的微程序控制器.doc

1.该资源内容由用户上传,如若侵权请联系客服进行举报

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

版权申诉

0 下载量 58 浏览量

2024-09-19

22:19:03

上传

评论

收藏 441KB DOC 举报

温馨提示

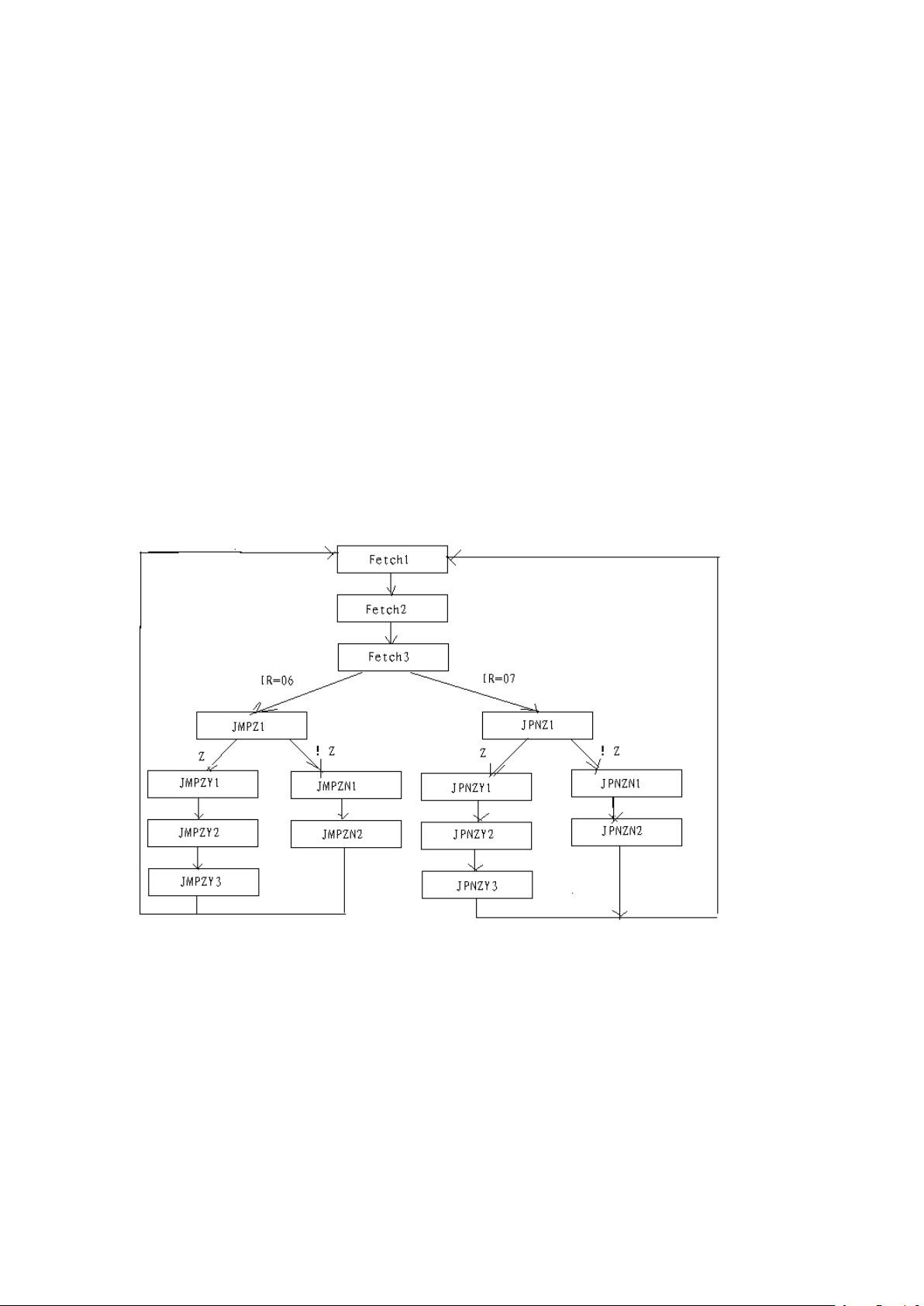

这个控制单元的设计需要修改原来的状态转换图,参看前一章A Relatively Simple CPU设计中的状态转换图,在Fetch3状态,状态的转换影射可能同时影射到两个状态JMPZY1和JMPZN1,其状态的转换还需要参照标志寄存器Z的值来进行。所以,在微序列控制器中应该在影射逻辑中加入输入标志寄存器Z。而通常情况下,映射逻辑只接受IR寄存器中的操作码作为其输入,标志寄存器应该在微序列控制器的其他部分处理完成。所以我们需要对原来的状态图进行修改,增加两个状态JMPZ1和JPNZ1,并把Fetch3 的影射逻辑映射到这两个状态的地址上面。然后在这两个状态根据标志寄存器Z的值决定进入下一个状态是JMPZY1还是JMPZN1,或者JPNZY1还是JPNZN1。

资源推荐

资源详情

资源评论

3 设计和实现 A Relatively Simple CPU 的微序列控制器

如前面对 Very Simple CPU 的设计一样,我们保留前一章的指令集、数据路径、ALU

等不变,而只是对其控制逻辑进行设计。

3.1 修改状态图

这个控制单元的设计需要修改原来的状态转换图,参看前一章 A Relatively Simple CPU

设计中的状态转换图,在 Fetch3 状态,状态的转换影射可能同时影射到两个状态 JMPZY1

和 JMPZN1,其状态的转换还需要参照标志寄存器 Z 的值来进行。所以,在微序列控制器中

应该在影射逻辑中加入输入标志寄存器 Z。而通常情况下,映射逻辑只接受 IR 寄存器中的

操作码作为其输入,标志寄存器应该在微序列控制器的其他部分处理完成。所以我们需要对

原来的状态图进行修改,增加两个状态 JMPZ1 和 JPNZ1,并把 Fetch3 的影射逻辑映射到这

两个状态的地址上面。然后在这两个状态根据标志寄存器 Z 的值决定进入下一个状态是

JMPZY1 还是 JMPZN1,或者 JPNZY1 还是 JPNZN1。修改部分的状态转换图如下,其余部

分不变(参看前一章)

3.2 设计微序列硬件和微代码

这个 CPU 包含条件跳转语句,新创建的两个状态 JMPZ1 和 JPNZ1 根绝标志寄存器 Z

的值能够跳转到两个不同的状态。所以微序列控制器里面需要包含处理条件分支语句的功能。

如果条件符合则进行跳转取下一条为指令的地址为微代码存储器的输出域 ADDR,否则去

微代码存储器的下一条微代码也就是原来地址加一。

这个微序列控制器得基本流程框图如下:

资源评论

等天晴i

- 粉丝: 5838

- 资源: 10万+

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功