5.3 可编程逻辑器件开发工具.doc

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

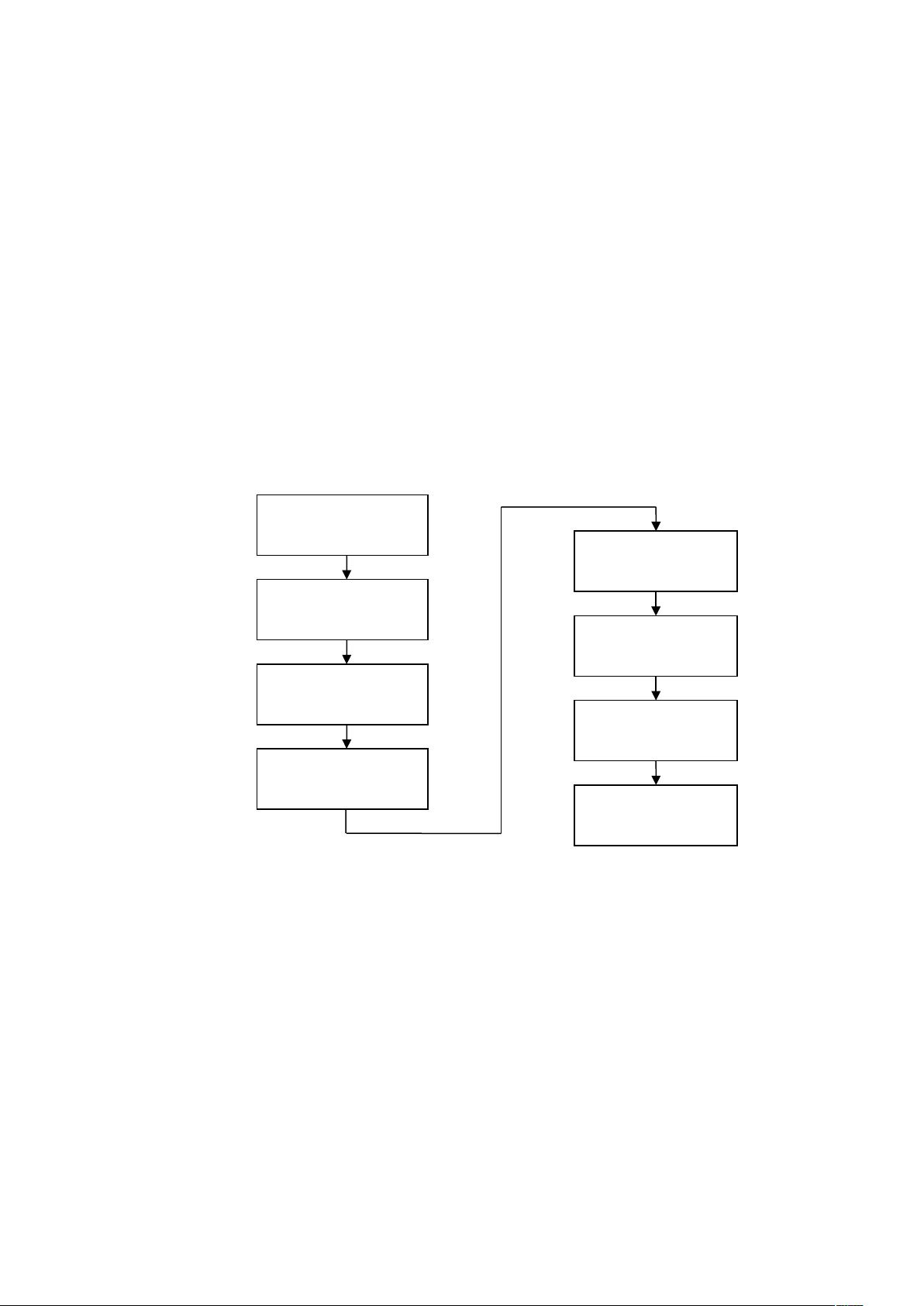

【5.3 可编程逻辑器件开发工具.doc】 在可编程逻辑器件的开发过程中,Modelsim 是一款常用且重要的仿真工具。它属于电子设计自动化(EDA)软件,用于验证 FPGA(现场可编程门阵列)或 CPLD(复杂可编程逻辑器件)的设计。Modelsim 支持多种硬件描述语言,包括 VHDL 和 Verilog,能够帮助开发者在实际硬件编程之前,进行设计的功能验证和时序分析。 **5.3.1 设计流程** 1. **设计输入(Design Entry)**: 设计的起点是输入设计规格,可以通过 VHDL 语言编程、原理图绘制、状态机描述或真值表等方法。VHDL 是一种广泛使用的硬件描述语言,它允许开发者用高级抽象来描述数字系统的逻辑行为。 2. **功能仿真(Function Simulation)**: 完成设计输入后,进行功能仿真以验证设计的功能是否符合预期。此阶段通常包括语法检查、编译和综合过程,将行为级的 VHDL 代码转换为门级电路模型。功能仿真可以先于或后于综合进行,但通常在综合后进行以方便语法错误的修正。 3. **执行(Implement Design)**: 功能仿真通过后,设计将在目标 FPGA 上进行布局和布线,生成包含时序延迟信息的 VHDL 网络表文件。 4. **时序仿真(Timing Simulation)**: 在硬件测试前,通过时序仿真检查设计是否满足实际时序约束。这一步骤能发现潜在的时序问题,提高硬件测试的效率和准确性。 5. **下载(Programming)**: 生成的位流文件被写入 FPGA 芯片,这个过程通常由器件供应商提供的专用软件完成,需要使用下载线通过计算机接口与目标硬件连接。 6. **硬件测试(Hardware Testing)**: 对实物系统进行实际测试,确保设计的完整性和功能性。 **5.3.2 功能仿真和时序仿真** - **功能仿真**: 功能仿真主要关注设计的逻辑功能,不考虑硬件实现的细节。它在设计编译后立即进行,可以快速验证设计的逻辑行为,而不需要考虑具体的器件特性。 - **时序仿真**: 时序仿真更接近实际硬件运行情况,考虑了延迟和其他物理因素,用于确认设计能否在实际速度下正常工作。它需要精确的时序模型和完整的测试向量,以确保设计在所有可能的工作条件下都能正确运行。 在 FPGA 开发中,Modelsim 提供的功能仿真和时序仿真功能是必不可少的,它们能有效减少设计迭代次数,提高设计质量和效率。通过这些工具,开发者可以在实际硬件制造之前发现并修复问题,从而节省时间和成本。在实际项目中,设计者通常会在设计的不同阶段反复进行功能仿真和时序仿真,以确保设计的可靠性和性能满足需求。

剩余19页未读,继续阅读

- 粉丝: 5800

- 资源: 10万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功