DisplayPort 1.4 TX Subsystem v1.0 4

PG299 April 4, 2018 www.xilinx.com Product Specification

Introduction

DisplayPort 1.4 TX Subsystem implements

functionality of a video source as defined by

the Video Electronics Standards Association

(VESA)'s DisplayPort standard v1.4 and

supports driving resolutions of up to Full Ultra

HD (FUHD) at 30 fps. The Xilinx

®

DisplayPort

subsystems provide highly integrated but

straightforward IP blocks requiring very little

customization by the user.

Features

• Support for DisplayPort Source (TX)

transmissions.

• Supports single stream transport (SST) at

FUHD at 30 fps

• Dynamic lane supports (1, 2, or 4 lanes)

• Dynamic link rate support

(1.62/2.7/5.4/8.1 Gb/s)

• Dynamic support of 6, 8, 10, 12, or 16 bits

per component (BPC).

• Dynamic support of RGB/YCbCr444/

YCbCr422 color formats.

• Supports 16-bit Video PHY (GT) Interface

• Supports 2 to 8 channel Audio.

• Supports native or AXI4-Stream video input

interface.

• Supports SDP packet for static HDR mode.

IP Facts

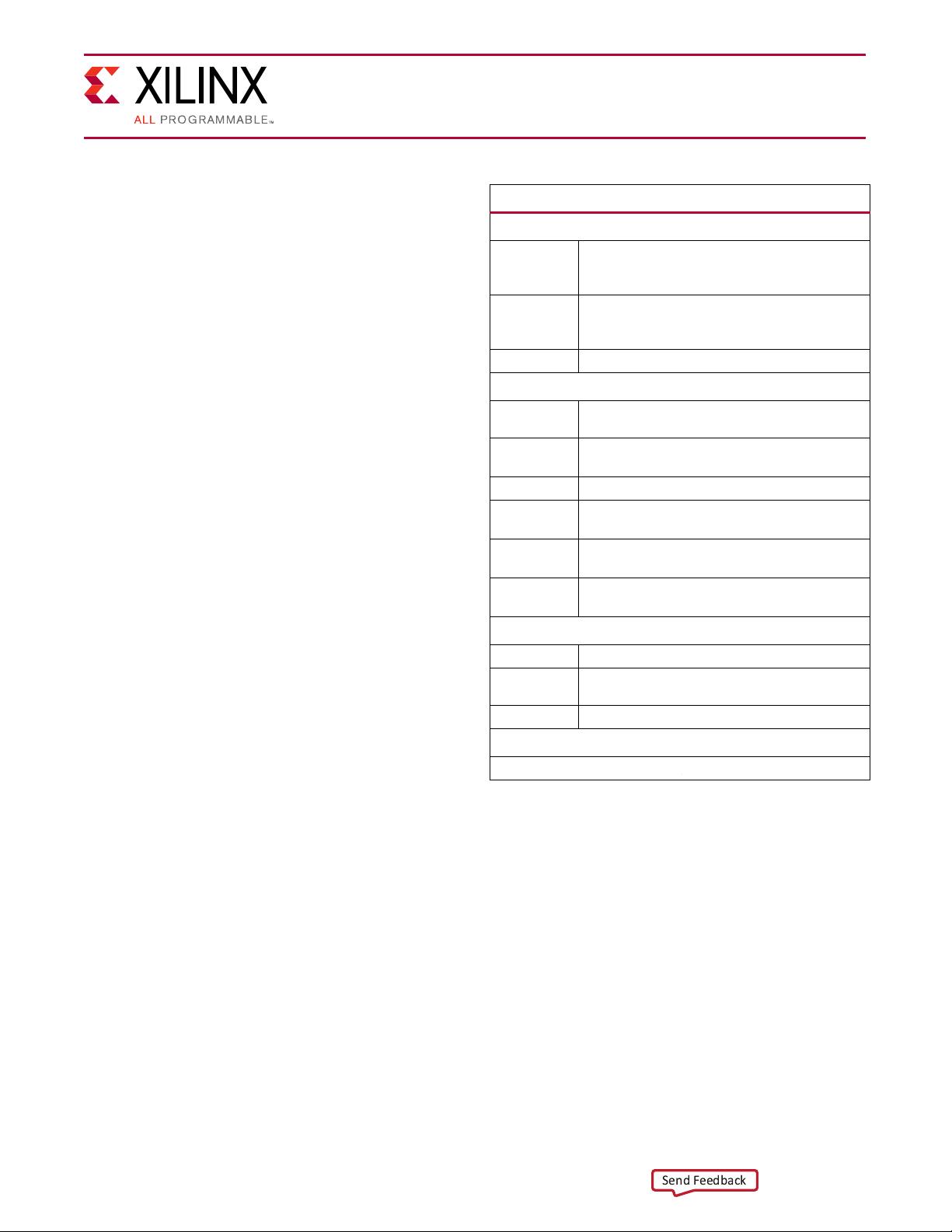

LogiCORE IP Facts Table

Core Specifics

Supported

Device

Family

(1)

UltraScale+™ Families (GTHE4)

UltraScale™ Families (GTHE3)

Supported

User

Interfaces

AXI4-Stream, AXI4-Lite, Native video

Resources Performance and Resource Utilization web page

Provided with Core

Design Files

Hierarchical subsystem packaged with DisplayPort

TX core and other IP cores

Example

Design

Vivado IP Integrator

Test Bench N/A

Constraints

File

IP cores delivered with XDC files

Simulation

Model

N/A

Supported

S/W Driver

Standalone

Tested Design Flows

(2)

Design Entry Vivado

®

Design Suite

Simulation

For supported simulators, see the

Xilinx Design Tools: Release Notes Guide.

Synthesis Vivado Synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog.

2. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

评论0

最新资源