ModelSim+Synplify+Quartus 的 Altera FPGA的

作者: chenhongyi

软件要求: ModelSimSE、Synplify Pro、 Quartus II

适用人群:初学者

源 代 码: mux4_to_1.v

工作内容 :

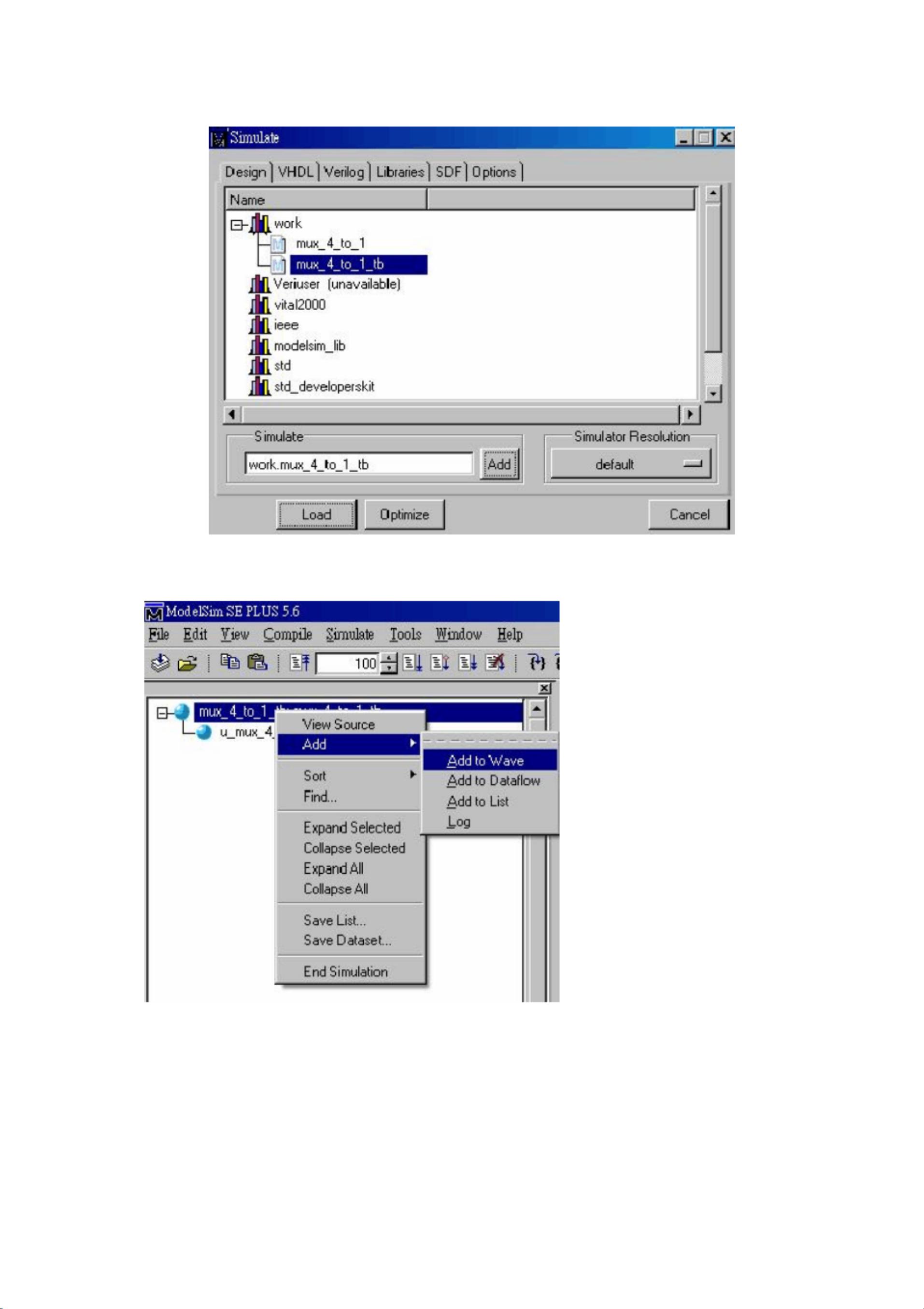

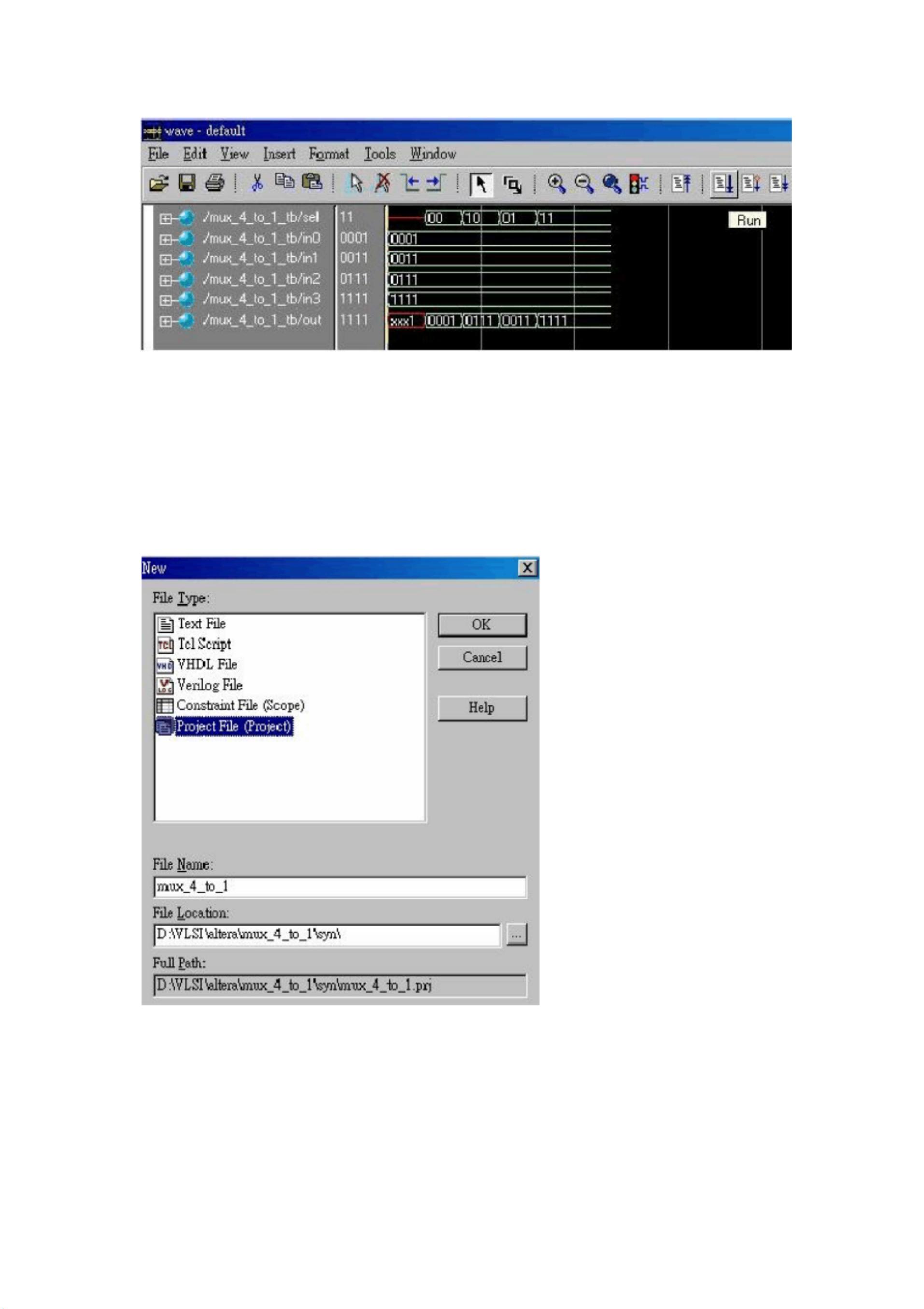

1、设计一个多路选择器,利用 ModelSimSE 做功能仿真;

2、利用 Synplify Pro 进行综合,生成 xxx.vqm 文件;

3、利用 Quartus II 导入 xxx.vqm 进行自动布局布线,并生成 xxx.vo(Verilog

4、利用 ModelSimSE 做后仿真,看是否满足要求。

注:

1. 仿真器 (Simulator) 是用来仿真电路的波形。

2. 综合工具 (Synthesizer)的功能是将 HDL 转换成由电路所组成的 Netlist 。

3. 一般而言,在电路设计的仿真上可分为 Pre‐Sim 和 Post‐Sim。Pre‐Sim 是针而 Post‐Sim 则

是针对综合过且做完成了 Auto Place and Route(APR)的电路进行仿真, 以确保所设计的电路

实现在 FPGA上时,与 Pre‐Sim 的功能一样。

1、前仿真( Pre‐Sim)

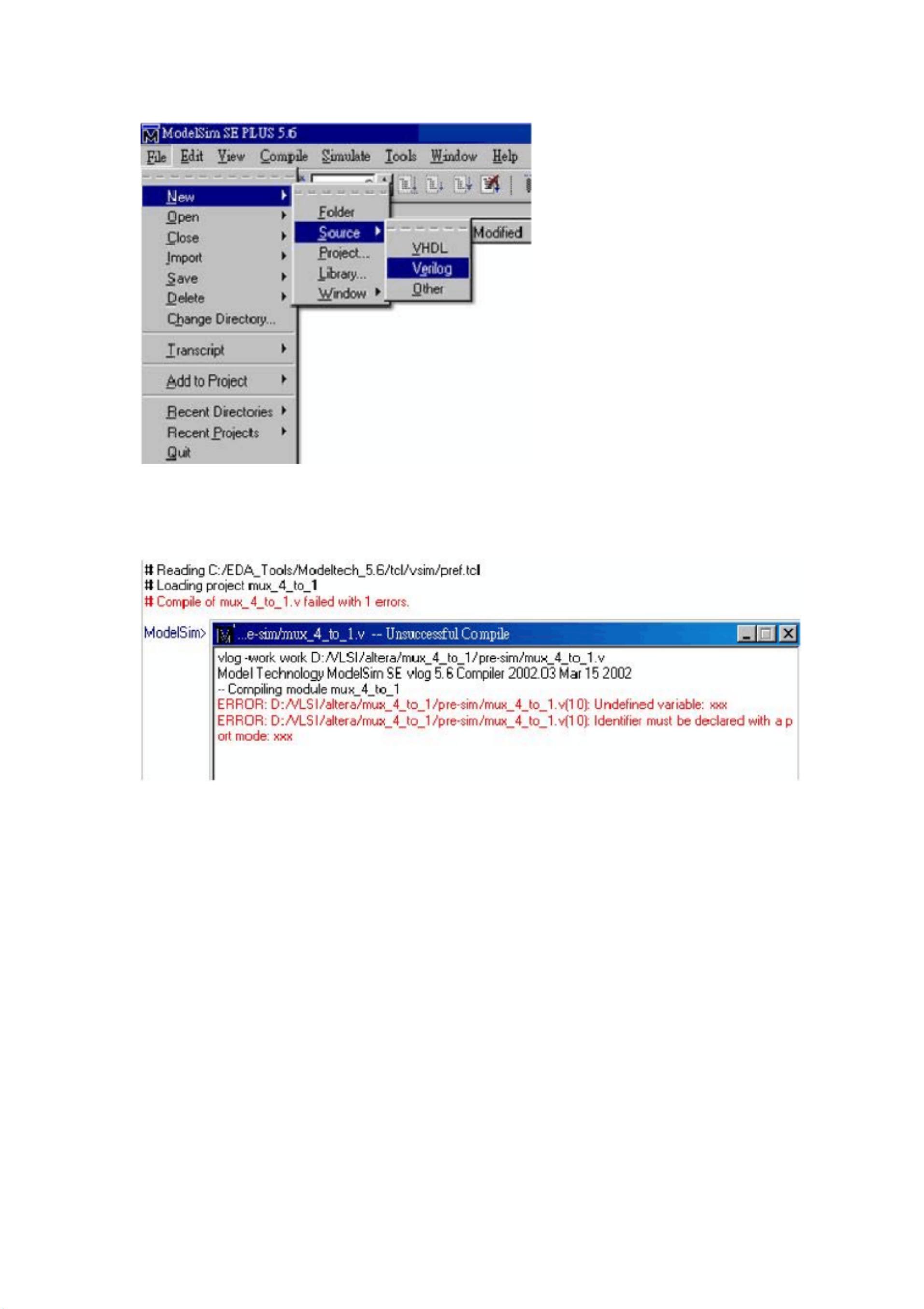

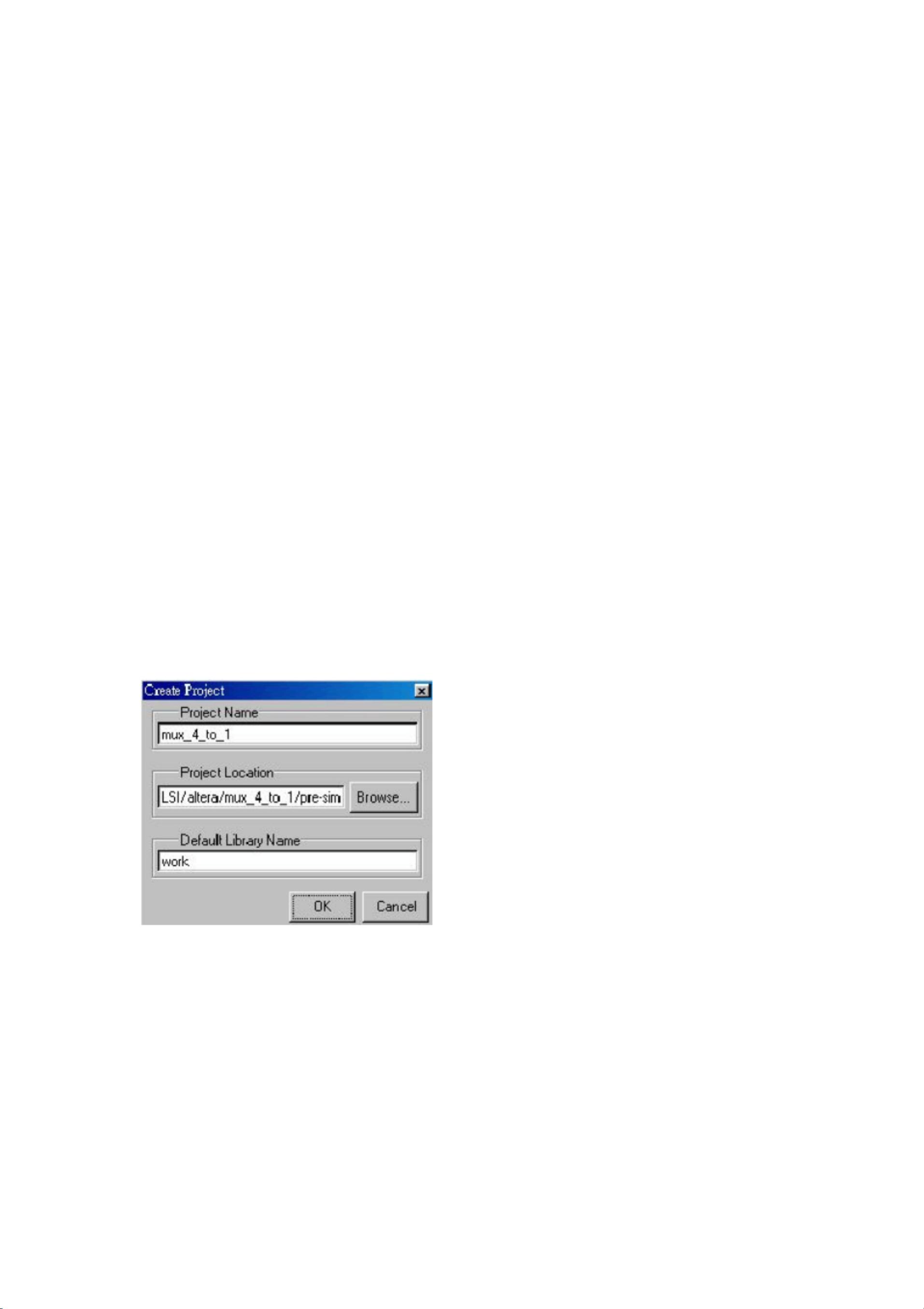

步骤一:打开 ModelSimSE,然后建立一个 Project;

※建立 Project 的方式为点选 File → New → Project…;

※设定 Project Name 与 Project location ,按 OK 即可建立 Project。

步骤二:新增设计文档或加入文档。

※新增文档的方式为点选 File → New → Source → Verilog,然后对文档进行编辑并储存

为 xxx.v;

※ 加 入 文 档 的 方 式 为 点 选 File → Add to Project → File... , 然 后 点 选 xxx.v ;