XX 大学

课程设计报告

学生姓名: 学 号:

专业班级:

课程名称: 数电课程设计

学年学期: 2022—2023 学年 第 一 学期

指导教师:

年 月

目 录

一、引言.........................................................................................................1

二、设计目的.................................................................................................1

三、总体设计.................................................................................................1

1、数字电子钟的设计原理......................................................................1

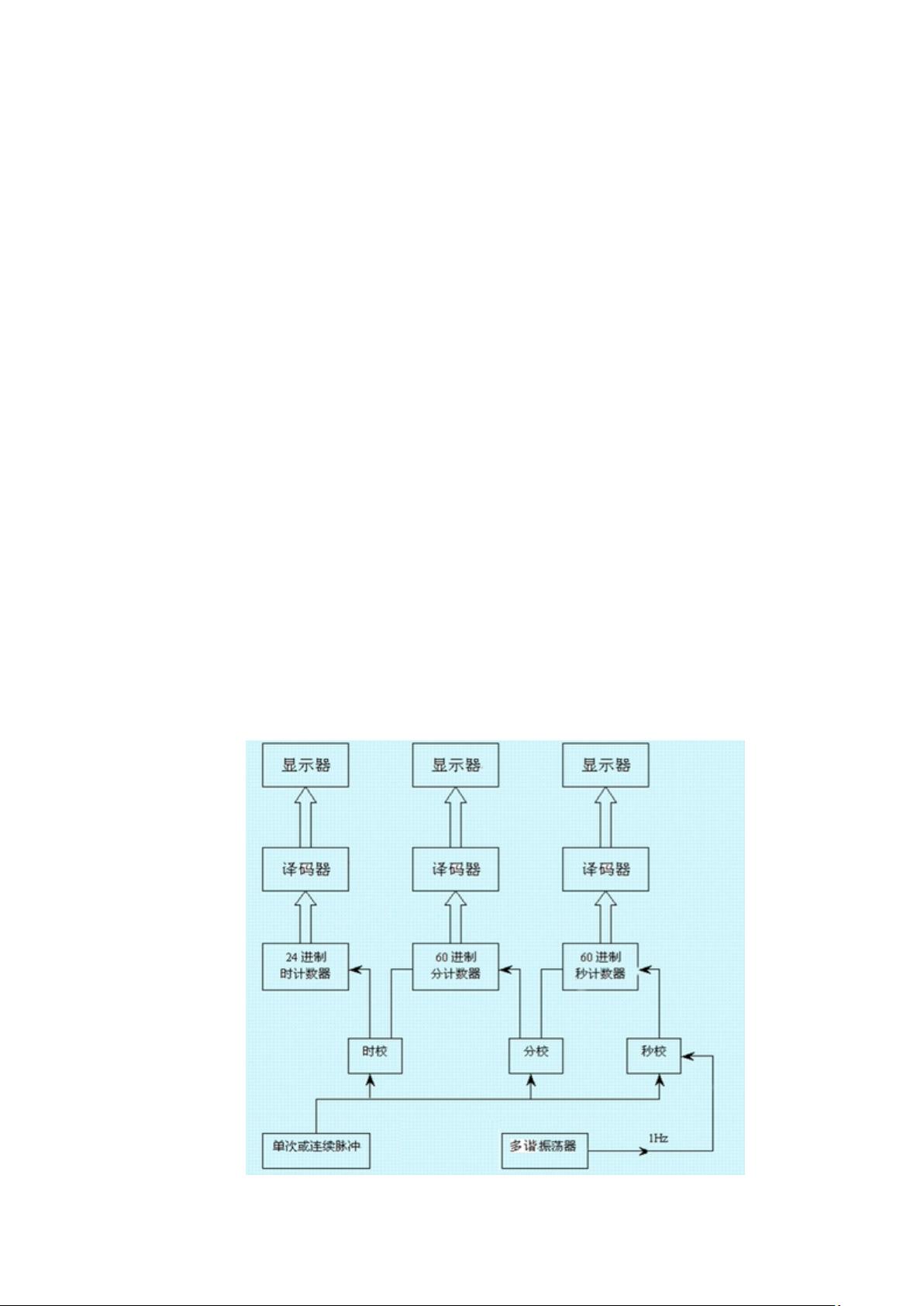

2、数字电子钟的设计框图......................................................................2

四、详细设计.................................................................................................3

1、秒脉冲产生电路..................................................................................3

2、分、秒、时计数电路..........................................................................3

3、译码显示电路......................................................................................5

4、校时电路..............................................................................................6

首先设计通过两个键位标识四种状态.........................................................7

五、组装电路并调试.....................................................................................9

六、元件明细表...........................................................................................10

七、心得体会...............................................................................................11

1

一、引言

数字钟是一种用数字电子技术实现时、分,秒计时的装置,因具有较高的准

确性和直观性等优势而得到广泛应用。设计数字电子钟的过程中,用数字电子技

术的理论和制造实践相结合,进一步加深数字电子技术课程的知识理解与应用。

该电子钟包括计时电路、显示电路、多谐振荡电路和校时电路,使用数码管显示

时、分、秒,通过按键实现对时、分、秒的分别调时。

本次所要设计的数字电子时钟时通过 NI Multisim 14.0 仿真软件,采用模块化

设计方法,设计的一款具有时、分、秒显示功能的计时装置。它的计时周期为 24

小时,满刻度为 23 小时 59 分 59 秒。

二、设计目的

(1)培养学生设计、调试常用数字电路小系统的能力。

(2)提高学生应用计数器自功能扩展、级联方法的能力。

(3)提高学生对计数、译码、显示系统的设计能力

三、总体设计

1、数字电子钟的设计原理

数字电子钟一般由振荡器、分频器、译码器、显示器等几部分组成。

工作原理为用稳定的脉冲信号供给作为数字钟的时间基准,要求振荡频率为

1HZ 的标准秒脉冲。将标准脉冲信号送入秒计数器,秒计数器采用 60 进制(00--59)

计数器,每累计 60 秒发出进位信号并使自身回到 00,将秒计数器的进位信号作

2

为分计数器的时钟脉冲,分计数器同样采用 60 进制(00--59)计数器,每累计 60

分钟发出进位信号并使自身回到 00,将分计数器的进位信号作为时计数器的时钟

脉冲,时计数器采用 24 进制(00--23)计数器,可实现对 24 小时的累计,译码器、

驱动器和显示器构成译码显示电路,各计数器输出信号经过译码器、驱动器到显

示器从而显示时间数字。并设置校时电路用于分别对时、分、秒计数器进行调整

校正。

各种功能电路及器件的确定:

(1)脉冲产生电路:LM555CM、示波器、高电平 VCC、地、电容、电阻

(2)分、秒、时计数电路:74LS160、与非门以及高电平 VCC 构成六十进制

计数器、二十四进制计数器

(3)译码显示电路:七段显示器,7448 和高电平 VCC

(4)校时电路:采用多个门电路

2、数字电子钟的设计框图