《计算机组成与设计》

实验指导书

2018.2

山东大学

目录

实验

1

基本逻辑门逻辑实验

实验

2

逻辑运算电路

实验

3

补码加法器

实验

4

移位器

实验

5

四位补码运算器

实验

6

七段译码设计

实验

7 ROM

实验

实验

8 RAM

实验

实验

9 RAM

扩展实验

实验

10

二进制补码加法器实验

实验

11

节拍脉冲发生器时序电路实验

实验

12

时序系统实验

实验

13

控制器实验

实验

14 CPU

综合实验

附录一

常用实验器件引脚图

实验

1

基本逻辑门逻辑实验

!

!" #$%&

1. 掌握 TTL 常用逻辑门输入与输出之间的逻辑关系。

2. 熟悉 TTL 中、小规模集成电路的外型、管脚和使用方法。

'" #$() QuartII *+,-

1. 二输入四异或门 74LS86

2. 三态门 TRI

3. 四位二进制计数器 74LS161

4. 3-8 译码器 74LS138

5. 双向移位寄存器 74LS194

6. 8 位寄存器 74LS74

." #$+/

测试 74LS86、tri、138、161、74LS194、74LS74 集成电路模块,分析其输入和输出

之间的逻辑关系。

0" #$12

1.在 quartii 环境下,建立工程文件,调入被测器件,将其输入管脚绑定在相应的

开关上,输出管脚绑定在相应的指示灯上,建立源文件。

2.将该文件编译下载到实验平台上的 FPGA 内,按照所测器件的功能表逐条验证。

3.用实验台的电平开关输出作为被测器件的输入。拨动开关,则改变器件的输入

电平。

4.将被测器件的输出引脚与实验台上的电平指示灯连接。指示灯亮表示输出电平为 1,

指示灯灭表示输出电平为 0。

3" (4,-&56789:;<=>

?@#$ABCD#$EFGHI7DJKLMN

(1)74LS86 中包含 4 个异或门,可测试一个异或门即可,如图 1 所示。

(2)可使平台工作于模式 5,图中的 K1、K2 绑定

在 FPGA 的 PIO0(52)、 PIO1(55)两个管脚上,

LED0 绑定在 FPGA 的 PIO8(60)管脚上。

(3)测试 74LS86 逻辑关系接线图及测试结果

输

入

输

出

引脚 1

引脚 2

引脚 3

L

L

L

L

H

H

H

L

H

H

H

L

图 1

实验

2

逻辑运算电路

1、实验内容及说明

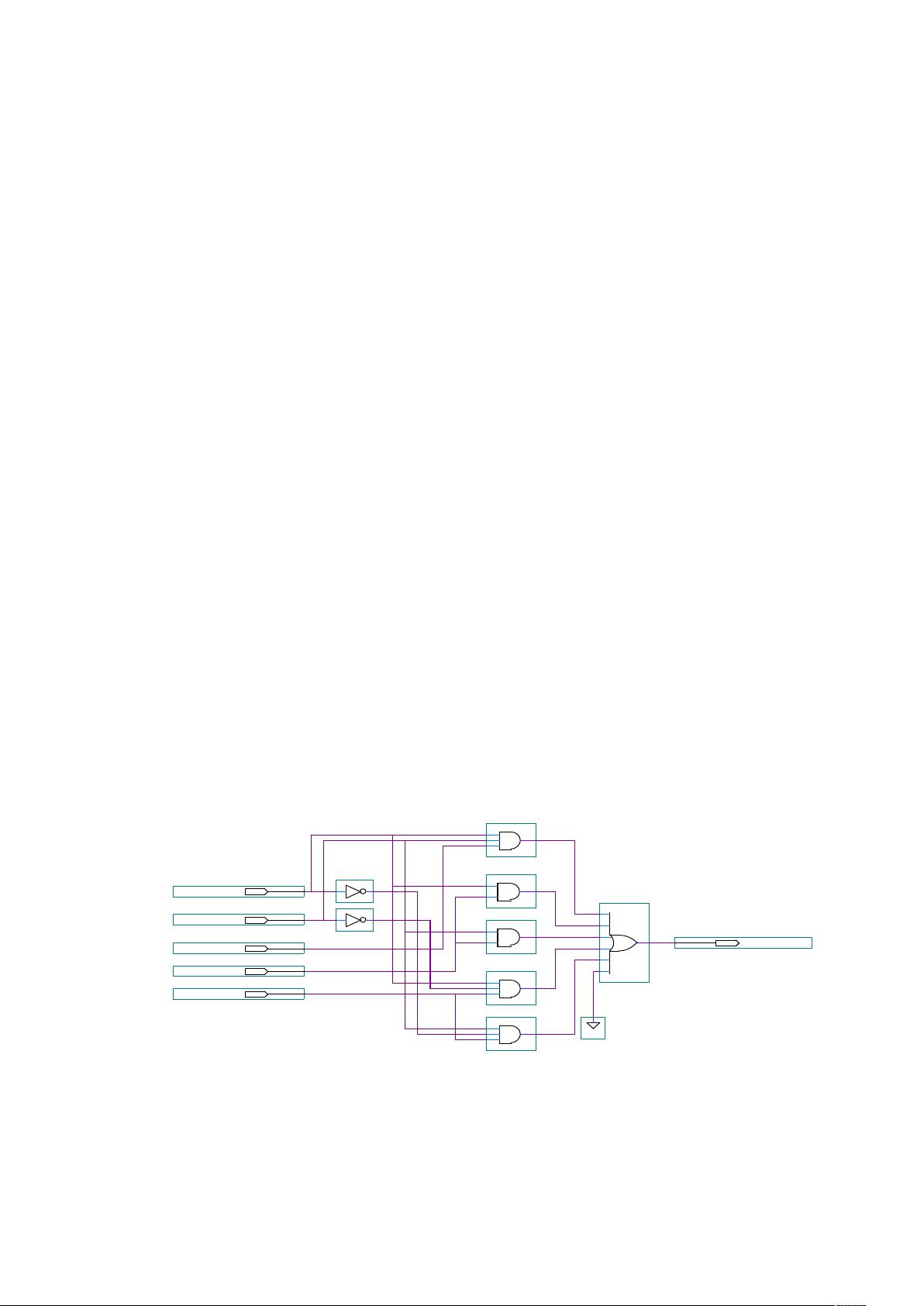

本实验要求设计一个能实现 1 位逻辑乘 ab、逻辑或 a+b、半加(aÅb)的逻辑运算电路。

图 2 为实现上述逻辑功能的电路原理图,其中参与运算的两个 1 位二进制数为 a 和 b,and、

xor 和 or 分别为与运算、异或运算和或运算控制输入端。

2、实验步骤

(1)原理图输入:根据图 2 所示电路,完成逻辑运算的电路原理图设计。

(2)管脚锁定:完成原理图中输入、输出的管脚锁定。

可使平台工作于模式 5,将 a 操作数锁定在键 1 上;将 b 操作数锁定在键 2 上;将输出

e 锁定在 D1 上;将与运算控制输入 and 端锁定在键 3 上;将或运算控制输入 or 端锁定在键

4 上;将异或运算控制输入 xor 端锁定在键 5 上。

(3)原理图编 译、适配 和下载 :在 QuartusⅡ环境中选择 EP4CE6/10

器件,

进行原理

图的编译和适配,无误后完成下载。

(4)功 能 测 试 :利 用 输 入 开 关 及 发 光 二 极 管 LD 测试逻辑运算部件的功能并记录测试结

果。

(5)生成元件符号。

3、选做

利用一位逻辑运算的结果实现两个 4 位二进制数 A(a3a2a1a0)和 B(b3b2b1b0)的逻辑

运算并生成元件符号。使平台工作于模式 5,当按键开关不足时,可使用平台上红色的拨码

开关。

图 2 逻辑运算电路原理图

AND3

inst

AND3

inst 1

AND3

inst 2

AND2

inst3

AND2

inst 4

NOT

inst 6

NOT

inst 7

OR6

inst 12

GND

VCC

a

INPU T

VCC

b

INPU T

VCC

and

INPU T

VCC

or

INPU T

VCC

xor

INPU T

e

OUT PUT

实验

3

补码加法器

1、实验内容及说明

本实验要求采用一位全加器和异或门设计一个四位二进制补码加法器,操作数和运算结

果均采用补码表示,该加法器要求可做补码加法,也可做补码减法运算。

在补码运祘中:

(X)

补

十(Y)

补

=(X 十 Y)

补

(X)

补

-(Y)

补

=(X)

补

十(-Y)

补

图 3 是四位补码加法器的原理图,图中 SUM3-SUM0 表示四位和数,C4 为向高位的进位,

A3-A0 为 A 操作数,B3-B0 为 B 操作数,C0 为低位来的进位, K 为控制端,当 K 为高电平时,

执行减法运算,K 为低电平时,执行加法运算。

2.实验步骤

(1)原理图输入:从元件库中选取相应器件实现四位补码加法器电路设计。

(2)管脚锁定:平台工作于模式 5,将 SUM3-SUM0、C4 依次定义在 LED 指示灯 D5-D1

上,将 K、C0、A3-A0、B3-B0 依次绑定在红色拨码开关 dout1、dout2、键 8-键 5、键 4-键

1 上。

(3)原理图编译、适配和下载:在 QuartusⅡ环境中选择 EP4CE6/10E

器件,

进行原

理图的编译和适配,无误后完成下载。

(4)功能测试:利用输入开关键改变 K、C0 和 A、B 操作数的值,看 LED 指示灯显示的

结果是否正确并记录结果。

(5)生成元件符号。

3、选做

利用四位补码加法运算的结果实现两个 8 位二进制数 A(a7a6a5a4a3a2a1a0)和

B(b7b6b5b4b3b2b1b0)的逻辑运算并生成元件符号。使平台工作于模式 5,当按键开关不足

时,可使用平台上红色的拨码开关。

评论0