SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

This document contains information on a new product. Specifications and information herein are subject to change without

notice.

http://www.solomon-systech.com

SSD1306 Rev 1.1 P 1/59 Apr 2008

Copyright © 2008 Solomon Systech Limited

Advance Information

SSD1306

128 x 64 Dot Matrix

OLED/PLED Segment/Common Driver with Controller

http://www.Datasheet4U.com

Solomon Systech Apr 2008 P 2/59 Rev 1.1 SSD1306

CONTENTS

1 GENERAL DESCRIPTION .......................................................................................................6

2 FEATURES...................................................................................................................................6

3 ORDERING INFORMATION...................................................................................................6

4 BLOCK DIAGRAM ....................................................................................................................7

5 DIE PAD FLOOR PLAN ............................................................................................................8

6 PIN ARRANGEMENT..............................................................................................................11

6.1 SSD1306TR1 PIN ASSIGNMENT.......................................................................................................................... 11

7 PIN DESCRIPTION ..................................................................................................................13

8 FUNCTIONAL BLOCK DESCRIPTIONS.............................................................................15

8.1 MCU INTERFACE SELECTION.............................................................................................................................. 15

8.1.1 MCU Parallel 6800-series Interface.......................................................................................................... 15

8.1.2 MCU Parallel 8080-series Interface.......................................................................................................... 16

8.1.3 MCU Serial Interface (4-wire SPI)............................................................................................................17

8.1.4 MCU Serial Interface (3-wire SPI)............................................................................................................18

8.1.5 MCU I

2

C Interface..................................................................................................................................... 19

8.2 COMMAND DECODER ......................................................................................................................................... 22

8.3 OSCILLATOR CIRCUIT AND DISPLAY TIME GENERATOR..................................................................................... 22

8.4 FR SYNCHRONIZATION ....................................................................................................................................... 23

8.5 RESET CIRCUIT ................................................................................................................................................... 23

8.6 SEGMENT DRIVERS / COMMON DRIVERS ............................................................................................................ 24

8.7 GRAPHIC DISPLAY DATA RAM (GDDRAM)..................................................................................................... 25

8.8 SEG/COM DRIVING BLOCK ............................................................................................................................... 26

8.9 POWER ON AND OFF SEQUENCE ........................................................................................................................ 27

9 COMMAND TABLE.................................................................................................................28

9.1 DATA READ / WRITE .......................................................................................................................................... 33

10 COMMAND DESCRIPTIONS .............................................................................................34

10.1 FUNDAMENTAL COMMAND ............................................................................................................................... . 34

10.1.1 Set Lower Column Start Address for Page Addressing Mode (00h~0Fh) ................................................. 34

10.1.2 Set Higher Column Start Address for Page Addressing Mode (10h~1Fh) ................................................ 34

10.1.3 Set Memory Addressing Mode (20h).......................................................................................................... 34

10.1.4 Set Column Address (21h) ......................................................................................................................... 35

10.1.5 Set Page Address (22h).............................................................................................................................. 36

10.1.6 Set Display Start Line (40h~7Fh) .............................................................................................................. 36

10.1.7 Set Contrast Control for BANK0 (81h)......................................................................................................36

10.1.8 Set Segment Re-map (A0h/A1h)................................................................................................................. 36

10.1.9 Entire Display ON (A4h/A5h).................................................................................................................. 37

10.1.10 Set Normal/Inverse Display (A6h/A7h)..................................................................................................37

10.1.11 Set Multiplex Ratio (A8h)...................................................................................................... ................. 37

10.1.12 Set Display ON/OFF (AEh/AFh) ........................................................................................................... 37

10.1.13 Set Page Start Address for Page Addressing Mode (B0h~B7h)............................................................. 37

10.1.14 Set COM Output Scan Direction (C0h/C8h)..........................................................................................37

10.1.15 Set Display Offset (D3h)........................................................................................................................ 37

10.1.16 Set Display Clock Divide Ratio/ Oscillator Frequency (D5h)............................................................... 40

10.1.17 Set Pre-charge Period (D9h)................................................................................................................. 40

10.1.18 Set COM Pins Hardware Configuration (DAh)..................................................................................... 40

10.1.19 Set V

COMH

Deselect Level (DBh) ......................................................................................................... .. 43

SSD1306 Rev 1.1 P 3/59 Apr 2008 Solomon Systech

10.1.20 NOP (E3h) .............................................................................................................................................43

10.1.21 Status register Read............................................................................................................................... 43

10.2 GRAPHIC ACCELERATION COMMAND................................................................................................................. 44

10.2.1 Horizontal Scroll Setup (26h/27h) ............................................................................................................. 44

10.2.2 Continuous Vertical and Horizontal Scroll Setup (29h/2Ah)..................................................................... 45

10.2.3 Deactivate Scroll (2Eh).............................................................................................................................. 46

10.2.4 Activate Scroll (2Fh).......................................................................................................... ........................ 46

10.2.5 Set Vertical Scroll Area(A3h) .................................................................................................................... 46

11 MAXIMUM RATINGS..........................................................................................................47

12 DC CHARACTERISTICS.....................................................................................................48

13 AC CHARACTERISTICS.....................................................................................................49

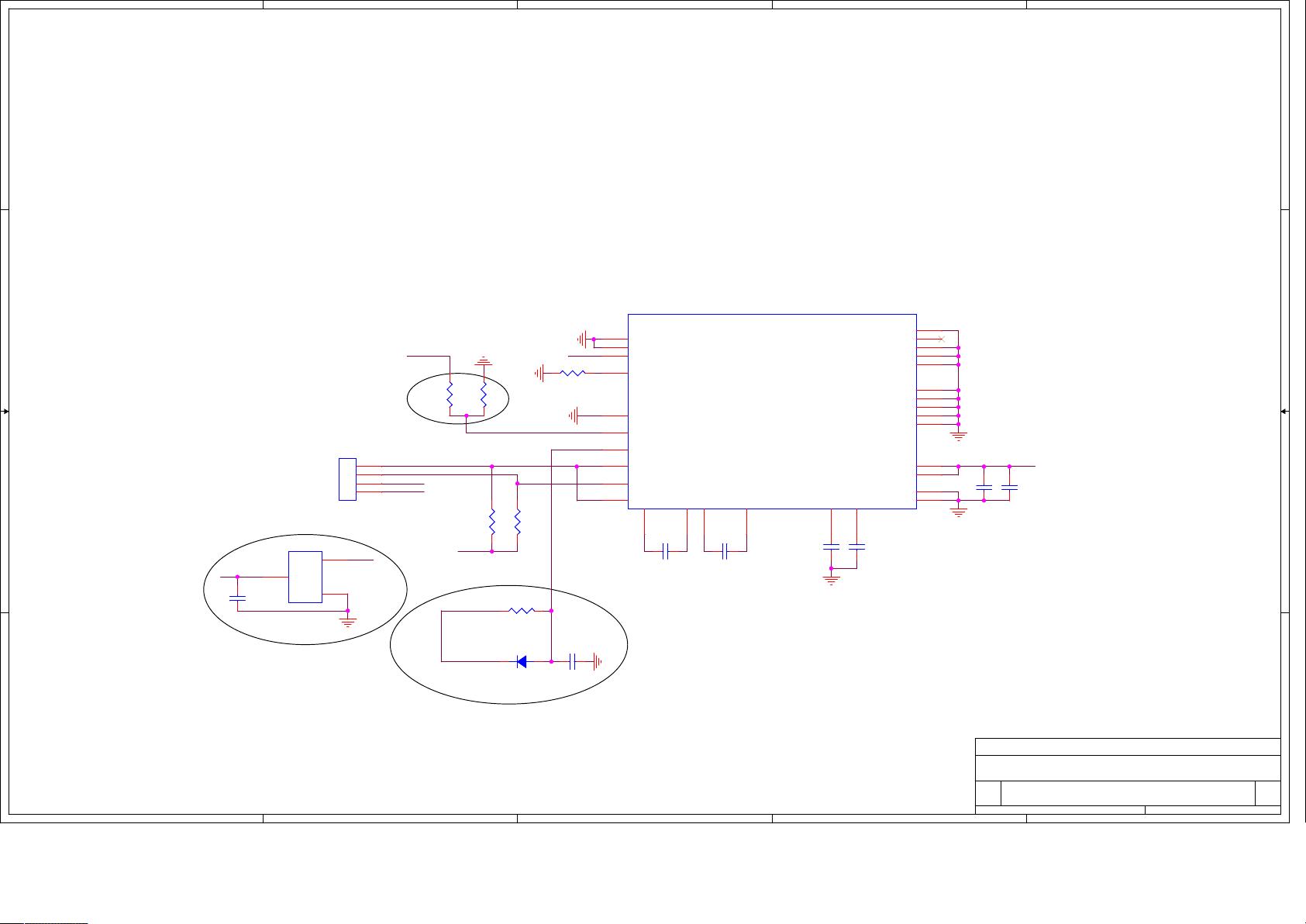

14 APPLICATION EXAMPLE..................................................................................................55

15 PACKAGE INFORMATION................................................................................................56

15.1 SSD1306TR1 DETAIL DIMENSION ..................................................................................................................... 56

15.2 SSD1306Z DIE TRAY INFORMATION.................................................................................................................. 58

Solomon Systech Apr 2008 P 4/59 Rev 1.1 SSD1306

TABLES

TABLE 5-1 : SSD1306Z BUMP DIE PAD COORDINATES...................................................................................................... 10

TABLE 6-1 : SSD1306TR1 PIN ASSIGNMENT TABLE.......................................................................................................... 12

TABLE 7-1 : MCU BUS INTERFACE PIN SELECTION............................................................................................................ 14

TABLE 8-1 : MCU INTERFACE ASSIGNMENT UNDER DIFFERENT BUS INTERFACE MODE ...................................................... 15

TABLE 8-2 : CONTROL PINS OF 6800 INTERFACE................................................................................................................. 15

TABLE 8-3 : CONTROL PINS OF 8080 INTERFACE................................................................................................................. 17

TABLE 8-4 : CONTROL PINS OF 4-WIRE SERIAL INTERFACE................................................................................................. 17

TABLE 8-5 : CONTROL PINS OF 3-WIRE SERIAL INTERFACE................................................................................................. 18

TABLE 9-1: COMMAND TABLE ........................................................................................................................................... 28

TABLE 9-2 : READ COMMAND TABLE................................................................................................................................. 33

TABLE 9-3 : ADDRESS INCREMENT TABLE (AUTOMATIC) ................................................................................................... 33

TABLE 10-1 : EXAMPLE OF SET DISPLAY OFFSET AND DISPLAY START LINE WITH NO REMAP.......................................... 38

TABLE 10-2 :EXAMPLE OF SET DISPLAY OFFSET AND DISPLAY START LINE WITH REMAP ................................................ 39

TABLE 10-3 : COM PINS HARDWARE CONFIGURATION ..................................................................................................... 40

TABLE 11-1 : MAXIMUM RATINGS (VOLTAGE REFERENCED TO VSS)................................................................................ 47

TABLE 12-1 : DC CHARACTERISTICS .................................................................................................................................. 48

TABLE 13-1 : AC CHARACTERISTICS .................................................................................................................................. 49

TABLE 13-2 : 6800-SERIES MCU PARALLEL INTERFACE TIMING CHARACTERISTICS......................................................... 50

TABLE 13-3 : 8080-SERIES MCU PARALLEL INTERFACE TIMING CHARACTERISTICS......................................................... 51

TABLE 13-4 : 4-WIRE SERIAL INTERFACE TIMING CHARACTERISTICS ................................................................................ 52

TABLE 13-5 : 3-WIRE SERIAL INTERFACE TIMING CHARACTERISTICS ................................................................................ 53

TABLE 13-6 :I

2

C INTERFACE TIMING CHARACTERISTICS.................................................................................................... 54

SSD1306 Rev 1.1 P 5/59 Apr 2008 Solomon Systech

FIGURES

FIGURE 4-1 SSD1306 BLOCK DIAGRAM .............................................................................................................................. 7

FIGURE 5-1 : SSD1306Z DIE DRAWING ............................................................................................................................... 8

FIGURE 5-2 : SSD1306Z ALIGNMENT MARK DIMENSIONS .................................................................................................... 9

FIGURE 6-1 : SSD1306TR1 PIN ASSIGNMENT ................................................................................................................. 11

FIGURE 7-1 PIN DESCRIPTION............................................................................................................................................. 13

FIGURE 8-1 : DATA READ BACK PROCEDURE - INSERTION OF DUMMY READ ....................................................................... 16

FIGURE 8-2 : EXAMPLE OF WRITE PROCEDURE IN 8080 PARALLEL INTERFACE MODE......................................................... 16

FIGURE 8-3 : EXAMPLE OF READ PROCEDURE IN 8080 PARALLEL INTERFACE MODE .......................................................... 16

FIGURE 8-4 : DISPLAY DATA READ BACK PROCEDURE - INSERTION OF DUMMY READ ......................................................... 17

FIGURE 8-5 : WRITE PROCEDURE IN 4-WIRE SERIAL INTERFACE MODE ............................................................................... 18

FIGURE 8-6 : WRITE PROCEDURE IN 3-WIRE SERIAL INTERFACE MODE ............................................................................... 18

FIGURE 8-7 : I

2

C-BUS DATA FORMAT .................................................................................................................................. 20

FIGURE 8-8 : DEFINITION OF THE START AND STOP CONDITION ......................................................................................... 21

FIGURE 8-9 : DEFINITION OF THE ACKNOWLEDGEMENT CONDITION ................................................................................... 21

FIGURE 8-10 : DEFINITION OF THE DATA TRANSFER CONDITION ......................................................................................... 21

FIGURE 8-11 : OSCILLATOR CIRCUIT AND DISPLAY TIME GENERATOR .............................................................................. 22

FIGURE 8-12 : SEGMENT OUTPUT WAVEFORM IN THREE PHASES ....................................................................................... 24

FIGURE 8-13 : GDDRAM PAGES STRUCTURE OF SSD1306................................................................................................ 25

FIGURE 8-14 : ENLARGEMENT OF GDDRAM (NO ROW RE-MAPPING AND COLUMN-REMAPPING)...................................... 25

FIGURE 8-15 : I

REF

CURRENT SETTING BY RESISTOR VALUE ............................................................................................. 26

FIGURE 8-16 : THE POWER ON SEQUENCE.......................................................................................................................... 27

FIGURE 8-17 : THE POWER OFF SEQUENCE ........................................................................................................................ 27

FIGURE 10-1 : ADDRESS POINTER MOVEMENT OF PAGE ADDRESSING MODE ..................................................................... 34

FIGURE 10-2 : EXAMPLE OF GDDRAM ACCESS POINTER SETTING IN PAGE ADDRESSING MODE (NO ROW AND COLUMN-

REMAPPING) ............................................................................................................................................................... 34

FIGURE 10-3 : ADDRESS POINTER MOVEMENT OF HORIZONTAL ADDRESSING MODE ......................................................... 35

FIGURE 10-4 : ADDRESS POINTER MOVEMENT OF VERTICAL ADDRESSING MODE .............................................................. 35

FIGURE 10-5 : EXAMPLE OF COLUMN AND ROW ADDRESS POINTER MOVEMENT .............................................................. 36

FIGURE 10-6 :TRANSITION BETWEEN DIFFERENT MODES .................................................................................................... 37

FIGURE 10-7 : HORIZONTAL SCROLL EXAMPLE: SCROLL RIGHT BY 1 COLUMN................................................................. 44

FIGURE 10-8 : HORIZONTAL SCROLL EXAMPLE: SCROLL LEFT BY 1 COLUMN ................................................................... 44

FIGURE 10-9 : HORIZONTAL SCROLLING SETUP EXAMPLE................................................................................................... 44

FIGURE 10-10 : CONTINUOUS VERTICAL AND HORIZONTAL SCROLLING SETUP EXAMPLE .................................................. 45

FIGURE 13-1 : 6800-SERIES MCU PARALLEL INTERFACE CHARACTERISTICS...................................................................... 50

FIGURE 13-2 : 8080-SERIES PARALLEL INTERFACE CHARACTERISTICS................................................................................ 51

FIGURE 13-3 : 4-WIRE SERIAL INTERFACE CHARACTERISTICS............................................................................................. 52

FIGURE 13-4 : 3-WIRE SERIAL INTERFACE CHARACTERISTICS............................................................................................. 53

FIGURE 13-5 : I

2

C INTERFACE TIMING CHARACTERISTICS.................................................................................................. 54

FIGURE 14-1 : APPLICATION EXAMPLE OF SSD1306Z ....................................................................................................... 55

FIGURE 15-1 SSD1306TR1 DETAIL DIMENSION ................................................................................................................ 56

FIGURE 15-2 : SSD1306Z DIE TRAY INFORMATION ............................................................................................................ 58