1 / 23

HUNAN UNIVERSITY

简易计算机系统综合设计

设 计 报 告

专业班级 计科 1905

学 号 201908010502

姓 名 林观田

2 / 23

一、设计目的

完整、连贯地运用《数字逻辑》所学到的知识,熟练掌握 EDA 工具基本使用方法,

为 学习好后续《计算机原理》课程做铺垫。

二、设计内容

① 按照给定的数据通路、数据格式和指令系统,使用 EDA 工具设计一台用硬连线逻

辑控制的简易计算机; ② 要求灵活运用各方面知识,使得所设计的计算机具有较佳的性能;

③ 对所设计计算机的性能指标进行分析,整理出设计报告。

④ 设计出各个部分的分部件,包括:

时序部件:指令寄存器 IR,C 寄存器,Z 寄存器,指令计数器 PC,时钟 SM,通用寄存器

组,IN 部件,OUT 部件,存储器 RAM

组合部件:ALU、指令译码器,控制器,位移逻辑,3-1 多路复用器。

三、 详细设计

3.1 设计的整体架构

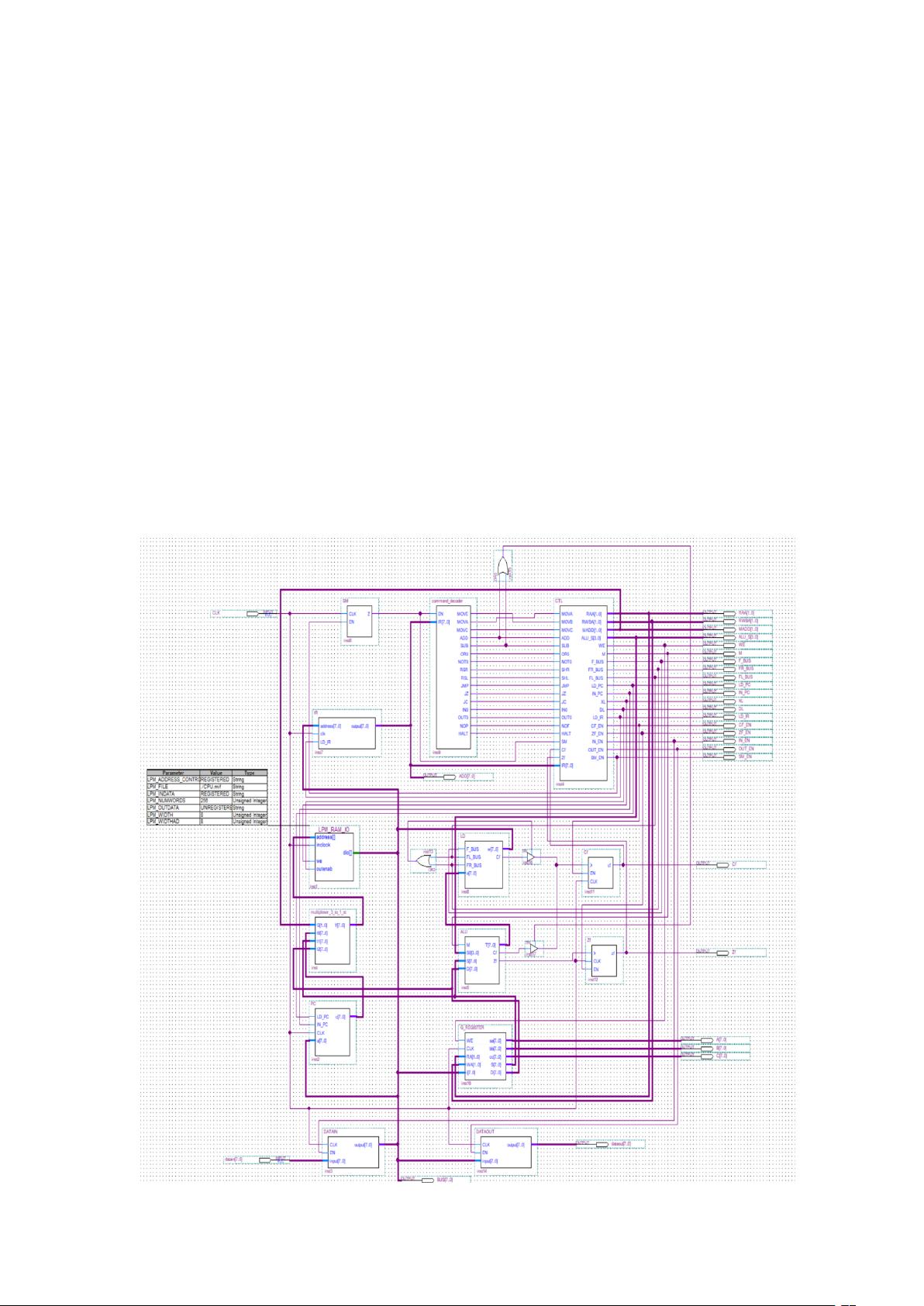

3.1.1 整个模型机分为 14 个模块,由若干个时序部件模块、组合逻辑电路模块以及三态门、

逻辑门组成。其中时序部件模块有 SM、指令寄存器 IR,存储器 RAM、指令计数器 PC、通

用寄存器 G_REGISTER、IN 模块、OUT 模块、Zf 模块、Cf 模块,组合逻辑电路模块有 8

重 3-1 多路复用器、指令译码器 command_decoder、控制信号模块 CTL、ALU、移位逻辑。

设计的模型机原理图如下:

3 / 23

3.1.2 数据格式与指令系统

3.1.2.1 数据格式

数据字采用 8 位二进制定点补码表示,其中最高位(第 7 位)为符号位,小数点可视为最

左或最右,其数值表示范围分别为:-1≤X<+1 或-128≤X<+127。

3.1.2.2 寻址方式

指令的高 4 位为操作码,低 4 位分别用 2 位表示目的寄存器和源寄存器的编号,或表示

寻址方式。共有 2 种寻址方式。

⑴ 寄存器直接寻址

当 R1 和 R2 均不是“11”时,R1 和 R2 分别表示两个操作数所在寄存器的地址(寄存

器 编号),其中 R1 为目标寄存器地址,R2 为源寄存器地址。

R1 或 R2 的值 指定的寄存器

00 A 寄存器

01 B 寄存器

10 C 寄存器

⑵ 寄存器间接寻址

当 R1 或 R2 中有一个为“11”时,表示相应操作数的地址在 C 寄存器中。

3.1.2.3 指令系统

指令系统有 16 条指令,具体格式见指令系统表。应该指出的是,各条指令的编码形式 可

以多种多样。为了叙述方便,下面采用汇编符号对指令进行描述,其中 R1 和 R2 分别表

示“目标”和“源”寄存器,M 表示地址在寄存器 C 中的存贮单元。

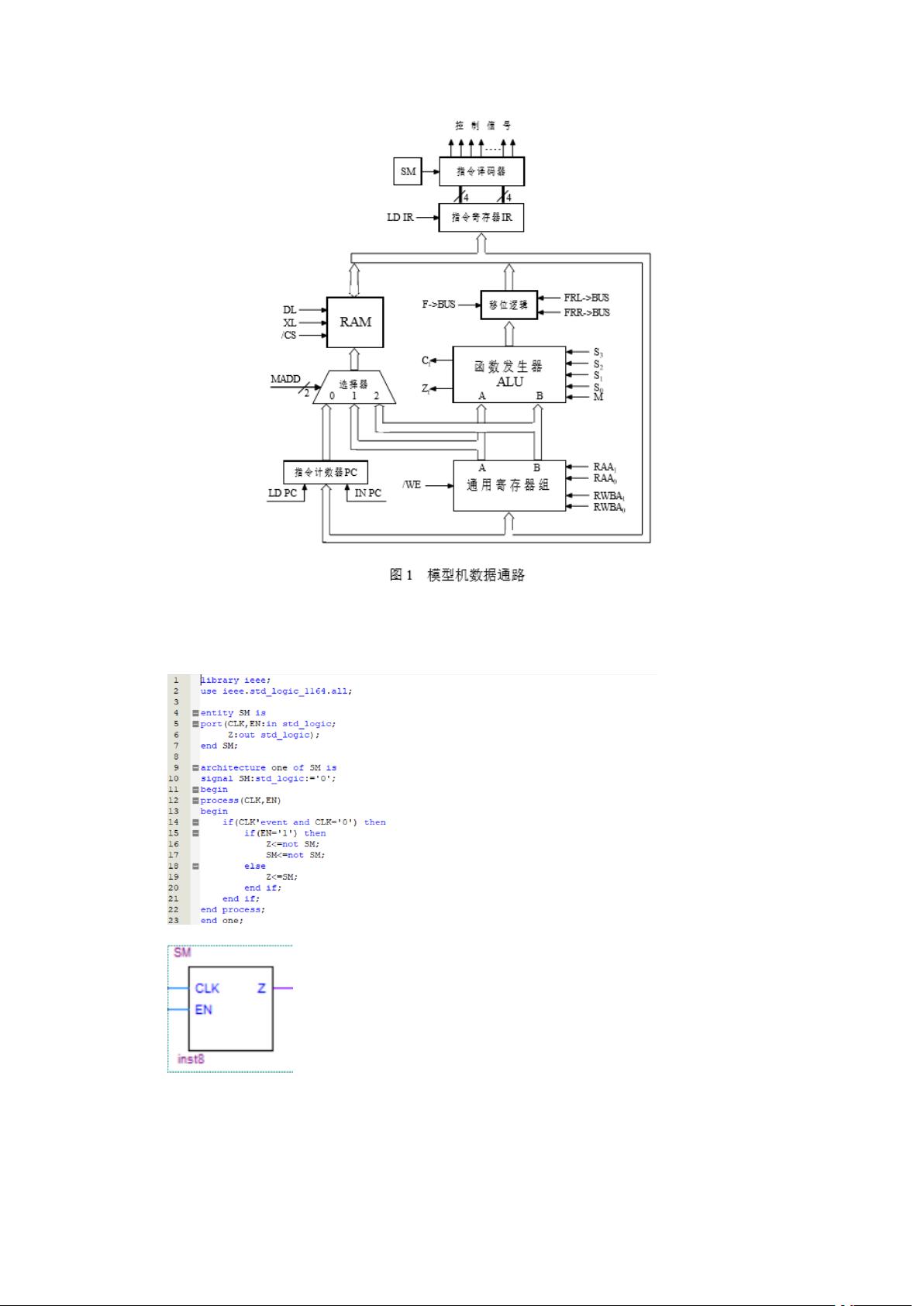

3.1.2.4 数据通路及其说明

计算机的工作过程可以看作是许多不同的数据流和控制流在机器各部分之间的流动,数据流

所经过的路径称作机器的数据通路。数据通路不同,指令执行所经过的操作过程就不同,机

器的结构也就不一样。如何设计一个好的数据通路已经超出了本课程的范围,在此我们不予

讨论。我们假设所设计的计算机的数据通路如图 1 所示。

4 / 23

3.2 各模块的具体实现

3.2.1SM 模块

1) VHDL 程序

2) 原理图&接口设计

此模块设计有两个输入接口,分别是时钟和使能信号接口,有一个输出接口,用于输出

模型机执行指令的控制信号。

3) 实现功能&功能验证

*实现的功能:

用于区分当前周期是取指令还是执行指令。

5 / 23

*功能验证:

由以上功能仿真波形图可知,

① 0-20ns:第一个时钟周期,Z 输出为初值 0;

② 20ns:第一个时钟下降沿,此时使能信号为 1,Z 的值取反为 1,输出 1;

③ 20-40ns:第二个时钟周期;

④ 40ns:第二个时钟下降沿,此时使能信号为 0,Z 的值保持不变,输出 1;

⑤ 40-60ns:第三个时钟周期;

⑥ 60ns:第三个时钟下降沿,此时使能信号为 0,Z 的值保持不变,输出 1;

⑦ 60-80ns:第四个时钟周期;

⑧ 80ns:第四个时钟下降沿,此时使能信号为 1,Z 的值取反为 0,输出 0。

3.2.2 指令计数器 PC

1) VHDL 程序

2)原理图&接口设计

此模块设计有四个输入接口,分别是时钟接口、两个使能信号接口以及加载总线中的数据接

口,有一个输出接口,用于输出地址。

4) 实现功能&功能验证

*实现的功能:

评论0