没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

3页

该设计思想与方法是学习龙芯Local IO接口的经典设计方法,特别适用于初学者: 1、给出了通过龙芯2K1000LIO接口外扩CAN、485、uart的设计架构; 2、给出了总线设计中地址与片选的设计原则; 3、给出采用“基地址+偏移地址”的方式对外设进行访问的思想; 4、给出将基地址作为片选使用的方法 5、作者全面阐释了这种通用设计思想,可以作为其他设计人员参考。

资源推荐

资源详情

资源评论

Name:总线设计思想 Author:Lisen Date:2022.05.21—

1 / 3

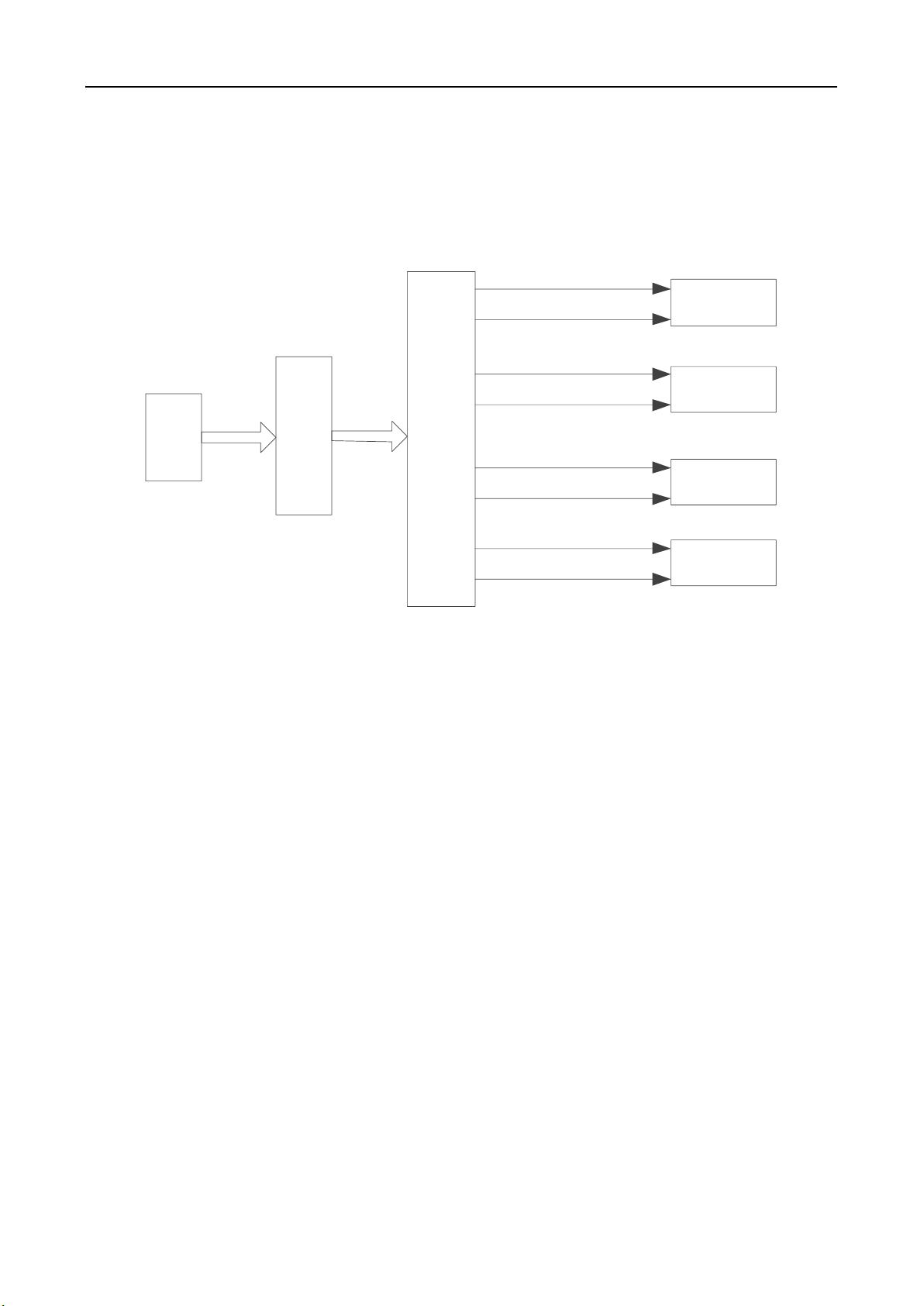

1. 基于 FPGA 的总线接口扩展设计

在使用 FPGA 对接口进行外扩的过程中,常需要对 CPU 接口进行转换处理,将与 CPU 通信的标准接

口,转换为与相应的外设模块进行通信的接口。外设模块中的通信接口设计为具有:write_en、data_in、

read_en、data_out、addr 这 5 大标准接口的模块。根据需要有时也需要添加 ready 信号,作为读取完毕的

指示信号。FPGA 外扩总线的设计结构:

CPU

各子

模块

地址

处

理、

片选

生成

CAN模块

485模块

ADC模块

1553B模块

CAN_EN/CAN_CS

CAN_data、CAN_addr

485_EN/485_CS

485_data、485_addr

ADC_EN/ADC_CS

ADC_data、ADC_addr

1553_EN/1553_CS

1553_data、1553_addr

LIO

接口

LIO

处

理

模

块

EN

data

addr

图 1 系统整体结构

1.1 接口设计的思路与方法

CPU 通过 LIO 接口去访问其他端口的处理与设计方法:

(1) 首先编写 LIO 处理模块,将 CPU 的 LIO 接口转换为 write_en、read_en、data_in、data_out、addr

5 部分;

(2) 根据 LIO 接口传递下来的地址,提取地址中的基地址部分生成下游每一个模块的片选、使能、地

址,因为上游传递进来的地址是包括基地址在内的地址,如果要生成相应模块的访问地址,则必须

将地址中的基地址部分剔除,只留下偏移地址,才是每一个模块的实际访问地址;

(3) 每个子模块只负责在自己地址对应关系的条件下,在读写使能的控制下,完成对模块的控制;

(4) 各个子模块片选、地址的处理,由外部独立模块集中处理,这样的设计更加灵活,在每一次对地址

空间进行重新映射时,我们只需要修改使能、地址处理模块,即可对地址空间进行重新映射;

1.2 片选、使能生成设计方法

在计算机系统中,CPU 对每一个外设的访问机制为:“基地址+偏移地址”的方式进行访问,基地址的分

配标准永远是从地址的最高位开始,从高到低进行使用,将高位作为基地址,利用基地址生成片选,去操

作相应的外设,也可以直接将基地址作为片选使用。再将生成的片选与读写使能信号相与,生成相应外设

的读写使能信号。

如:CPU 输出的地址为 32bit 地址,读写使能信号 write_en、read_en,外设为 3 个外设,则代码设计

为:

CAN:基地址 0x1000_0000;

ADC:基地址 0x2000_0000;

UART:基地址 0x3000_0000;

CWNULT

- 粉丝: 190

- 资源: 16

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

- 1

- 2

- 3

- 4

前往页