ARM7TDMI体系架构.pdf

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

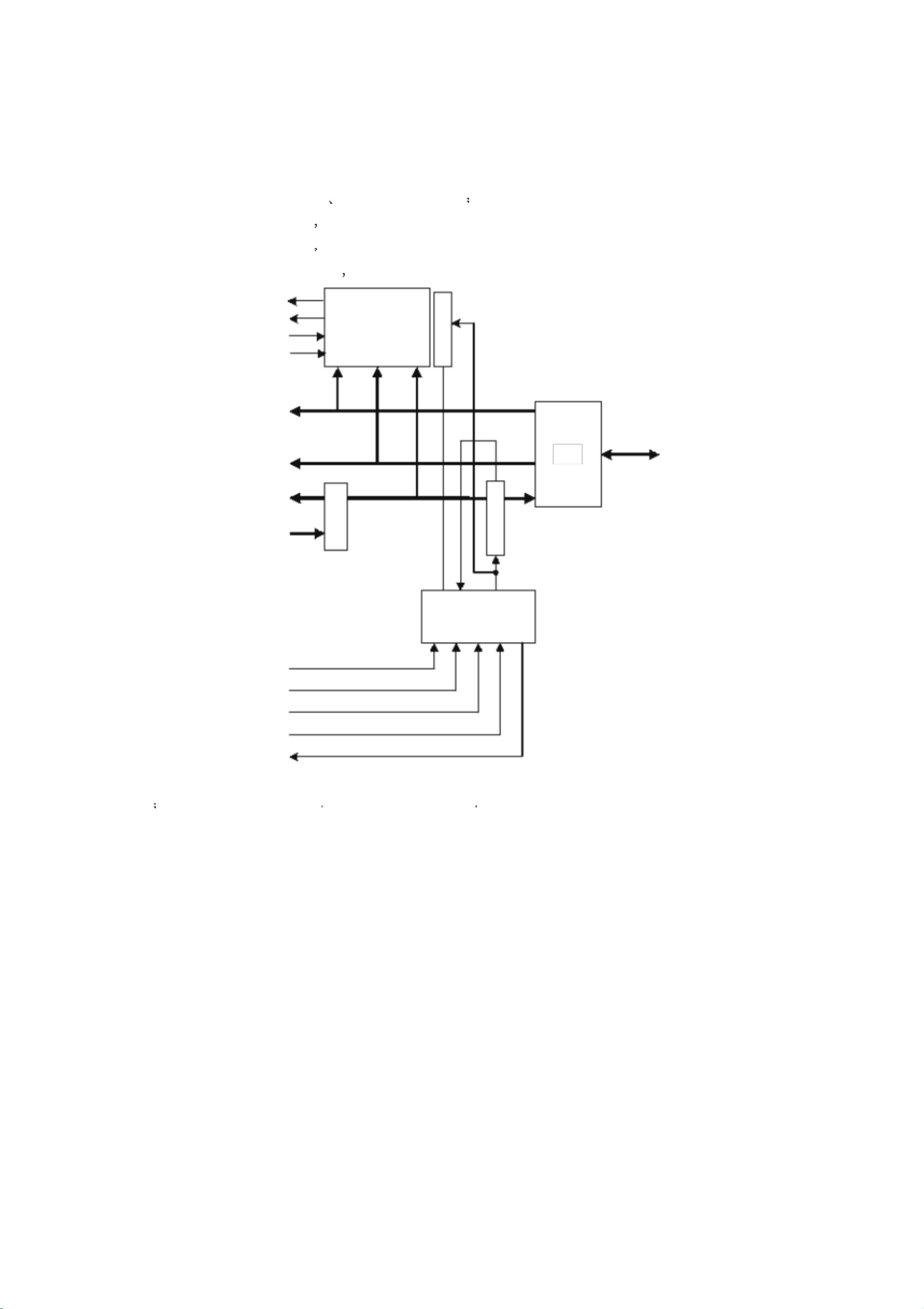

《ARM7TDMI体系架构》技术参考手册主要介绍了ARM7TDMI-S处理器的架构特点和工作原理,该处理器是ARM公司32位微处理器家族的一员,以其高效能、低功耗和小巧的门数设计著称。基于RISC(精简指令集计算机)设计理念,ARM7TDMI-S处理器拥有简洁的指令集和高效的译码机制,使得其在实时中断响应和指令吞吐量上表现出色。 1. **指令流水线**:处理器采用3阶段流水线设计,包括取指、译码和执行阶段,通过这种方式,可以在同一时间处理多条指令,提高处理速度。程序计数器(PC)在执行指令的同时,已经完成了下一条指令的译码和下下一条指令的取指,确保了指令流的连续性。 2. **冯诺依曼结构与存储器访问**:处理器遵循冯诺依曼架构,指令和数据共享32位总线。存储器访问支持8位字节、16位半字和32位字的读写,字和半字的分配需按4字节和2字节对齐。为了优化性能,处理器的存储器接口采用了流水线技术,支持快速突发访问模式,适应不同类型的片内和片外存储器。 3. **存储器接口与周期类型**:存在四种基本的存储器周期类型:内部周期、非连续周期、连续周期和协处理器寄存器传输周期,这使得处理器能够灵活地处理各种内存操作。 4. **ARM7TDMI-S结构**:处理器包含32位ARM指令集和16位Thumb指令集。ARM指令集用于高性能处理,而Thumb指令集则通过16位指令实现更高的代码密度,同时保持接近32位ARM指令的性能。Thumb指令集是ARM指令的子集,每个16位Thumb指令对应一条32位ARM指令,它们使用相同的寄存器配置,确保了良好的状态互用性。由于Thumb指令的高效性和代码密度,ARM7TDMI-S处理器特别适合资源有限且代码密度要求高的嵌入式应用。 5. **指令压缩与性能**:与传统16位结构相比,Thumb指令集在32位结构上实现,提供更高的性能和代码密度。尽管Thumb代码的大小只有ARM代码的65%,但其执行效率相当于16位存储器系统的ARM处理器的160%,为设计者提供了在性能和代码规模之间优化选择的灵活性。 6. **模块内核与功能框图**:手册中还包含了ARM7TDMI-S模块的内核和功能框图,详细展示了处理器的硬件构成,包括Embedded ICE-RT(嵌入式ICE实时调试)、CPU调试接口、调试范围、外部调试扩展等组件,为开发者提供了深入理解处理器内部工作原理的视觉参考。 ARM7TDMI-S处理器通过优化的指令流水线、高效的存储器访问机制、灵活的指令集以及精巧的硬件结构,实现了高效能与低功耗的平衡,是嵌入式系统设计的理想选择。

剩余49页未读,继续阅读

- 粉丝: 17

- 资源: 26万+

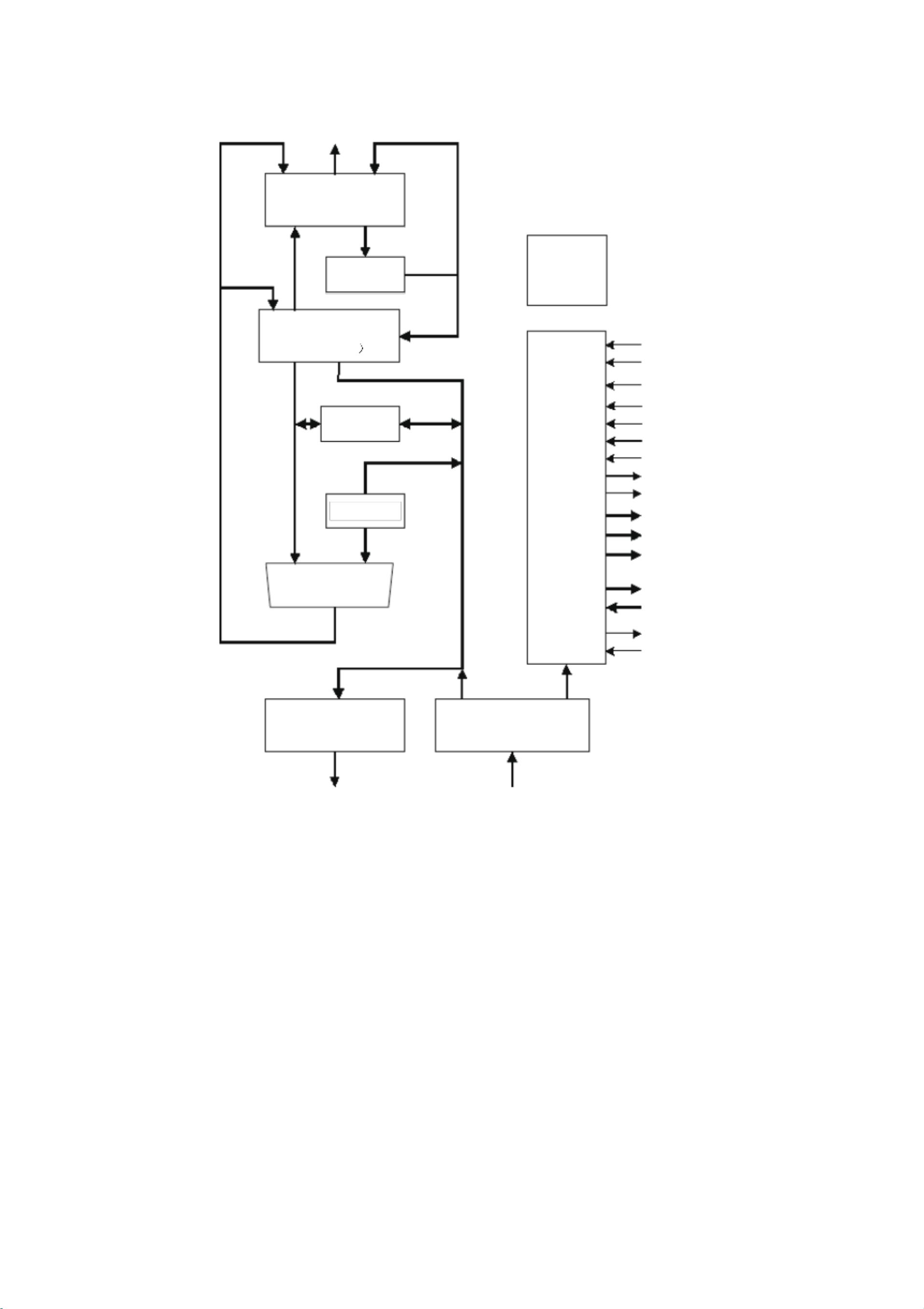

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- dataCollection-资源文件

- Java-Interview-Advanced-啊哦111

- Pear Admin Layui-资源文件

- 1615-1.6米写真机(数码印花机) sw14可编辑全套技术资料100%好用.zip

- FDG-A1∕D-56电子防盗保险柜sw16可编辑全套技术资料100%好用.zip

- A17038产品自动锁螺丝机sw17可编辑全套技术资料100%好用.zip

- 半自动U型上止焊接机(sw16可编辑+工程图)全套技术资料100%好用.zip

- 四工位高速塞棉机sw18全套技术资料100%好用.zip

- 消磁生产线sw17可编辑全套技术资料100%好用.zip

- 2.5mm铜箔焊线机sw19可编辑全套技术资料100%好用.zip

- 20T双级级水处理设备step全套技术资料100%好用.zip

- C语言编程实现不同类型的圣诞树

- HTML与JavaScript实现圣诞节飘雪效果代码详解

- 20米双层倍速链sw18可编辑全套技术资料100%好用.zip

- MC-160袋式除尘器sw18可编辑全套技术资料100%好用.zip

- 毕业设计-基于Flask健身论坛 详细文档+全部资料+高分项目.zip

信息提交成功

信息提交成功