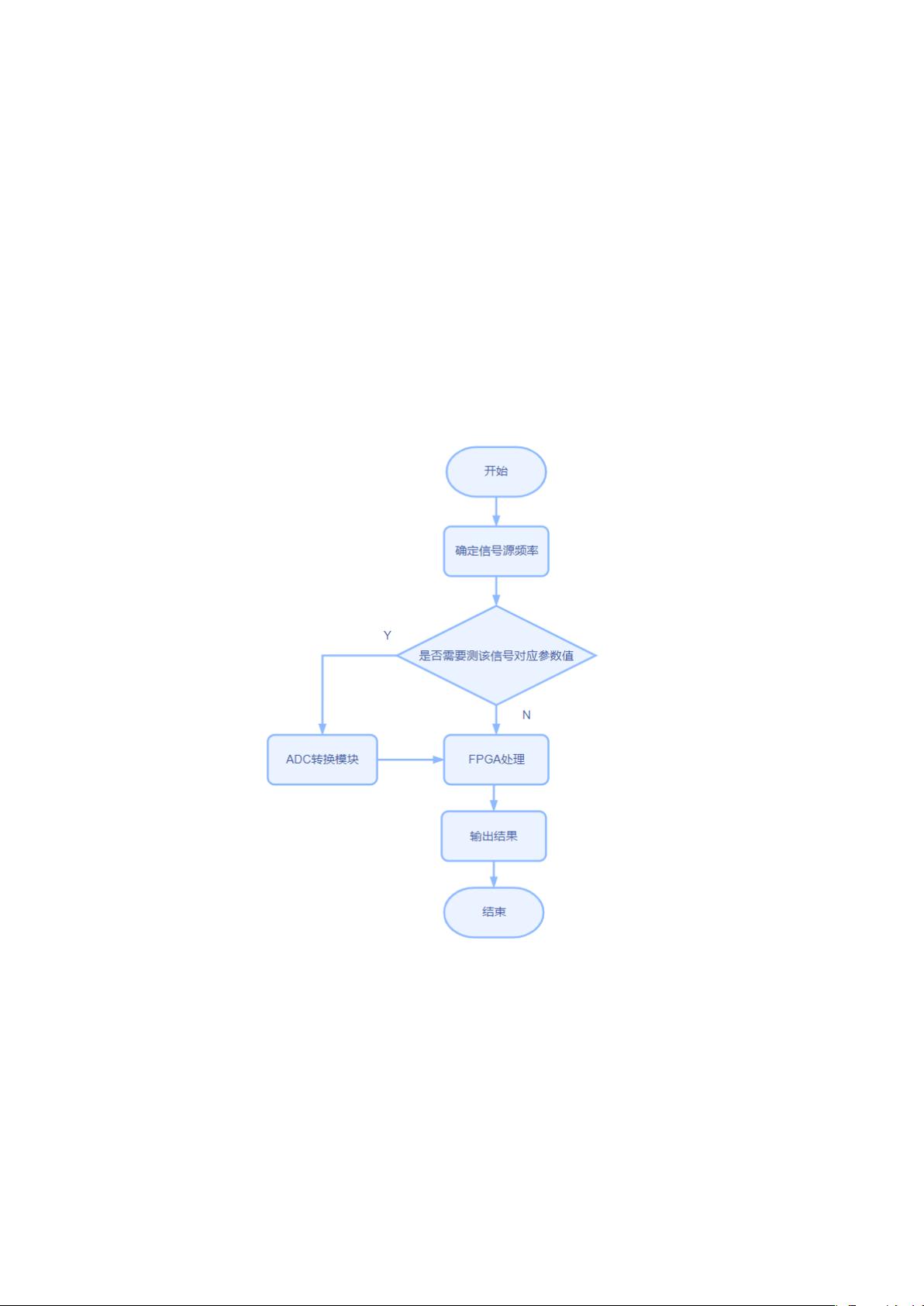

信号采集

假设信号源频率为 1Mhz~400Mhz(需要用示波器测试一下该信号最大输出频率),如果

该信号频率已经达到该量级,该信号已经近似模拟信号

1. 如需测量该信号的幅值,则需要添加一个 ADC 模数转换芯片(问题 1:如需测量信号幅

值何种 ADC 采样芯片能承受 400Mhz 的信号);

2. 如不需要该信号幅值,那么可以直接和 FPGA 相接,只采集 0,1 电平判断上升沿和下降

沿(问题 2:理论上采集一个信号只需要频率达到该信号的 2 倍即可,但工程上最好为

该信号源频率的 5~10 倍,则 400Mhz 信号则需要 FPGA 内部时钟信号倍频到 2Ghz~4Ghz,

但市面上最好的 FPGA 芯片也就能倍频到 400-700M 左右,基本 900M 左右是极限,也

就是说内部时钟频率如果信号源最大频率为 400Mhz 或者更高则只能达到该数据源频率

的 1.5~2 倍左右如果无法在硬件上突破,则需要在逻辑上处理);

3. 问题 3:为保证采样信号无偏移,该传感器是否有内部时钟信号,或者起始位信号;

4. 添加分压电路。

数据采集流程图