FPGA(Kintex-7)学习笔记

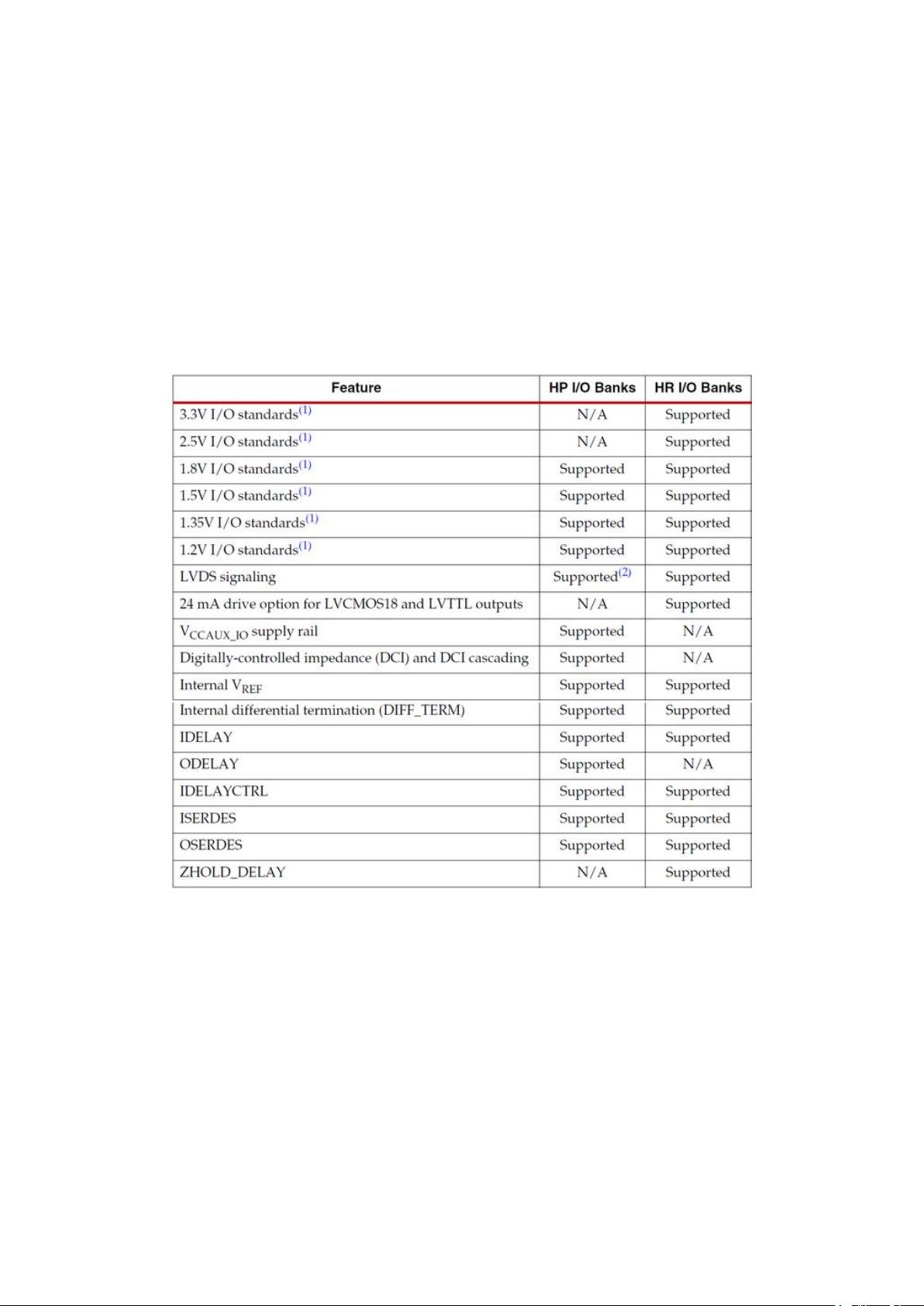

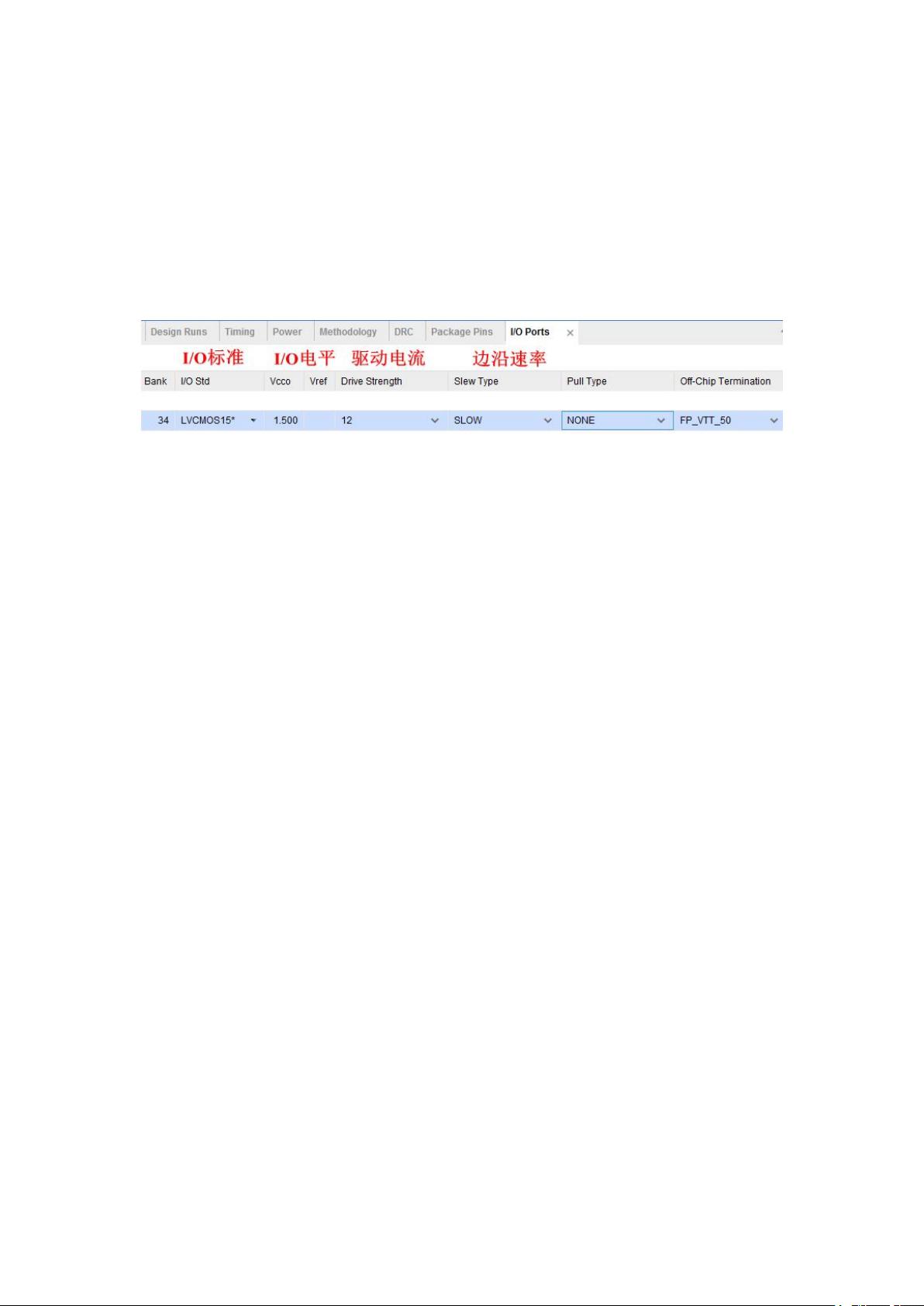

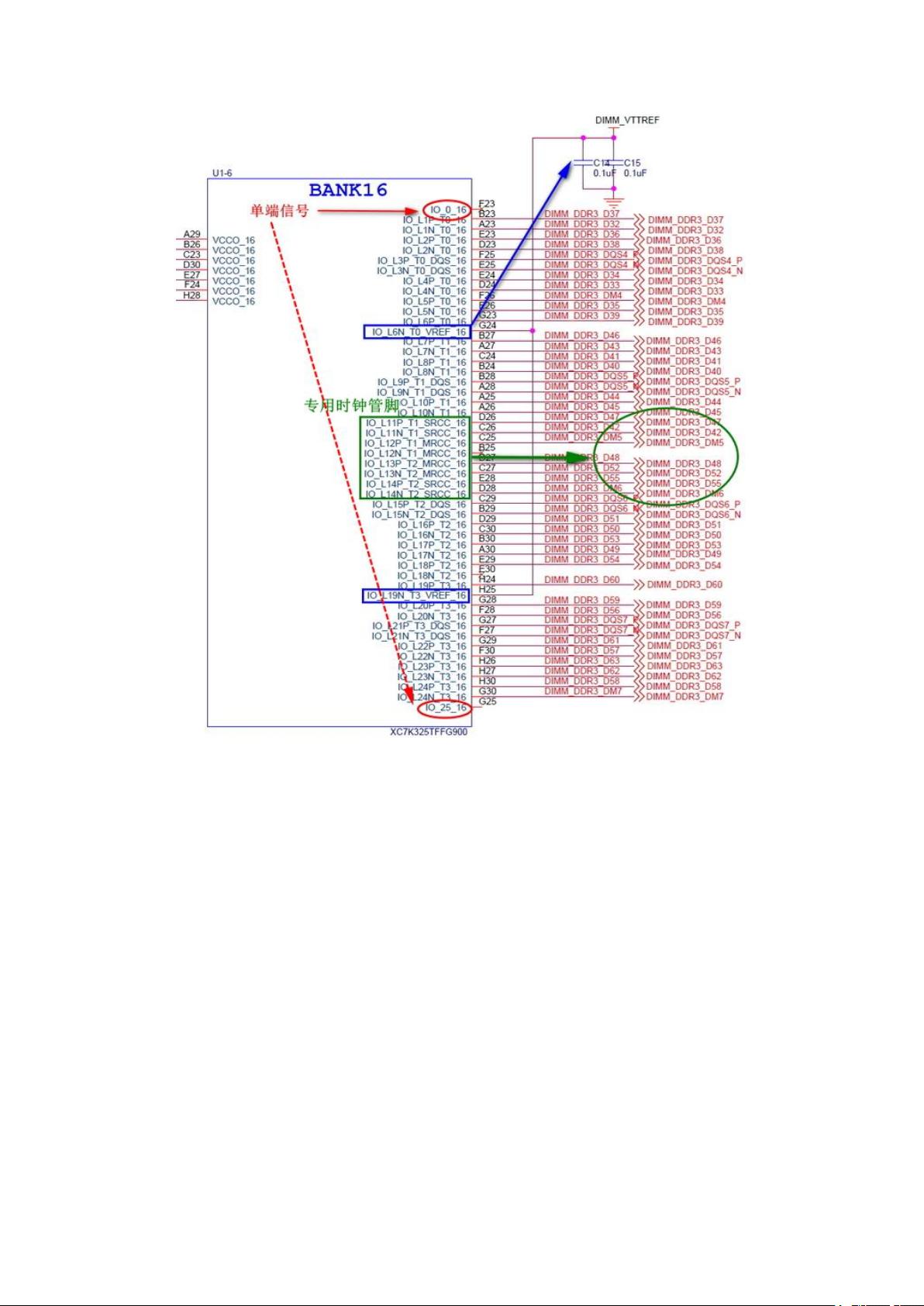

在FPGA(Field-Programmable Gate Array)学习过程中,Kintex-7系列是一个重要的研究对象,尤其在I/O接口的设计与应用方面。Kintex-7 FPGA的I/O系统由高性能(High Performance, HP)和宽范围(High Range, HR)两大类bank组成,它们各自具有独特的特性和功能。 HP I/O banks专门设计用于实现高速存储器接口和芯片间通信,如PCIe等,支持的最大电压为1.8V。而HR I/O banks则具备更广泛的I/O电平兼容性,最高可达3.3V,适合于不同电压标准的接口需求。值得注意的是,并非所有I/O标准和电流驱动强度在HP和HR banks中都得到支持,例如LVDS虽然通常被视为2.5V标准,但在两者中都能使用。 Kintex-7系列FPGA的SelectIO资源是其I/O配置的核心,它提供了可配置的驱动器和接收器,支持多种可变标准接口,包括可编程的输出电流、边沿速率、DCI(差分电流注入)片上端接和内部参考电压(INTERNAL_VREF)。然而,HR banks并不包含DCI功能,所以依赖DCI的应用需选择其他bank。 每个I/O bank通常包含50个SelectIO管脚,其中两个仅支持单端I/O,剩下的48个可以配置为48个单端或24对差分I/O。SelectIO管脚可以配置为输入、输出或三态模式,适应不同的信号类型,如单端I/O标准(LVCMOS、LVTTL、HSTL、PCI、SSTL)和差分I/O标准(Mini_LVDS、RSDS、PPDS、BLVDS、差分HSTL和SSTL)。 在硬件结构上,HP I/O banks有两种类型:一种只能配置为单端信号,另一种则是常规结构,既支持单端也支持差分信号。而HR I/O banks则相对简单,仅支持单端信号配置。这些不同类型的IOB结构图在原文中通过图4至图11进行了详细展示。 在设计指导方面,7系列FPGA的I/O bank布局规则是关键。每个bank包含50个IOB资源,bank的数量根据器件的大小和封装决定。例如,XC7K325T有10个可用的I/O banks。此外,Vcco电源管脚是I/O电路的主要电压,同一bank内的所有Vcco必须连接到相同电压,确保所有I/O管脚在同一电平下工作。Vcco应与选用的I/O标准电压匹配,否则可能导致器件损坏。在HP bank中,如果Vcco过高,器件会自动进入过压保护模式,调整至正确电平后恢复正常。单端I/O标准可能需要VREF作为参考电压,而全局辅助电压Vccaux为内部逻辑和某些I/O标准提供电源,Vccaux_io则是针对HP bank的辅助电压,其电压设置与存储器接口的频率有关。 配置期间和配置后的I/O状态管理也是设计中的重要环节。7系列FPGA在配置过程中,I/O状态需要被初始化,配置完成后则根据设计需求进行相应的设置。对于未使用的I/O,通常应将其配置为三态,避免产生不必要的信号干扰。 理解和掌握Kintex-7 FPGA的SelectIO结构及设计指导对于FPGA开发者至关重要,这将直接影响到系统的性能、兼容性和可靠性。在实际应用中,需要根据具体需求合理选择I/O bank,正确配置I/O参数,以确保系统稳定运行。

剩余20页未读,继续阅读

- 粉丝: 1w+

- 资源: 32

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

信息提交成功

信息提交成功