没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

1

1

第5章 触发器

组合逻辑电路:任何时刻产生的稳定输出信号仅仅取决于

该时刻电路的输入信号,而与该时刻以前的输入信号无关。组

合电路无记忆功能,电路不能储存与过去输入有关的信息。

组合逻辑电路

a

1

a

2

a

n

.

.

.

.

.

.

y

1

y

2

y

m

时序逻辑电路:任何时刻输出的稳定值,不仅与该时刻的

输入信号有关,而且与该时刻以前的输入信号有关。

如:自动售饮料机器,取款机,抢答器等。

存储器件,

存储单元电路

5.1 概述

在逻辑数字电路中,绝大部分存储单元都是双稳态电路。

1. 具有两个稳定状态,无外加信号作用,电路常期处于某

一稳定状态。

2. 有(一个或多个)激励输入端,在外加信号激励下,电

路从一种稳定状态转换到另一稳定状态,以后即使外加

激励信号消失,稳定状态仍能保持下去。

最常用的存储单元有两类:

一类是锁存器:复位Reset-置位Set锁存器.

一类是触发器:除激励输入端外,还有1个时钟控制输入

端Clock.

如电脑开关键

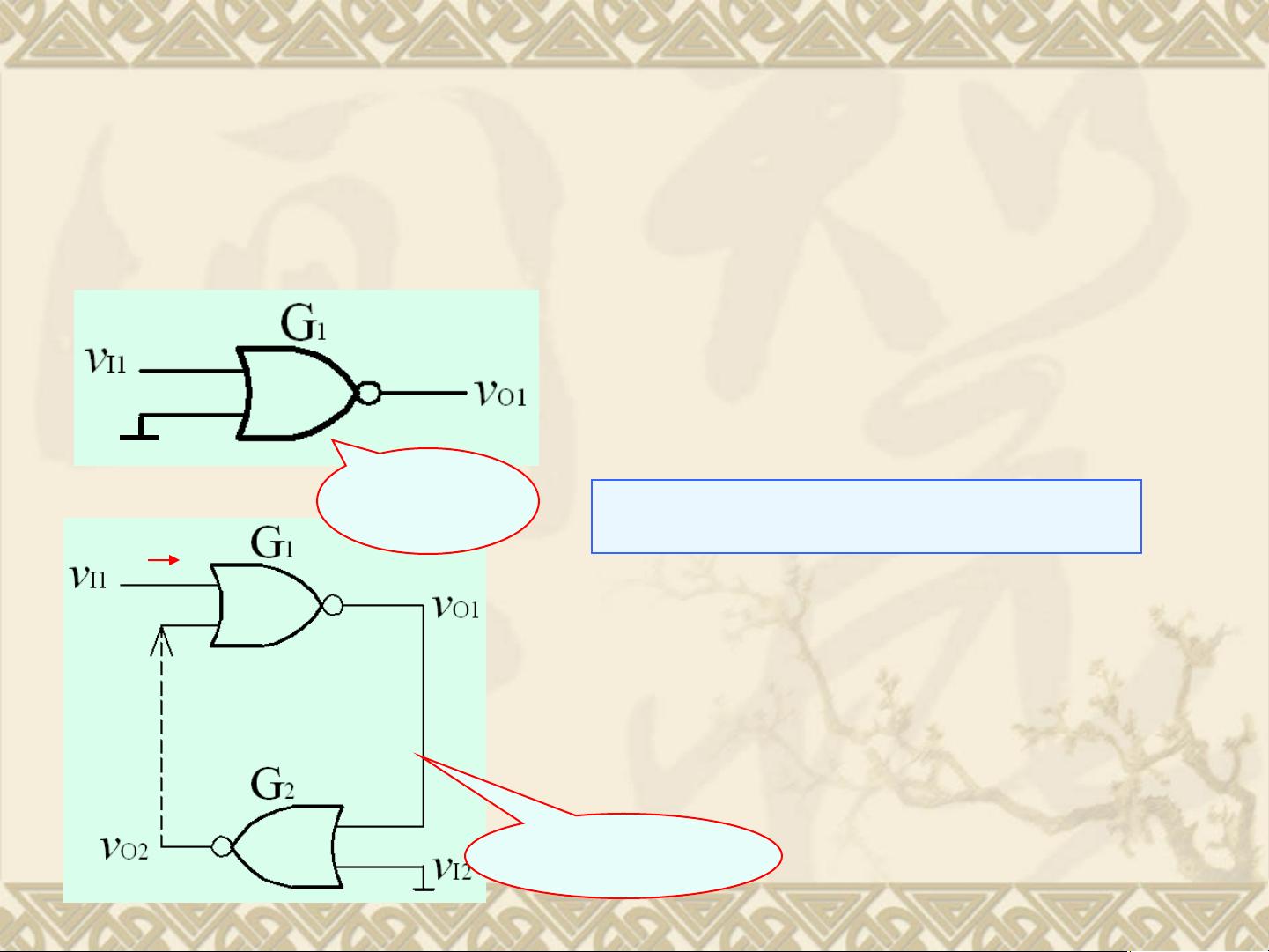

一、电路结构与工作原理:

5.2 SR锁存器

或非门:一个输入端固定,

输出将随另一个输入端的改

变而改变。

门电路不具备记忆功能

反相器

用

G

2

门将

V

O1

反相,并接

G

1

的

另一个输入端;则

V

I1

信号消

失,

V

O1

的低电平和

V

O2

的高

电平也能保持。

1

0

1

0

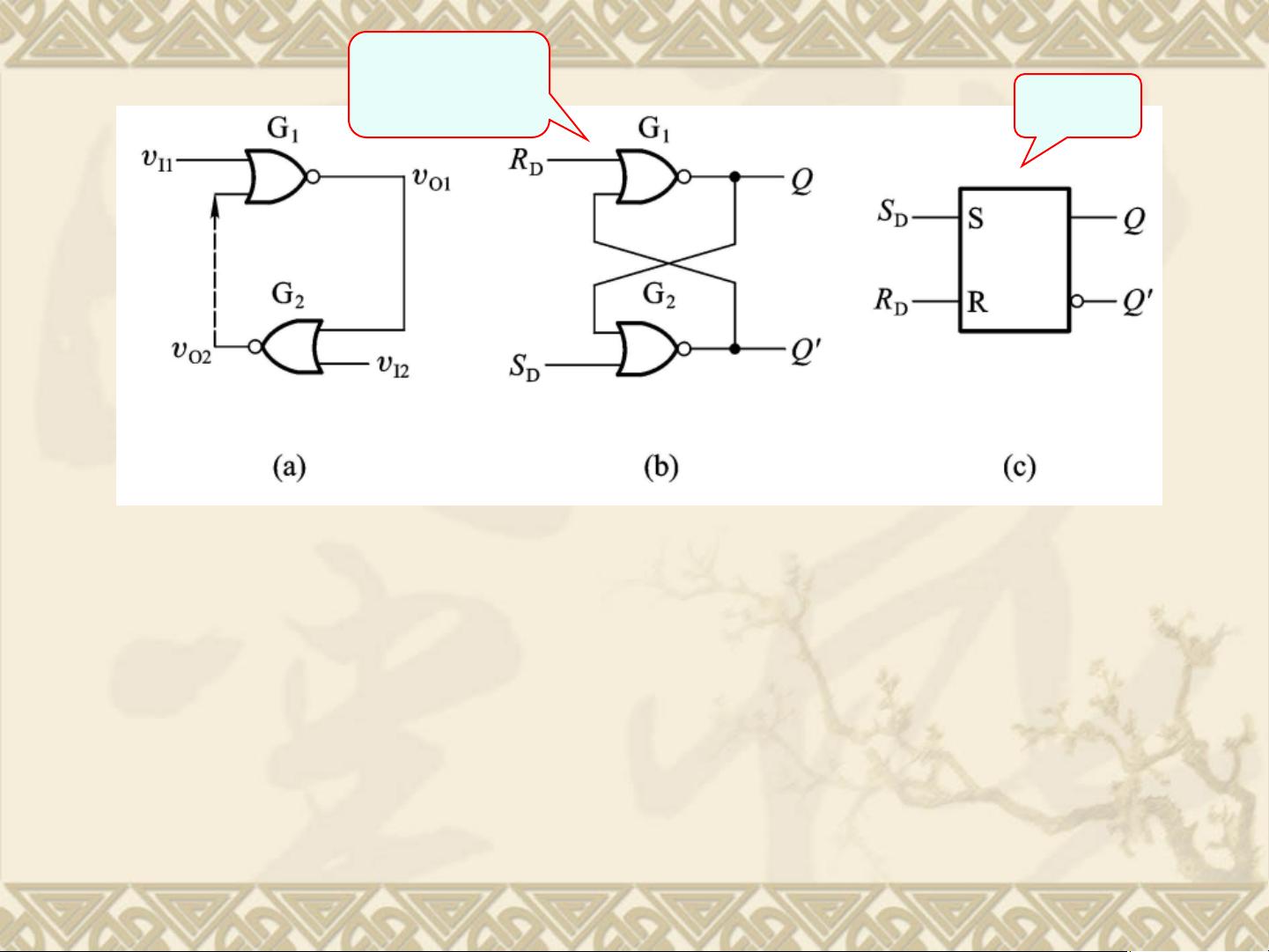

SR锁存器

SR锁存器由两个交叉耦合的或非门(与非门构成)。

SR

锁存器:是各种触发器的基本组成部分,有两个

能自行保持的稳定状态。

S

D

、R

D

为激励输入端,定义输出端的

Q

=1、

Q’

=0

为锁存器的1状态,

Q

=0、

Q’

=1为锁存器的0状态。

SR锁存器

原理图

符号

剩余125页未读,继续阅读

资源评论

一只小小的土拨鼠

- 粉丝: 2w+

- 资源: 315

下载权益

C知道特权

VIP文章

课程特权

开通VIP

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功