2

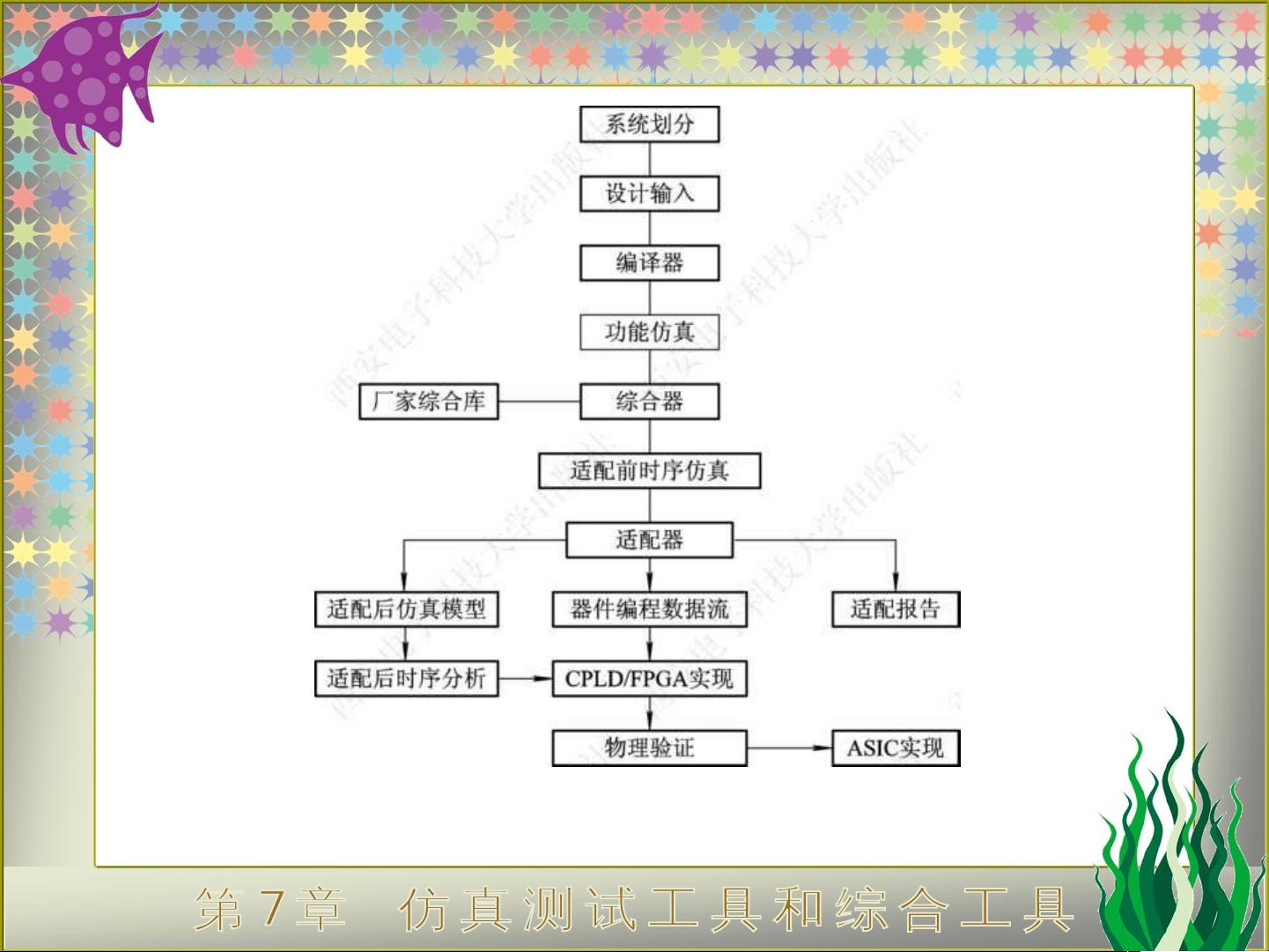

在数字集成电路设计过程中,设计者使用 Verilog HD

L 硬件描述语言进行关键性步骤的开发和设计。其基本过

程是,首先使用 Verilog HDL 对硬件电路进行描述性设计,

利用 EDA 综合工具将其综合成一个物理电路,然后进行

功能验证、定时验证和故障覆盖验证。

4.1 Verilog HDL 语言的设计思

想和可综合特性

3

与计算机软件所采用的高级程序语言 (C 语言 ) 类似,

Verilog HDL 是一种高级程序设计语言,程序编写较简单,

设计效率很高。然而,它们面向的对象和设计思想却完全

不同。

软件高级程序语句是对通用型处理器 ( 如 CPU) 的编

程,主要是在固定硬件体系结构下的软件化程序设计。处

理器的体系结构和功能决定了可以用于编程的固定指令集,

设计人员的工作是调用这些指令,在固化的体系结构下实

现特定的功能。

4

Verilog HDL 和 VHDL 等硬件描述语言对电路的设

计是将基本的最小数字电路单元 ( 如门单元、寄存器、存

储器等 ) 通过连接方式,构成具有特定功能的硬件电路。

在数字集成电路中,这种最小的单元是工艺厂商提供的设

计标准库或定制单元;在 FPGA 中,这种最小的单元是芯

片内部已经布局的基本逻辑单元。设计人员通过描述性语

言调用和组合这些基本单元实现特定的功能,其基本的电

路是灵活的。

5

Verilog HDL 给设计者提供了几种描述电路的方法。

设计者可以使用结构性描述方式把逻辑单元互连在一起进

行电路设计,也可以采用抽象性描述方式对大规模复杂电

路进行设计,如对有限状态机、数字滤波器、总线和接口

电路的描述等。

由于硬件电路的设计目标是最终产生的电路,因此

Verilog HDL 程序设计的正确性需要通过对综合后电路的

正确性进行验证来实现。逻辑上相同的电路在物理电路中

的形式却有可能完全不同。对于 Verilog HDL 程序设计而

言,数字电路的描述性设计具有一定的设计模式,这与 C

语言等高级软件程序设计是不同的。

- 1

- 2

- 3

- 4

前往页