第二章 DSP 芯片结构和 CPU 外围电路

讲课内容:

1 ) TMS320C55x 处理器的特点

2 ) TMS320C55x 处理器的 CPU 结构

3 ) TMS320C55x 处理器的 CPU 外围电路

2.1 DSP 芯片结构

第二章 DSP 芯片结构和 CPU 外围电路

第二章 DSP 芯片结构和 CPU 外围电路

2.1 DSP 芯片结构

2.1.1 TMS320C55x 处理器的特点

采用改进的哈佛结构。 1 条读程序数据总线 (PB) , 5 条数据总线 (B

B,CB,DB,EB,FB) ,和他们对应的 6 条地址总线 (PAB,BAB,CAB,

DAB,EAB,FAB)

40 位和 16 位的算术逻辑单元 (ALU) 各 1 个 , 1 个 40 位的移位器

4 个 40 位的累加器 (AC0,AC1,AC2,AC3) 和 (T0,T1,T2,T3)

17×17 比特的硬件乘法器和一个 40 比特专用加法器的组合 (MAC)

比较、选择和存储单元

数据地址产生单元 (DAGEN) 和程序地址产生单元 (PAGEN)

数据空间和和程序空间位同一物理空间,采用统一编址

第二章 DSP 芯片结构和 CPU 外围电路

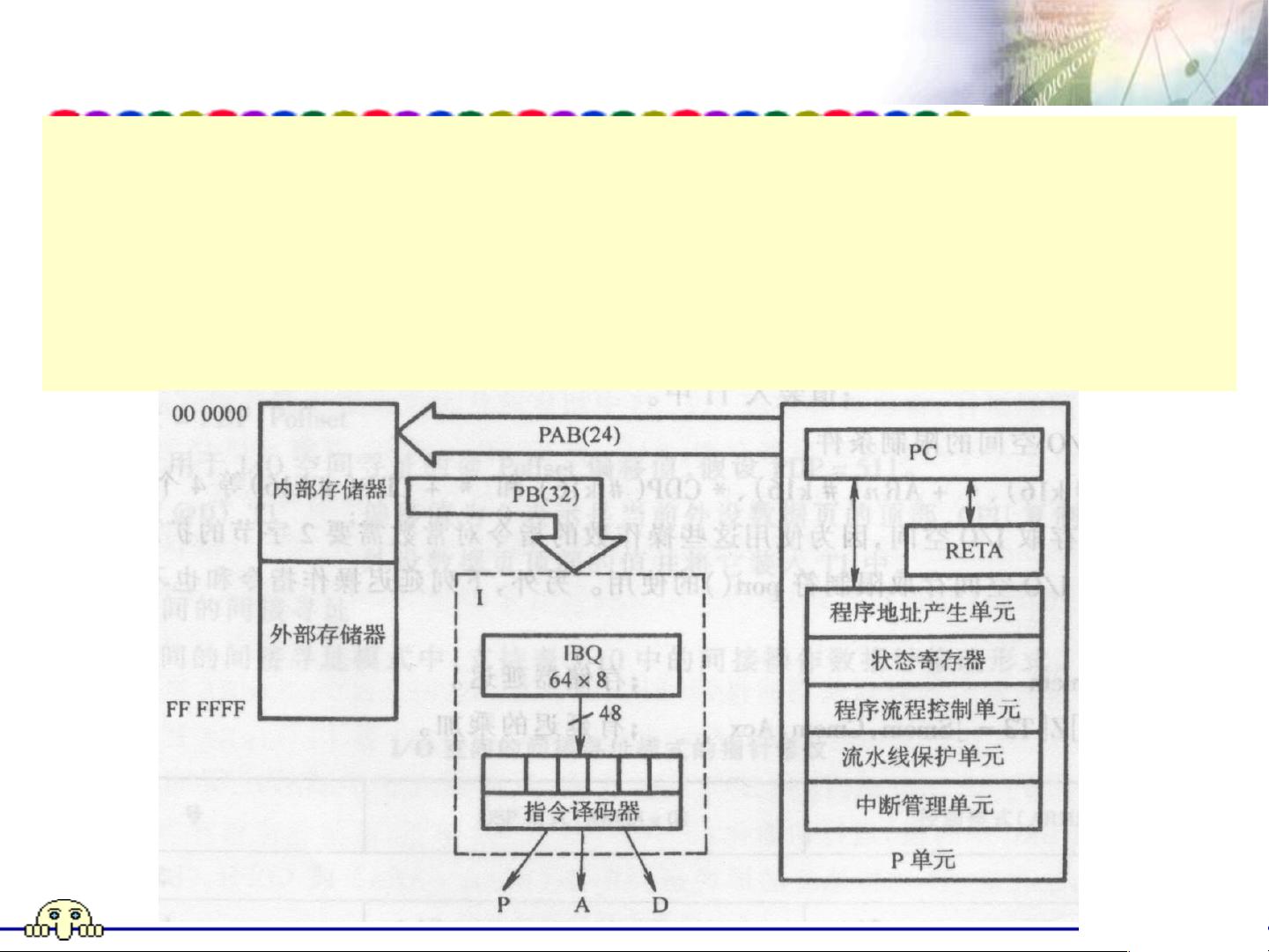

2.1.2 TMS320C55x CPU

CPU 有 4 个功能单元:指令缓冲单元 (I 单元 ) ,程序流程单元 (P 单元 ) ,

地址数据流程单元 (A 单元 ) 和数据计算单元 (D 单元 )

CPU 结构示意图

第二章 DSP 芯片结构和 CPU 外围电路

1 、指令缓冲单元 (I Unit)

由指令缓冲队列 (IBQ) 和指令

译码器构成。

I 单元从程序数据总线接收

程序指令代码 ( 每次接收 32 比

特程序代码 ) 放到 IBQ( 最多可存

放 64 字节的未译码指令 ) 中。

指令译码器从指令缓冲队

列中取指令 ( 每次取 6 字节的程

序代码 ) 进行变长 8/16/24/3

2/48 位)指令译码。

译码后的数据分别送到 P

单元, A 单元, D 单元处理。

指令缓冲单元( I 单元)

图