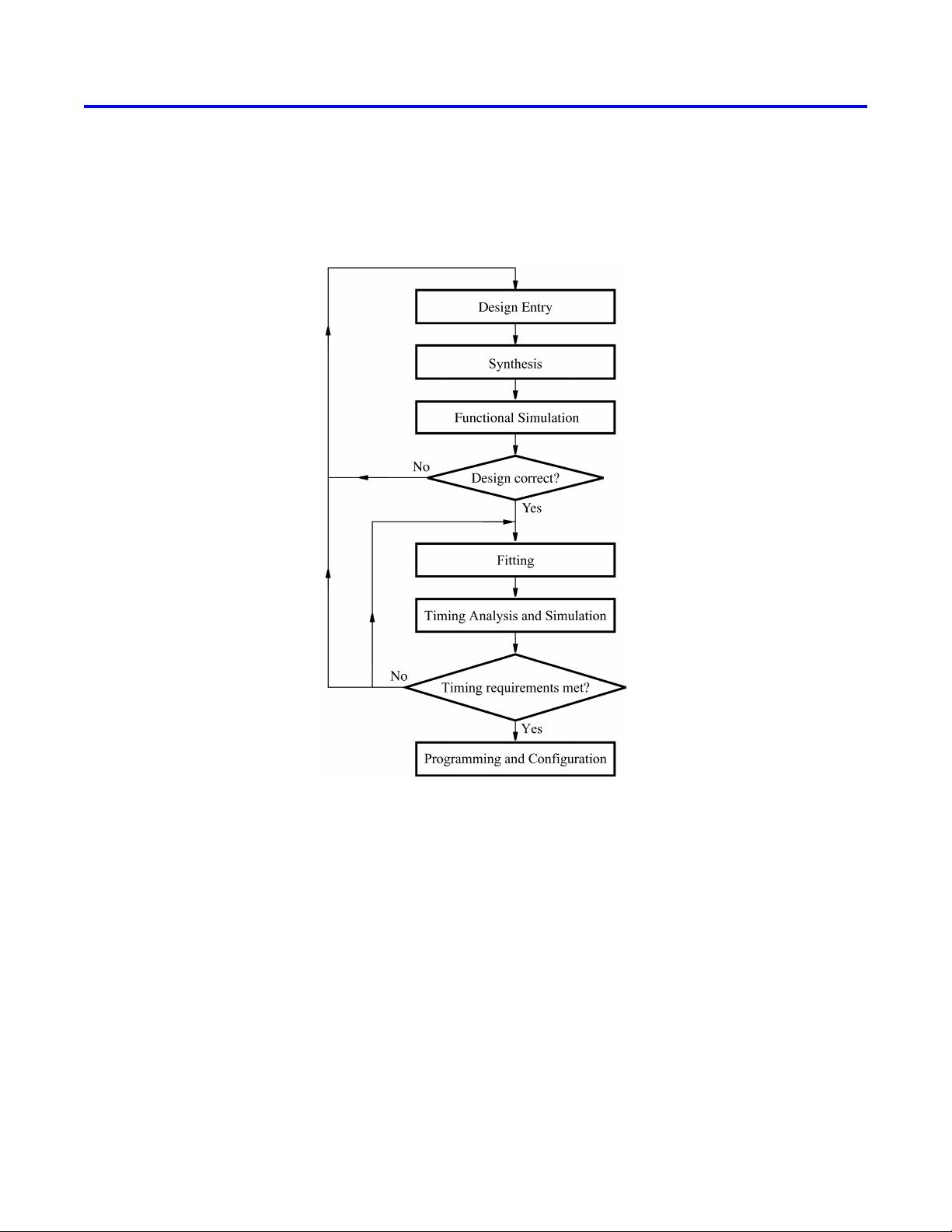

Quartus 软件界面介绍与部分使用技巧 Quartus Prime 是一款功能强大且广泛应用于 FPGA 设计的电子设计自动化(EDA)软件。下面将对 Quartus Prime 软件的界面进行介绍,并提供一些使用技巧。 1. Quartus Prime 界面介绍 Quartus Prime 的界面主要由六个部分组成:工具栏、项目管理器、设计入口、 PROPERTY Editor、信息中心和输出窗口。工具栏提供了常用的操作按钮,例如新建项目、打开项目、保存项目等。项目管理器用来管理项目的文件结构和设计单元。设计入口是 Quartus Prime 的核心组件,用于编写 Verilog 代码和设计电路。PROPERTY Editor 用来编辑设计单元的属性。信息中心提供了关于设计的信息,例如警告、错误和日志。输出窗口显示编译和仿真的结果。 2. 使用 Verilog 设计电路 Quartus Prime 支持多种设计入口方法,包括 Verilog、VHDL 和图形化设计。Verilog 是一种广泛应用于数字电路设计的硬件描述语言。使用 Verilog,可以快速设计和实现复杂的数字电路。Quartus Prime 提供了 Verilog 模板,可以快速创建新的设计项目。 3. 创建新的设计项目 要创建新的设计项目,需要在 Quartus Prime 中新建一个项目,然后添加设计文件。可以使用 Quartus Prime 的文本编辑器编写 Verilog 代码。Verilog 代码可以使用 Quartus Prime 的模板快速创建。例如,可以使用 Quartus Prime 的计数器模板快速创建一个计数器电路。 4. 编译和仿真设计电路 在设计电路完成后,需要编译和仿真设计电路。Quartus Prime 提供了强大的编译和仿真功能,可以快速检查设计电路的正确性。在编译过程中,Quartus Prime 会检查设计电路的语法和逻辑错误,并提供错误信息。如果设计电路存在错误,需要修改设计电路并重新编译。 5. 程序和配置 FPGA 设备 在设计电路完成和编译后,需要将其程序和配置到 FPGA 设备中。Quartus Prime 提供了多种编程和配置方法,例如 JTAG 编程和.getActive serialization。可以根据实际情况选择合适的编程和配置方法。 6. 测试设计电路 在设计电路程序和配置到 FPGA 设备后,需要测试设计电路。可以使用 Quartus Prime 的测试功能来测试设计电路。测试结果可以帮助设计者快速检查设计电路的正确性。 Quartus Prime 是一个功能强大且广泛应用于 FPGA 设计的 EDA 软件。通过本教程,可以快速掌握 Quartus Prime 的使用方法和技巧,从而提高 FPGA 设计的效率和质量。

剩余27页未读,继续阅读

- 粉丝: 515

- 资源: 12

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 自考02197概率论与数理统计(二)试卷及答案解释2016-2021

- java毕设项目之游戏分享网站lw(完整前后端+说明文档+mysql).zip

- java毕设项目之ssm助学贷款+jsp(完整前后端+说明文档+mysql+lw).zip

- IBM Instana应用性能监视.pptx

- webview+H5来实现的android短视频(短剧)音视频播放依赖控件资源

- 黑马最新Hive存储压缩与优化课程总结

- 商城系统项目源代码全套技术资料.zip

- 番茄图像目标检测数据【已标注,约4,300张数据,YOLO 标注格式】

- 校园生活相关项目源代码全套技术资料.zip

- C语言上机实验_1.pptx

- 基于遗传算法求解TSP问题的研究 50个样本点

- 基于XGBoost的振动数据预警模型与参数优化技术-构建一个基于XGBoost的振动信息数据集预警模型 首先引入算法实现动态阈值设置,然后进行参数优化

- sublimeText 4

- 西红柿叶片缺陷分类数据集【已标注,约500张数据】

- 自考00023《高等数学(工本)》试题及答案及复习资料

- 智能点阵笔项目源代码全套技术资料.zip

信息提交成功

信息提交成功