Systemverilog-Verification-Me

2.虚拟产品一经售出概不退款(资源遇到问题,请及时私信上传者)

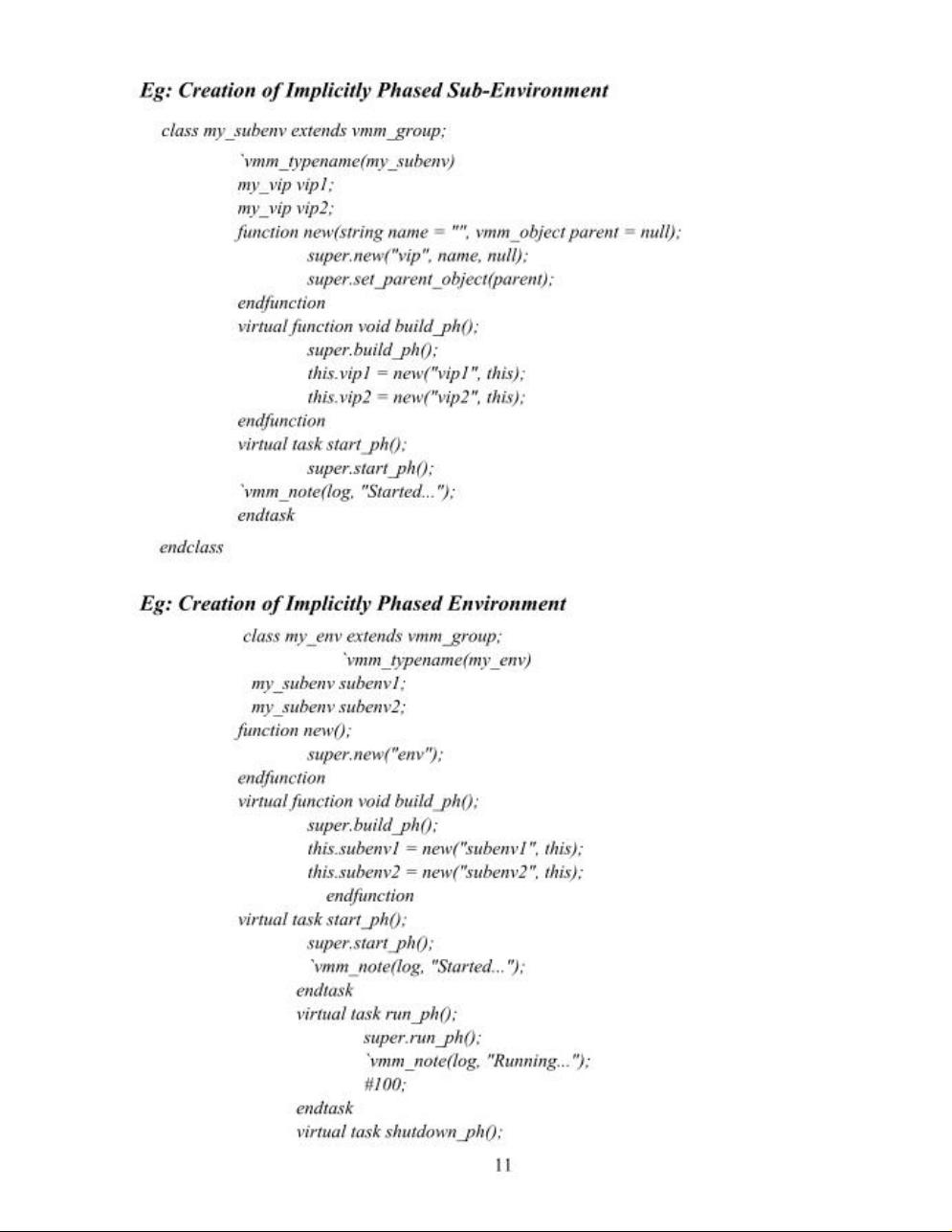

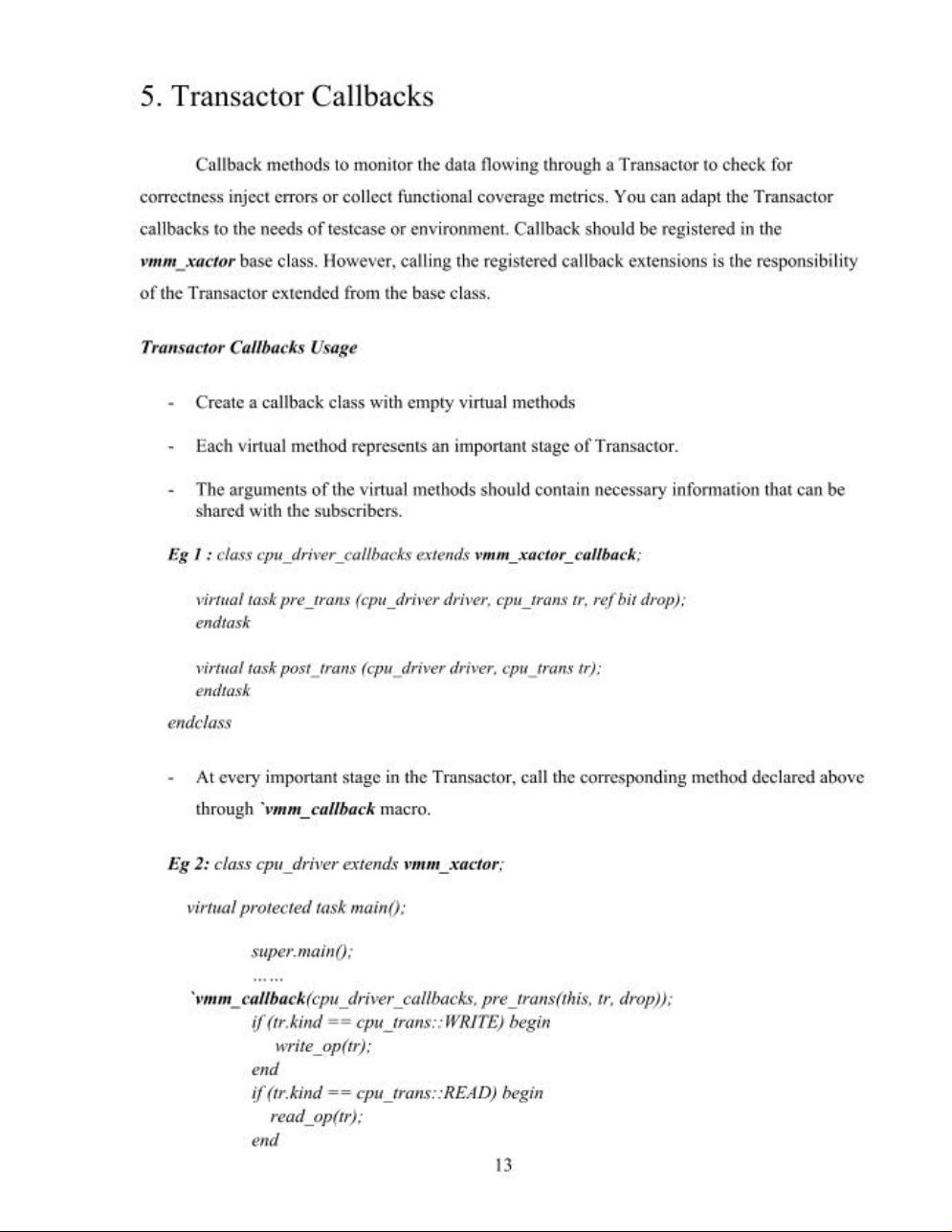

"Systemverilog-Verification-Me" 涉及的主题是Systemverilog在验证领域的应用,特别是 Verification Methodology Manual (VMM1.2) 的相关内容。Systemverilog是一种强大的硬件描述语言,广泛用于集成电路设计和验证。VMM1.2是Systemverilog的一种验证方法学,它为系统级验证提供了统一的框架和工具集。 "Systemverilog_Verification_Methodology_Manual(VMM1.2)共36页.pdf.zip" 指出,这是一份关于Systemverilog验证方法学VMM1.2的详细手册,共有36页。通常,这样的手册会涵盖VMM1.2的核心概念、基本组件、设计流程、以及如何利用Systemverilog进行高效验证的实践指导。PDF文档的形式意味着信息是结构化的,易于阅读和查阅。 在Systemverilog验证方法学VMM1.2中,你可能会学到以下关键知识点: 1. **Systemverilog基础**:Systemverilog的基本语法,包括类、接口、任务、函数、覆盖点等,这些都是构建验证环境的基础。 2. **验证组件**:VMM1.2提供了一系列预定义的验证组件,如代理(Agent)、驱动(Driver)、断言(Assertion)和随机化器(Randomizer),它们用于模拟和验证目标设计的行为。 3. **环境模型**:VMM1.2强调基于组件的验证环境构建,允许设计者快速搭建可重用的验证环境,以模拟真实世界的应用场景。 4. **协作机制**:VMM1.2中的事件和消息机制允许不同组件之间的通信和同步,确保验证的完整性。 5. **覆盖率**:VMM1.2提供了覆盖度收集和分析的框架,帮助验证工程师评估验证的完整性。 6. **类库**:VMM1.2的类库包含各种实用工具,如异常处理、数据包处理和事务序列管理,有助于提升验证效率。 7. **复用和扩展性**:VMM1.2设计时考虑了复用性和扩展性,使得新的验证需求可以方便地融入现有环境。 8. **最佳实践**:手册可能还会包含验证流程的最佳实践,如验证计划、验证策略和调试技巧,这些都是提高验证效率的关键。 9. **案例研究**:实际的示例和案例研究将帮助理解VMM1.2在实际项目中的应用。 由于压缩包中提到的"赚钱项目"与主题不相符,无法在此处进一步展开讨论。但总体来说,深入理解和掌握Systemverilog VMM1.2能够提升你在硬件验证领域的专业技能,对于参与和领导复杂设计项目具有重大价值。

Systemverilog_Verification_Methodology_Manual(VMM1.2)共36页.pdf.zip (1个子文件)

Systemverilog_Verification_Methodology_Manual(VMM1.2)共36页.pdf.zip (1个子文件)  赚钱项目

赚钱项目  吃不胖.知识分享

吃不胖.知识分享  吃不胖.CSDN知识分享

吃不胖.CSDN知识分享  Systemverilog_Verification_Methodology_Manual(VMM1.2)共36页.pdf 2.07MB

Systemverilog_Verification_Methodology_Manual(VMM1.2)共36页.pdf 2.07MB- 1

- 粉丝: 1w+

- 资源: 4万+

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 安卓期末大作业-android垃圾分类app项目源码(高分项目).zip

- 基于go语言和vue3的简易图书管理系统.zip

- XYZ7-Matlab Code.zip

- 基于go语言与websocket实现的简易聊天室.zip

- 基于Go语言Gin框架的订单管理系统,正在建设中,本身为简单Demo,有助于掌握Go语言语法以及Gin开发框架简单使用,喜欢就点个Star吧!.zip

- 基于go-cqhttp的易语言SDK.zip

- 18717844379-2402241500.awb

- 基于Eytion的语言,在沿着用了Eytion的部分内容的基础上,做出了结构,制定得更加简洁,易懂.zip

- 基于C语言的简单在线词典.zip

- 基于C语言Socket编程的简易公告发布程序.zip

信息提交成功

信息提交成功