XVC(Xilinx Virtual Cable)调研报告

1. 调研背景

当前的原型验证系统多采用的是 FPGA+ZYNQ 的方式,利用网口远程实现对 FPGA 的配置和对

用户代码的验证。现阶段我们采用的是 selectmap 加载实现远程向 FPGA 加载 bit 文件。但是

由于 xilinx 官方并未直接提供 selectmap 的 IP,以及公司自研的 selectmap IP 在稳定性和安全

性上欠佳,所以急需一种安全稳定的远程加载 bit 文件的方法。XVC(Xilinx Virtual Cable)方

案指的是 zynq 的网口通过 xvc-driver 和 Debug-Bridge IP 来访问 FPGA,鉴于是 Xilinx 官方所提

供的 IP 及方案,并经过多年的版本更新和迭代,渐趋稳定,所以针对 XVC 进行调研。

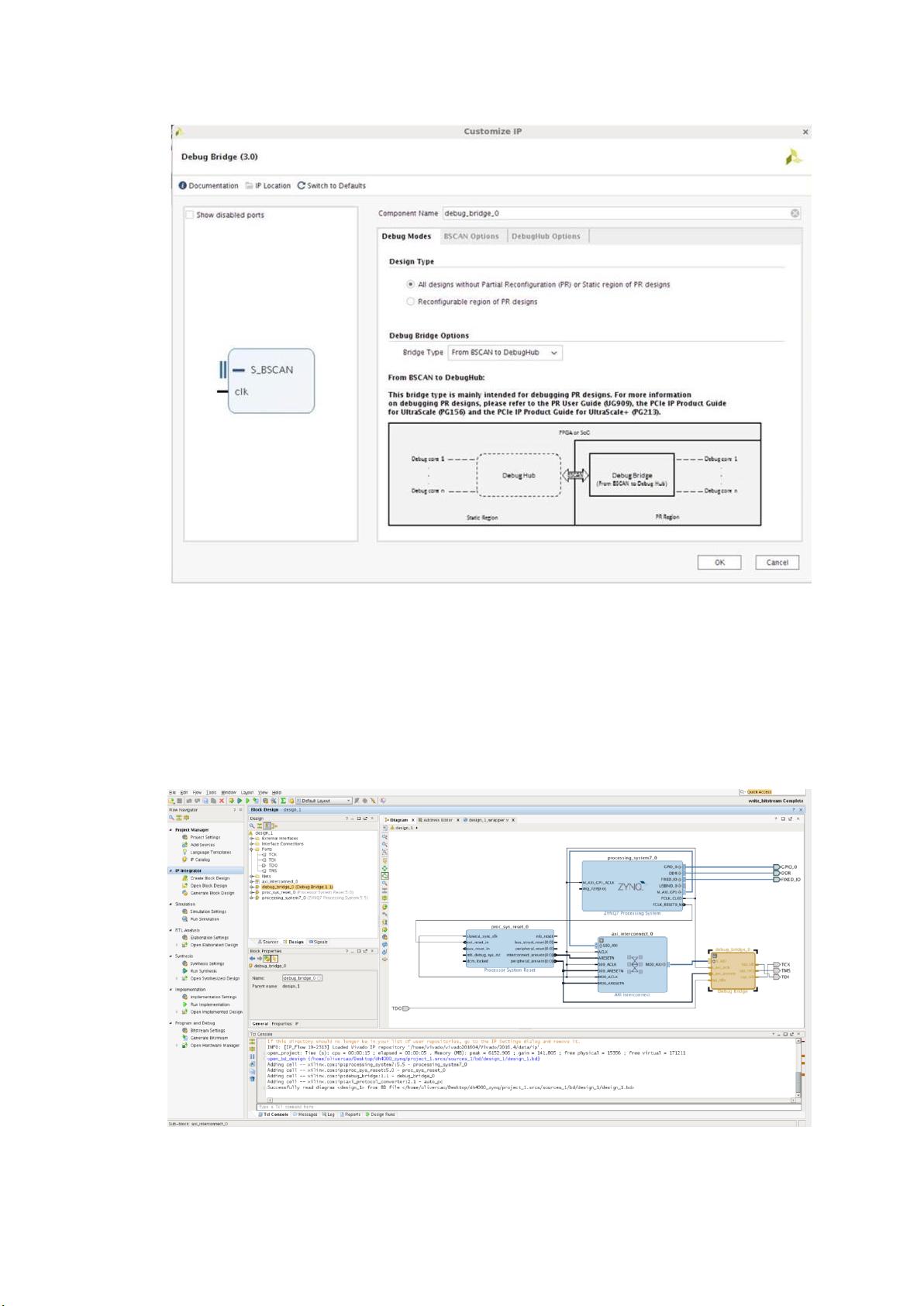

2. 调研方案

Vivado Hardware Server ZYNQ-Debug Bridge FPGAEthernet XVC Protocol JTAG Interface

Vivado Hardware Server 通过 Ethetnet XVC Protocol 来操纵 Debug Bridge 访问 FPGA。

3. Debug Bridge 说明

Xilinx Debug Bridge IP 控制器提供一种为调试核和运行软件之间建立通信通道的机制。Debug

Core 用法可以分为两类: 配合现场更新和 Xilinx Virtual Cable (XVC)。这两类提供了 一种和

Debug IP(包括内存 IP)通信的方式。

现场更新流程允许用户在设备通过串联可编程只读存储器/PCIe 配置后下载新功能到设备中。

XVC 流程允许用户通过非 JTAG 接口使用调试内核调试设计 (例如,以太网/PCIe)。

Debug 功能上分为两大类,支持六种不同的模式:

Tandem with Field Updates and Partial Reconfiguration Solution:支持以下模式:

From_BSCAN_to_Debug:每一个连接了 debug cores 重配置模块添加 Debug Bridge。

XVC Solution:支持以下 5 种模式:

From_AXI_to_BSCAN:在带有 Ethernet/Pcie 作为主设备的设计中添加 Debug Bridge。当在

同一个芯片上带有 Debug Cores 使用该模式。

From_AXI_to_JTAG: 在带有 Ethernet/Pcie 作为主设备的设计中添加 Debug Bridge。该模式

下会引出 JTAG 管脚,用于 Debug 另一个带有 Debug Cores 的芯片。

From_JTAG_to_BSCAN:当通过 TAP(soft Test Acess Port)来 Debug 设计时使用。

From_PCIE_to_BSCAN: 在带有 Pcie 作为主设备的设计中添加 Debug Bridge。Debug 当前

芯片。仅支持 ultra scale 及 ultrascale+系列的芯片。

From_PCIE_to_JTAG: 在带有 Pcie 作为主设备的设计中添加 Debug Bridge。该模式下会引

出 JTAG 管脚,用于 Debug 另一个芯片。仅支持 ultra scale 及 ultrascale+系列的芯片。

IP 配置介绍: