没有合适的资源?快使用搜索试试~ 我知道了~

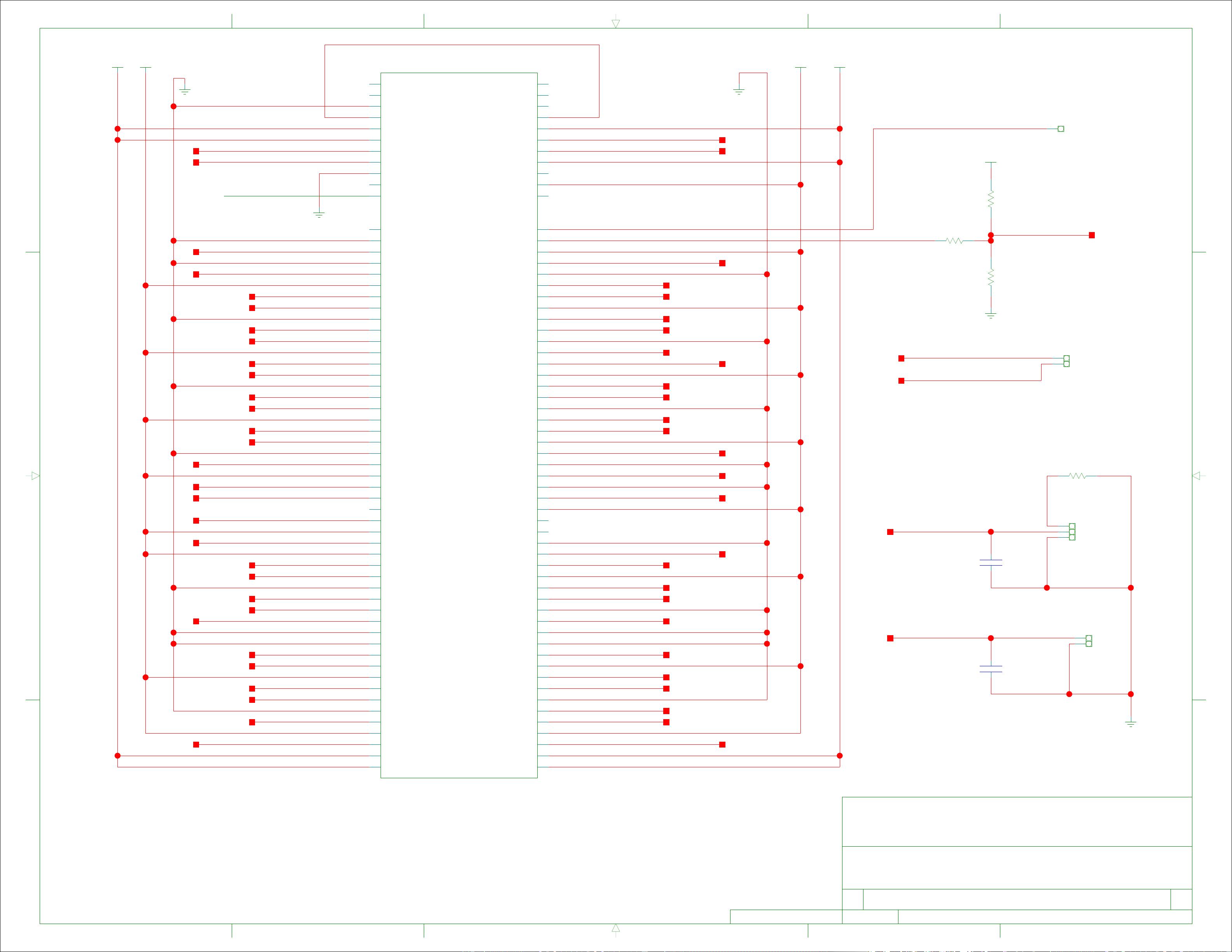

PCIe 原理图

温馨提示

PCIe 原理图

资源推荐

资源详情

资源评论

01

Xilinx

0381219

456 3 2 1

REV

TITLE

SCHEM,ROHS COMPLIANT,ML555

PCIE PCI PCI-X PCB,1280389

SCALE SHEET

SIZE DWG NO

1236 5 4

B

A A

B

C

D

C

D

C

of

DRAWN BY

PCIe CEM Spec, Pg. 56 footnotes:

- By default the PETpx and PETnx pins shall be connected

to the PCI Express transmitter differential pair on the

system board, and the PCI Express receiver pair on the add-in card

- By default the PERpx and PERnx pins shall be connected

system board, and the PCI Express transmitter pair on the add-in card

to the PCI Express receiver differential pair on the

2) PCI Edge Connector P1 is keyed as 3.3V ONLY

ML555 PCB:

Notes:

1) Active Low Signals Names end in B or _B

3) +IOV for PCI edge connector is wired to 3.3V

4) Ref. Sheet 6:

Xilinx PCB Schematic Number: 0381219

Latest Schematics Revision:

ML555 Engineering Rev03 (3rd spin) will be

Production Rev01 for customer Release

Rev01_10-5-06

37

10-5-2006_15:48

1

DAVID NAYLOR

01

Xilinx

0381219

456 3 2 1

REV

TITLE

SCHEM,ROHS COMPLIANT,ML555

PCIE PCI PCI-X PCB,1280389

SCALE SHEET

SIZE DWG NO

1236 5 4

B

A A

B

C

D

C

D

C

of

DRAWN BY

10.J5 SATAConn,MGTX0Y5 SATA I/F,J6-J9SMAConns,U3 Clock Mux

1.ML555 Schematic Sheet Cover Page

2.ML555 Schematic SheetList (this page)

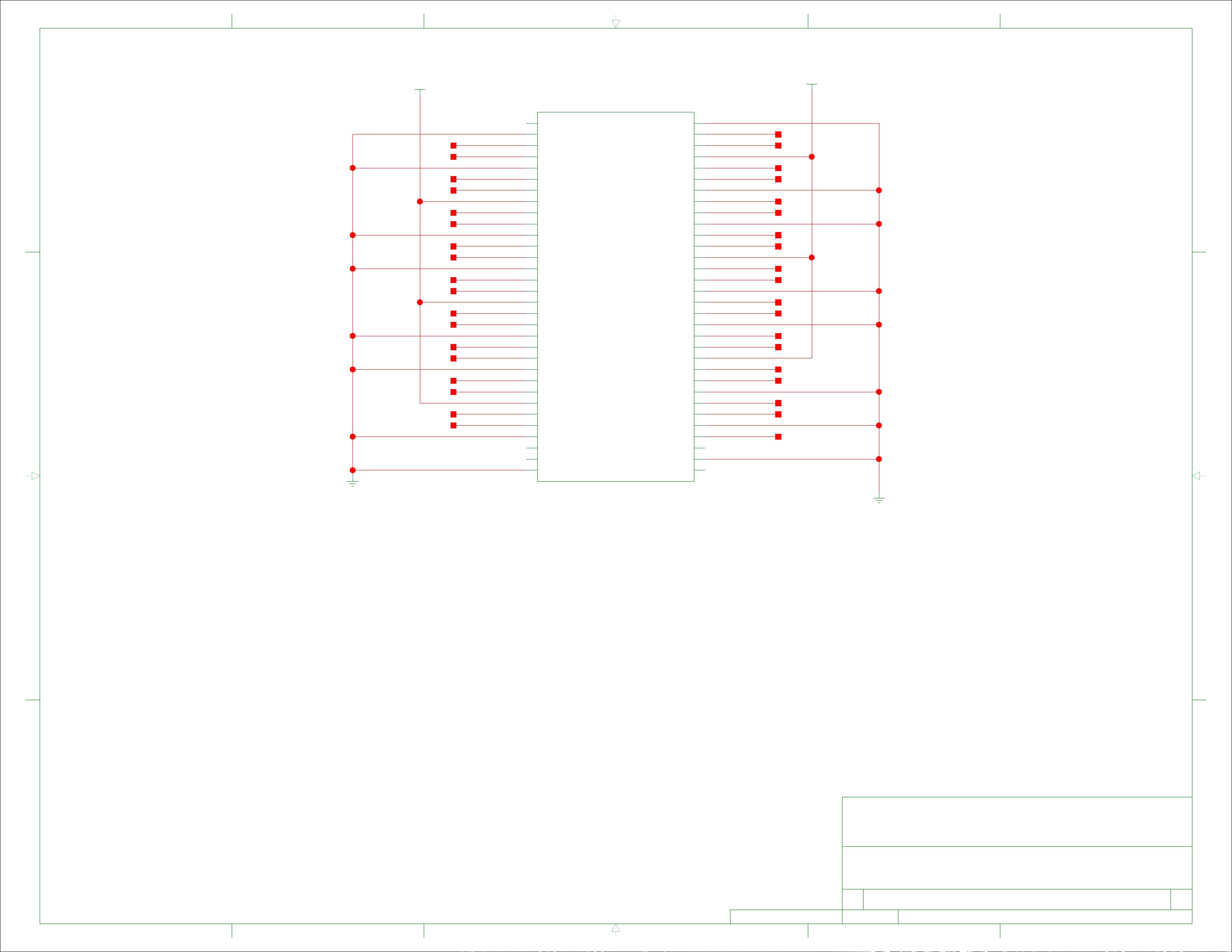

3.P1a PCI/PCI-X 3.3V Edge Connector, 32-bit portion

4.P1b PCI/PCI-X 3.3V Edge Connector, 64-bit extension

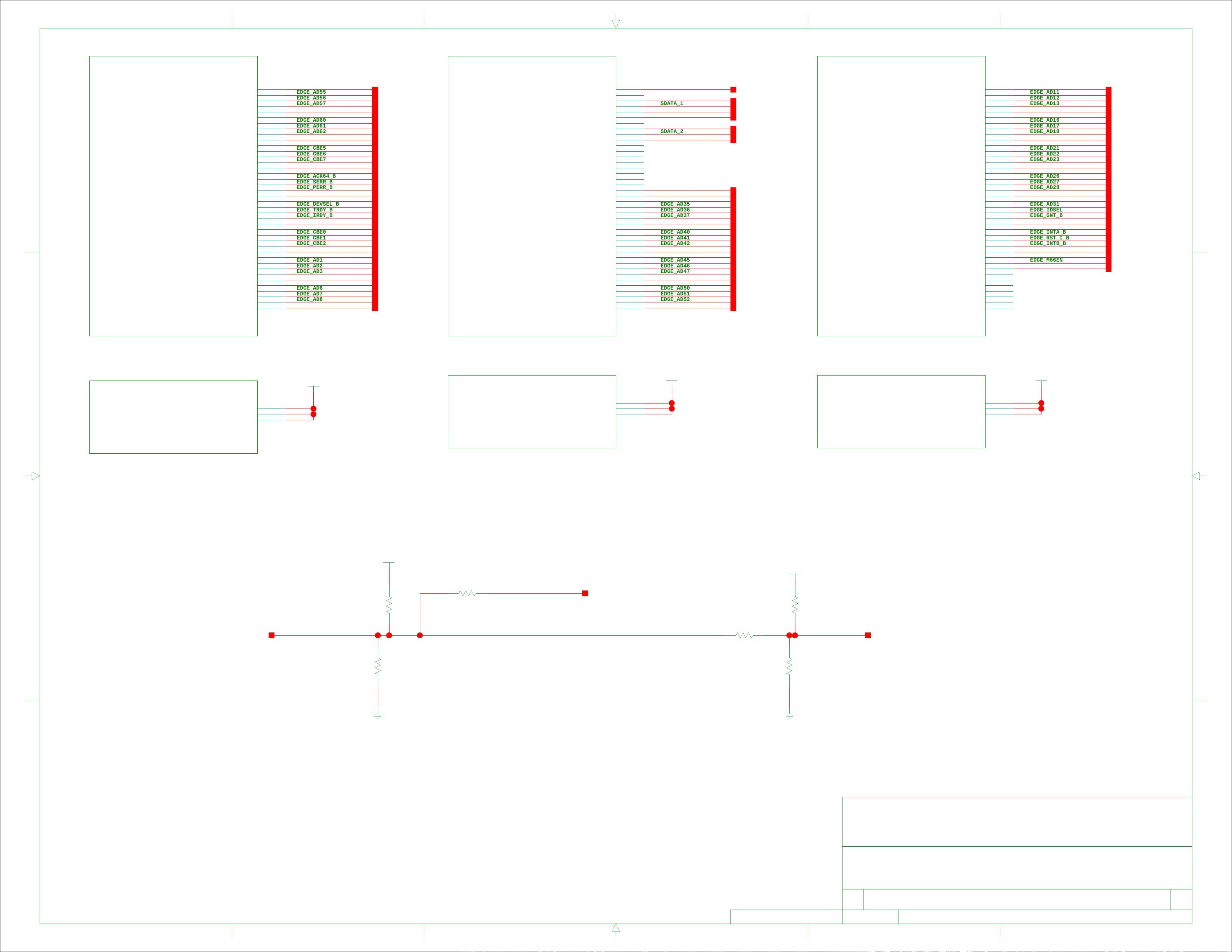

5.PCI/PCI-X P1 FPGA I/F, 3.0V Banks 11, 13, 15

6.PCIe Edge Conn.P13,PCIe I/F MGT's X0Y0,X0Y1,X0Y2,X0Y3

7.MGT X0Y0,X0Y1,X0Y2,X0Y3 Power & Filtering

8.SFP1(J3), SFP2(J4) Optical I/F Connectors

9.MGTX0Y4 SFP1&2 I/F,U2 Clock Mux

11.Y1 Osc. 125MHz LVDS, U11 Clock Mux

13.U6 CPLD, Reset&Prog Push-Buttons

17.J15,J16 2x32 EPHY BERG HEADERS,J1 USB-B Conn, U5 USB I/F

19.J2 200-pin 1.8V DDR2 SODIMM Socket

20.DDR2 Memory Termination Resistors

21.Banks 17 and 21 DDR2 SODIMM Socket I/F

22.Banks 4 and 22 DDR2 SODIMM Socket I/F

23.Bank0 JTAG and Mode I/F

28.Unused XC5VLX110T Banks 5, 6, 23, 25

27.Unused MGT's XC5VLX110T

29.Voltage Regulators VR1,VR2,VR3

30.Voltage Regulators VR4,U12,U13,U14

31.MGT Voltage Regulators VR5, VR6, VR7

32.Decoupling Caps: 12V, 5V, 3.3V

ML555 Schematic Sheet List

36.ML555 Voltage Regulator Topology

37.ML555 Block Diagram

33.Decoupling Caps: 2.5V Vccaux, 2.5V Vcco

26.FPGA Power Connections: VCCINT 1.0V, VCCAUX 2.5V, GND

35.Decoupling Caps: 3.0V PCI, 1.0V Vccint

18.Bank12 BERG EPHY I/F, Bank20 BERG HDR,U6 CPLD I/F

24.U8 Clock Synthesizer 1 - Memory I/F

25.U7 Clock Synthesizer 2 - SATA and SFP I/F

15.Banks 1, 2 PF I/F, GPIO I/F, USB I/F

14.Banks18,19 P32,P33 GPIO Samtec Connectors

34.Decoupling Caps: 1.8V DDR2 Mem, 0.9V DDR2 Term

12.U1 Platform Flash,P5JTAG Conn,Y2 Osc 33MHz CMOS, U2 PCI Clk Buffer

16.Bank3 GCLK I/F, misc. CLK I/F,Y2 Osc. 200MHz LVPECL, J10&J11 Clk.SMA

37

8-30-2006_8:06

2

DAVID NAYLOR

PCI_VCC

D

D

VCC3V3VCC5 VCC5

DD

1

2

1

2

1

2

3

D

01

Xilinx

0381219

456 3 2 1

REV

TITLE

SCHEM,ROHS COMPLIANT,ML555

PCIE PCI PCI-X PCB,1280389

SCALE SHEET

SIZE DWG NO

1236 5 4

B

A A

B

C

D

C

D

C

of

DRAWN BY

GND

GND

+AUXV

PME#

M66EN

AD[21]

GND

KEY

-12V

KEY

+IOV

+12V

TRST#

TMS

TDI

+5V

INTA#

INTC#

+5V

RESERVED

RESERVED

RST#

+IOV

GNT#

GND

AD[30]

+3.3V

AD[28]

AD[26]

GND

AD[24]

IDSEL

+3.3V

AD[22]

AD[20]

GND

AD[18]

AD[16]

+3.3V

FRAME#

GND

TRDY#

GND

STOP#

+3.3V

GND

PAR

AD[15]

+3.3V

AD[13]

AD[11]

GND

AD[09]

C/BE#[0]

+3.3V

AD[06]

AD[04]

GND

AD[02]

AD[00]

+IOV

REQ64#

+5V

+5V

TCK

GND

TDO

+5V

+5V

INTB#

INTD#

PRSNT1#

RESERVED

PRSNT2#

KEY

KEY

RESERVED

GND

CLK

GND

REQ#

+IOV

AD[31]

AD[29]

GND

AD[27]

AD[25]

+3.3V

C/BE#[3]

AD[23]

AD[19]

+3.3V

AD[17]

C/BE#[2]

GND

IRDY#

+3.3V

DEVSEL#

LOCK#

PERR#

+3.3V

SERR#

+3.3V

C/BE#[1]

AD[14]

GND

AD[12]

AD[10]

AD[08]

AD[07]

+3.3V

AD[05]

AD[03]

GND

AD[01]

+IOV

ACK64#

+5V

+5V

PCIXCAP

SMBCLK

SMBDAT

GND

GND

VCC3V3

1

PCI EDGE CONNECTOR 3.3V 32-bit SECTION

REMOVE JUMPER FOR 66Mhz

EDGE_PRSNT1_B

EDGE_PRSNT2_B

to U10 LX50T Bank 5

JUMPER 2-3 = NOT PCI-X capable, PCI Mode Only

JUMPER 1-2 = PCI-X 66MHz capable

NO JUMPER = PCI-X 133MHz capable

P8 JUMPERS:

1

P6

DNA

AUXV_A14

1 2

R240

100R

1 2

R239

100R

1 2

R238

15R

A1

A10

A11

A14

A15

A16

A17

A18

A19

A2

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A3

A30

A31

A32

A33

A34

A35

A36

A37

A38

A39

A4

A40

A41

A42

A43

A44

A45

A46

A47

A48

A49

A5

A52

A53

A54

A55

A56

A57

A58

A59

A6

A60

A61

A62

A7

A8

A9

B1

B10

B11

B14

B15

B16

B17

B18

B19

B2

B20

B21

B22

B23

B24

B25

B26

B27

B28

B29

B3

B30

B31

B32

B33

B34

B35

B36

B37

B38

B39

B4

B40

B41

B42

B43

B44

B45

B46

B47

B48

B49

B5

B52

B53

B54

B55

B56

B57

B58

B59

B6

B60

B61

B62

B7

B8

B9

B50

B51

A50

A51

P1

EDGE_PCI_3V3

37

6-8-2006_19:07

3

DAVID NAYLOR

12

C13

0.01UF

12

C12

0.01UF

1 2

R1

10K

1

2

3

P8

1

2

P9

1

2

P7

EDGE_RST_I_B

EDGE_RST_B

PCIXCAP_PD

EDGE_M66EN

EDGE_PME_B

EDGE_REQ64_BEDGE_ACK64_B

EDGE_SERR_B

EDGE_PERR_B

EDGE_DEVSEL_B

EDGE_IRDY_B

EDGE_STOP_B

EDGE_TRDY_B

EDGE_FRAME_B

EDGE_REQ_B

EDGE_PME_B

EDGE_GNT_B

EDGE_INTC_B

EDGE_INTA_B

EDGE_PCIXCAP

VCC5

VCC5

VCC5

VCC5

VCC5

VCC5

VCC5

VCC5

CLK_FROM_EDGE

EDGE_AD8

EDGE_CBE1

EDGE_PCIXCAP

EDGE_AD19

EDGE_AD12

EDGE_M66EN

EDGE_CBE2

EDGE_CBE3

EDGE_CBE0

EDGE_AD30

EDGE_AD28

EDGE_AD26

EDGE_AD24

EDGE_AD22

EDGE_AD20

EDGE_AD18

EDGE_AD16

EDGE_AD31

EDGE_AD29

EDGE_AD27

EDGE_AD25

EDGE_AD23

EDGE_AD21

EDGE_AD17

EDGE_AD10

EDGE_AD7

EDGE_AD5

EDGE_AD3

EDGE_AD15

EDGE_AD13

EDGE_AD11

EDGE_AD9

EDGE_AD6

EDGE_AD4

EDGE_AD2

EDGE_AD0

EDGE_JTAG

EDGE_AD1

EDGE_IDSEL

EDGE_PAR

EDGE_AD14

EDGE_INTB_B

EDGE_INTD_B

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

FPGA_EDGE_PME_B

VCC3V3

VCC3V3

D

D

+IOV

GND

RESERVED

RESERVED

RESERVED

GND

GND

GND

+IOV

GND

GND

GND

GND

GND

GNDRESERVED

C/BE#[6]

C/BE#[4]

GND

AD[63]

AD[61]

AD[59]

AD[57]

AD[55]

AD[53]

AD[51]

AD[49]

+IOV

AD[45]

GND

C/BE#[7]

C/BE#[5]

+IOV

GND

PAR64

AD[47]

AD[62]

AD[60]

GND

AD[58]

+IOV

AD[56]

AD[54]

AD[52]

AD[50]

AD[48]

AD[46]

AD[44]

AD[43]

AD[41]

AD[39]

AD[37]

AD[35]

AD[33]

GND

RESERVED

AD[32]

AD[34]

AD[36]

GND

AD[38]

AD[40]

+IOV

AD[42]

01

Xilinx

0381219

456 3 2 1

REV

TITLE

SCHEM,ROHS COMPLIANT,ML555

PCIE PCI PCI-X PCB,1280389

SCALE SHEET

SIZE DWG NO

1236 5 4

B

A A

B

C

D

C

D

C

of

DRAWN BY

PCI EDGE CONNECTOR 3.3V 64-bit EXTENSION

37

5-30-2006_18:44

4

DAVID NAYLOR

A63

A64

A65

A66

A67

A68

A69

A70

A71

A72

A73

A74

A75

A76

A77

A78

A79

A80

A81

A82

B63

B64

B65

B66

B67

B68

B69

B70

B71

B72

B73

B74

B75

B76

B77

B78

B79

B80

B81

B82

B83

B84

B85

B86

B87

B88

B89

B90

B91

B92

B93

B94

A83

A84

A85

A86

A87

A88

A89

A90

A91

A92

A93

A94

P1

EDGE_64BIT_EXT

EDGE_AD32

EDGE_AD34

EDGE_AD36

EDGE_AD38

EDGE_AD40

EDGE_AD42

EDGE_AD33

EDGE_AD35

EDGE_AD37

EDGE_AD39

EDGE_AD41

EDGE_AD43

EDGE_AD45

EDGE_AD47

EDGE_AD49

EDGE_AD51

EDGE_AD53

EDGE_AD55

EDGE_AD57

EDGE_AD59

EDGE_AD61

EDGE_AD63

EDGE_CBE4

EDGE_CBE6

EDGE_AD44

EDGE_AD46

EDGE_AD48

EDGE_AD50

EDGE_AD52

EDGE_AD54

EDGE_AD56

EDGE_AD58

EDGE_AD60

EDGE_AD62

EDGE_PAR64

EDGE_CBE5

EDGE_CBE7

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

VCC2V5

DD

PCI_VCC

PCI_VCC

PCI_VCC

01

Xilinx

0381219

456 3 2 1

REV

TITLE

SCHEM,ROHS COMPLIANT,ML555

PCIE PCI PCI-X PCB,1280389

SCALE SHEET

SIZE DWG NO

1236 5 4

B

A A

B

C

D

C

D

C

of

DRAWN BY

IO_L0P_11_B32

IO_L0N_11_A33

IO_L1P_11_B33

IO_L1N_11_C33

IO_L2P_11_C32

IO_L2N_11_D32

IO_L3P_11_C34

IO_L3N_11_D34

IO_L4P_11_G32

IO_L4N_VREF_11_H32

IO_L5P_11_F33

IO_L5N_11_E34

IO_L6P_11_E32

IO_L6N_11_E33

IO_L7P_11_G33

IO_L7N_11_F34

IO_L8P_CC_11_J32

IO_L8N_CC_11_H33

IO_L9P_CC_11_H34

IO_L9N_CC_11_J34

IO_L10P_CC_SM7_11_L34

IO_L10N_CC_SM7_11_K34

IO_L11P_CC_SM6_11_K33

IO_L11N_CC_SM6_11_K32

IO_L12P_VRN_11_N33

IO_L12N_VRP_11_M33

IO_L13P_11_L33

IO_L13N_11_M32

IO_L14P_11_P34

IO_L14N_VREF_11_N34

IO_L15P_SM5_11_P32

IO_L15N_SM5_11_N32

IO_L16P_SM4_11_T33

IO_L16N_SM4_11_R34

IO_L17P_SM3_11_R33

IO_L17N_SM3_11_R32

IO_L18P_SM2_11_U33

IO_L18N_SM2_11_T34

IO_L19P_SM1_11_U32

IO_L19N_SM1_11_U31

FPGA1

5VLX50T

FF1136

VCCO_11_T27

VCCO_11_R30

VCCO_11_V31

FPGA1

IO_L0P_SM16_13_V32

IO_L0N_SM16_13_V33

IO_L1P_SM15_13_W34

IO_L1N_SM15_13_V34

IO_L2P_SM14_13_Y33

IO_L2N_SM14_13_AA33

IO_L3P_SM13_13_AA34

IO_L3N_SM13_13_Y34

IO_L4P_13_Y32

IO_L4N_VREF_13_W32

IO_L5P_SM12_13_AC34

IO_L5N_SM12_13_AD34

IO_L6P_SM11_13_AC32

IO_L6N_SM11_13_AB32

IO_L7P_SM10_13_AC33

IO_L7N_SM10_13_AB33

IO_L8P_CC_SM9_13_AF33

IO_L8N_CC_SM9_13_AE33

IO_L9P_CC_SM8_13_AF34

IO_L9N_CC_SM8_13_AE34

IO_L10P_CC_13_AH34

IO_L10N_CC_13_AJ34

IO_L11P_CC_13_AD32

IO_L11N_CC_13_AE32

IO_L12P_VRN_13_AG33

IO_L12N_VRP_13_AH33

IO_L13P_13_AK34

IO_L13N_13_AK33

IO_L14P_13_AG32

IO_L14N_VREF_13_AH32

IO_L15P_13_AJ32

IO_L15N_13_AK32

IO_L16P_13_AL34

IO_L16N_13_AL33

IO_L17P_13_AM33

IO_L17N_13_AM32

IO_L18P_13_AN34

IO_L18N_13_AN33

IO_L19P_13_AN32

IO_L19N_13_AP32

FPGA1

5VLX50T

FF1136

VCCO_13_W28

VCCO_13_AB29

VCCO_13_AA32

FPGA1

VCCO_15_M29

VCCO_15_L32

VCCO_15_P33

FPGA1

PCI_VCC

IO_L0P_15_E29

IO_L0N_15_F29

IO_L1P_15_G30

IO_L1N_15_F30

IO_L2P_15_H29

IO_L2N_15_J29

IO_L3P_15_F31

IO_L3N_15_E31

IO_L4P_15_L29

IO_L4N_VREF_15_K29

IO_L5P_15_H30

IO_L5N_15_G31

IO_L6P_15_J30

IO_L6N_15_J31

IO_L7P_15_L30

IO_L7N_15_M30

IO_L8P_CC_15_N29

IO_L8N_CC_15_P29

IO_L9P_CC_15_K31

IO_L9N_CC_15_L31

IO_L10P_CC_15_P31

IO_L10N_CC_15_P30

IO_L11P_CC_15_M31

IO_L11N_CC_15_N30

IO_L12P_VRN_15_R28

IO_L12N_VRP_15_R29

IO_L13P_15_T31

IO_L13N_15_R31

IO_L14P_15_U30

IO_L14N_VREF_15_T30

IO_L15P_15_T28

IO_L15N_15_T29

IO_L16P_15_U27

IO_L16N_15_U28

IO_L17P_15_R26

IO_L17N_15_R27

IO_L18P_15_U26

IO_L18N_15_T26

IO_L19P_15_U25

IO_L19N_15_T25

FPGA1

5VLX50T

FF1136

Bank 13

PCI 32-bit I/F

PCI 64-bit EXTENSION I/F

Banks 11,13,15

Bank 11 Bank 15

PCI 32&64 bit EDGE Connector Bank I/F

from PCI EDGE CONN pin P1.B16 on Sheet1

to Bank11 pinL34 on this Sheet

to (Vcco=2.5V) Bank3 pinJ14 on Sheet16

2.5V scaling network

SI network

To Sheet25 U7

To Sheet24 U8

E29

F29

G30

F30

H29

J29

F31

E31

L29

K29

H30

G31

J30

J31

L30

M30

N29

P29

K31

L31

P31

P30

M31

N30

R28

R29

T31

R31

U30

T30

T28

T29

U27

U28

R26

R27

U26

T26

U25

T25

U10

SCLOCK_2

1 2

R30

100R

1 2

R29

100R

1 2

R242

15R

PCIBUSCLK1

1 2

0R

R2

1 2

R4

100R

1 2

R3

100R

SDATA_2

STROBE_2

PLOAD_2

SCLOCK_1

SDATA_1

STROBE_1

PLOAD_1

EDGE_AD32

EDGE_AD33

EDGE_AD34

EDGE_AD35

EDGE_AD36

EDGE_AD37

EDGE_AD38

EDGE_AD39

EDGE_AD40

EDGE_AD41

EDGE_AD42

EDGE_AD43

EDGE_AD44

EDGE_AD45

EDGE_AD46

EDGE_AD47

EDGE_AD48

EDGE_AD49

EDGE_AD50

EDGE_AD51

EDGE_AD52

EDGE_AD53EDGE_AD9

EDGE_AD8

EDGE_AD7

EDGE_AD6

EDGE_AD5

EDGE_AD4

EDGE_AD3

EDGE_AD2

EDGE_AD1

EDGE_AD0

EDGE_CBE3

EDGE_CBE2

EDGE_CBE1

EDGE_CBE0

EDGE_PAR

EDGE_FRAME_B

EDGE_IRDY_B

EDGE_TRDY_B

EDGE_DEVSEL_B

EDGE_STOP_B

PCIBUSCLK1

EDGE_SERR_B

EDGE_PERR_B

EDGE_ACK64_B

EDGE_REQ64_B

EDGE_PAR64

EDGE_CBE7

EDGE_CBE6

EDGE_CBE5

EDGE_CBE4

EDGE_AD63

EDGE_AD62

EDGE_AD61

EDGE_AD60

EDGE_AD59

EDGE_AD58

EDGE_AD57

EDGE_AD56

EDGE_AD55

EDGE_AD54

M29

L32

P33

U10

W28

AB29

AA32

U10

V32

V33

W34

V34

Y33

AA33

AA34

Y34

Y32

W32

AC34

AD34

AC32

AB32

AC33

AB33

AF33

AE33

AF34

AE34

AH34

AJ34

AD32

AE32

AG33

AH33

AK34

AK33

AG32

AH32

AJ32

AK32

AL34

AL33

AM33

AM32

AN34

AN33

AN32

AP32

U10

T27

R30

V31

U10

B32

A33

B33

C33

C32

D32

C34

D34

G32

H32

F33

E34

E32

E33

G33

F34

J32

H33

H34

J34

L34

K34

K33

K32

N33

M33

L33

M32

P34

N34

P32

N32

T33

R34

R33

R32

U33

T34

U32

U31

U10

37

8-30-2006_8:06

5

DAVID NAYLOR

CLK_FROM_EDGE PCIBUSCLK2

EDGE_AD10

EDGE_AD11

EDGE_AD12

EDGE_AD13

EDGE_AD14

EDGE_AD15

EDGE_AD16

EDGE_AD17

EDGE_AD18

EDGE_AD19

EDGE_AD20

EDGE_AD21

EDGE_AD22

EDGE_AD23

EDGE_AD24

EDGE_AD25

EDGE_AD26

EDGE_AD27

EDGE_AD28

EDGE_AD29

EDGE_AD30

EDGE_AD31

EDGE_IDSEL

EDGE_GNT_B

EDGE_REQ_B

FPGA_EDGE_PME_B

EDGE_INTA_B

EDGE_RST_I_B

EDGE_INTB_B

EDGE_INTC_B

EDGE_INTD_B

EDGE_M66EN

EDGE_PCIXCAP

剩余36页未读,继续阅读

资源评论

wflishh2019-04-10参考学习。。。。

wflishh2019-04-10参考学习。。。。

qq_31716645

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 等发达地区的无穷大无穷大无穷大请问

- 微藻检测19-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- NE555+74LS192+74LS48电子秒表课程设计报告(纯数电实现)

- 基于深度学习的视频描述综述:视觉与语言的桥梁

- 2024年全球干式变压器行业规模及市场占有率分析报告

- 用于Unity使用NuGet

- 微藻检测18-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- 小红书2024新年市集合作方案解析与品牌营销策略

- 基于javaweb的沙发销售管理系统论文.doc

- 毕业设计Jupyter Notebook基于深度网络的垃圾识别与分类算法研究项目源代码,用PyTorch框架中的transforms方法对数据进行预处理操作,后经过多次调参实验,对比不同模型分类效果

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功