没有合适的资源?快使用搜索试试~ 我知道了~

资源推荐

资源详情

资源评论

产品特点

• 高性能、低功耗的 AVR

®

8 位微处理器

• 先进的 RISC 结构

– 133 条指令 – 大多数可以在一个时钟周期内完成

– 32 x 8 通用工作寄存器 + 外设控制寄存器

– 全静态工作

– 工作于 16 MHz 时性能高达 16 MIPS

– 只需两个时钟周期的硬件乘法器

• 非易失性的程序和数据存储器

– 128K 字节的系统内可编程 Flash

寿命 : 10,000 次写 / 擦除周期

– 具有独立锁定位、可选择的启动代码区

通过片内的启动程序实现系统内编程

真正的读 - 修改 - 写操作

–4K字节的 EEPROM

寿命 : 100,000 次写 / 擦除周期

–4K 字节的内部 SRAM

– 多达 64K 字节的优化的外部存储器空间

– 可以对锁定位进行编程以实现软件加密

– 可以通过 SPI 实现系统内编程

• JTAG 接口 ( 与 IEEE 1149.1 标准兼容 )

– 遵循 JTAG 标准的边界扫描功能

– 支持扩展的片内调试

– 通过 JTAG 接口实现对 Flash, EEPROM, 熔丝位和锁定位的编程

• 外设特点

– 两个具有独立的预分频器和比较器功能的 8 位定时器 / 计数器

– 两个具有预分频器、比较功能和捕捉功能的 16 位定时器 / 计数器

– 具有独立预分频器的实时时钟计数器

– 两路 8 位 PWM

–6路分辨率可编程 (2 到 16 位)的 PWM

– 输出比较调制器

–8路 10 位 ADC

8 个单端通道

7 个差分通道

2 个具有可编程增益 (1x, 10x, 或 200x)的差分通道

– 面向字节的两线接口

– 两个可编程的串行 USART

– 可工作于主机 / 从机模式的 SPI 串行接口

– 具有独立片内振荡器的可编程看门狗定时器

– 片内模拟比较器

• 特殊的处理器特点

– 上电复位以及可编程的掉电检测

– 片内经过标定的 RC 振荡器

– 片内 / 片外中断源

–6种睡眠模式 : 空闲模式、ADC 噪声抑制模式、省电模式、掉电模式、Standby 模式以及

扩展的 Standby 模式

– 可以通过软件进行选择的时钟频率

– 通过熔丝位可以选择 ATmega103 兼容模式

– 全局上拉禁止功能

• I/O 和封装

–53个可编程 I/O 口线

–64引脚 TQFP 与 64 引脚 MLF 封装

• 工作电压

– 2.7 - 5.5V ATmega128L

– 4.5 - 5.5V ATmega128

• 速度等级

– 0 - 8 MHz ATmega128L

– 0 - 16 MHz ATmega128

8 位

微处理器,具有

128K 字节的系统

内可编程 Flash

ATmega128

ATmega128L

Rev. 2467L–AVR–05/04

2

ATmega128

2467L–AVR–05/04

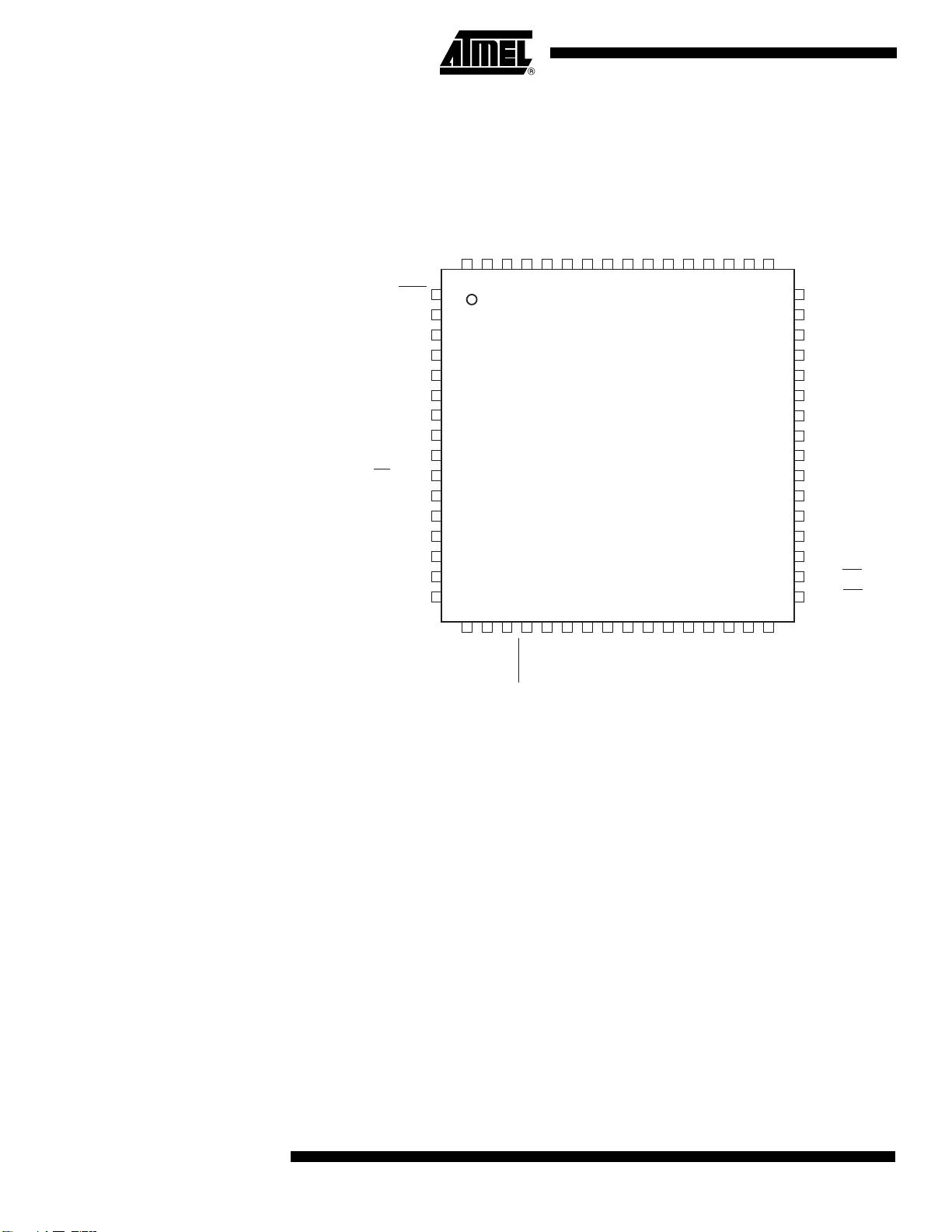

引脚配置 Figure 1. ATmega128 的引脚

综述 ATmega128为基于AVR RISC结构的8位低功耗CMOS微处理器。由于其先进的指令集以

及单周期指令执行时间, ATmega128 的数据吞吐率高达 1MIPS/MHz,从而可以缓减系

统在功耗和处理速度之间的矛盾。

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

PEN

RXD0/(PDI) PE0

(TXD0/PDO) PE1

(XCK0/AIN0) PE2

(OC3A/AIN1) PE3

(OC3B/INT4) PE4

(OC3C/INT5) PE5

(T3/INT6) PE6

(ICP3/INT7) PE7

(SS) PB0

(SCK) PB1

(MOSI) PB2

(MISO) PB3

(OC0) PB4

(OC1A) PB5

(OC1B) PB6

PA3 (AD3)

PA4 (AD4)

PA5 (AD5)

PA6 (AD6)

PA7 (AD7)

PG2(ALE)

PC7 (A15)

PC6 (A14)

PC5 (A13)

PC4 (A12)

PC3 (A11)

PC2 (A10)

PC1 (A9)

PC0 (A8)

PG1(RD)

PG0(WR)

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

(OC2/OC1C) PB7

TOSC2/PG3

TOSC1/1PG4

RESET

VCC

GND

XTAL2

XTAL1

(SCL/INT0) PD0

(SDA/INT1) PD1

(RXD1/INT2) PD2

(TXD1/INT3) PD3

(ICP1) PD4

(XCK1) PD5

(T1) PD6

(T2) PD7

AVCC

GND

AREF

PF0 (ADC0)

PF1 (ADC1)

PF2 (ADC2)

PF3 (ADC3)

PF4 (ADC4/TCK)

PF5 (ADC5/TMS)

PF6 (ADC6/TDO)

PF7 (ADC7/TDI)

GND

VCC

PA0 (AD0)

PA1 (AD1)

PA2 (AD2)

3

ATmega128

2467L–AVR–05/04

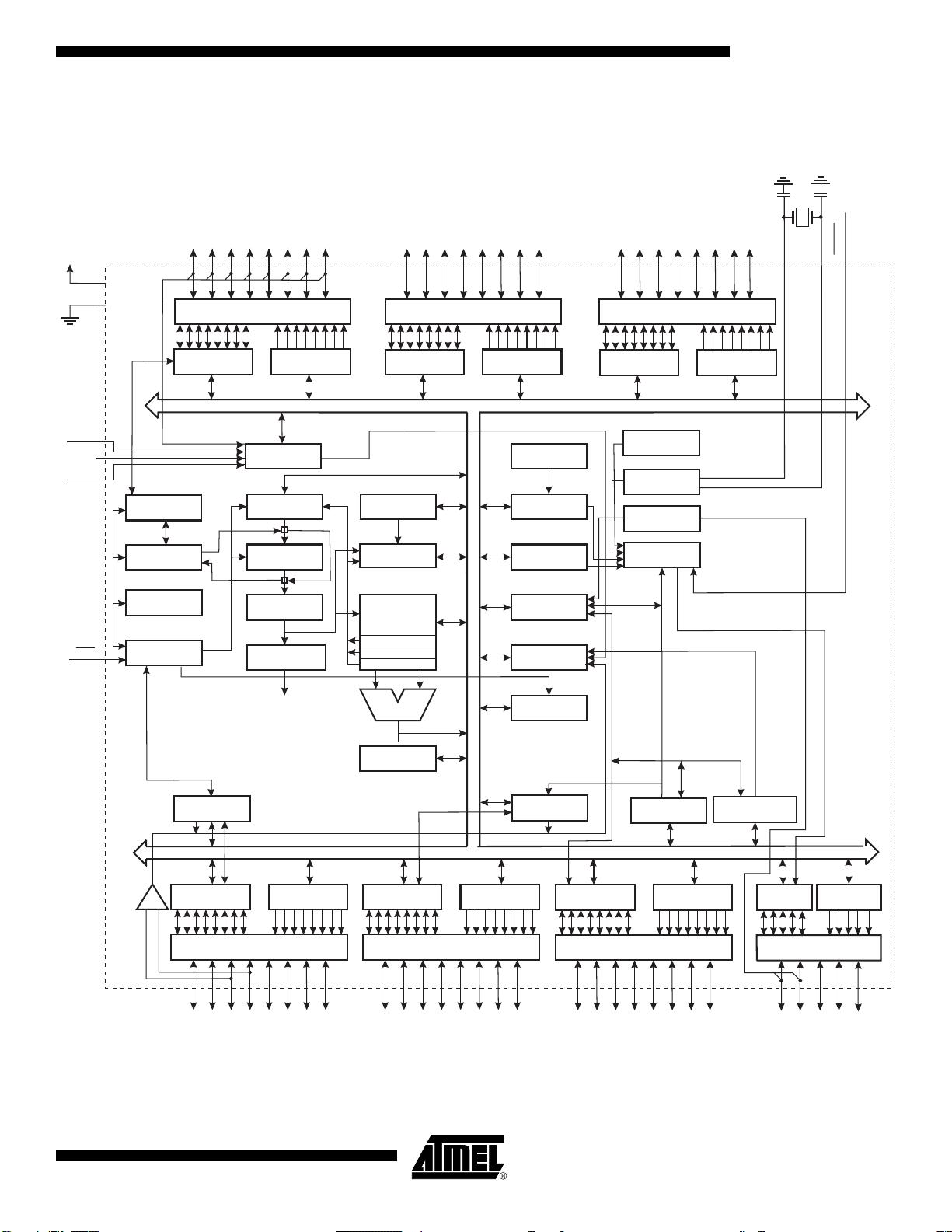

方框图

Figure 2. 方框图

PROGRAM

COUNTER

INTERNAL

OSCILLATOR

WATCHDOG

TIMER

STACK

POINTER

PROGRAM

FLASH

MCU CONTROL

REGISTER

SRAM

GENERAL

PURPOSE

REGISTERS

INSTRUCTION

REGISTER

TIMER/

COUNTERS

INSTRUCTION

DECODER

DATA DIR.

REG. PORTB

DATA DIR.

REG. PORTE

DATA DIR.

REG. PORTA

DATA DIR.

REG. PORTD

DATA REGISTER

PORTB

DATA REGISTER

PORTE

DATA REGISTER

PORTA

DATA REGISTER

PORTD

TIMING AND

CONTROL

OSCILLATOR

OSCILLATOR

INTERRUPT

UNIT

EEPROM

SPI

USART0

STATUS

REGISTER

Z

Y

X

ALU

PORTB DRIVERS

PORTE DRIVERS

PORTA DRIVERS

PORTF DRIVERS

PORTD DRIVERS

PORTC DRIVERS

PB0 - PB7PE0 - PE7

PA0 - PA7PF0 - PF7

RESET

VCC

AGND

GND

AREF

XTAL1

XTAL2

CONTROL

LINES

+

-

ANALOG

COMPARATOR

PC0 - PC7

8-BIT DATA BUS

AVCC

USART1

CALIB. OSC

DATA DIR.

REG. PORTC

DATA REGISTER

PORTC

ON-CHIP DEBUG

JTAG TAP

PROGRAMMING

LOGIC

PEN

BOUNDARY-

SCAN

DATA DIR.

REG. PORTF

DATA REGISTER

PORTF

ADC

PD0 - PD7

DATA DIR.

REG. PORTG

DATA REG.

PORTG

PORTG DRIVERS

PG0 - PG4

TWO-WIRE SERIAL

INTERFACE

4

ATmega128

2467L–AVR–05/04

AVR 内核具有丰富的指令集和 32 个通用工作寄存器。所有的寄存器都直接与算逻单元

(ALU) 相连接,使得一条指令可以在一个时钟周期内同时访问两个独立的寄存器。这种结

构大大提高了代码效率,并且具有比普通的复杂指令集微处理器高 10 倍的数据吞吐率。

ATmega128 具有如下特点:128K 字节的系统内可编程 Flash( 具有在写的过程中还可以读

的能力,即 RWW)、4K 字节的 EEPROM、 4K 字节的 SRAM、 53 个通用 I/O 口线、 32

个通用工作寄存器、实时时钟 RTC、4 个灵活的具有比较模式和 PWM 功能的定时器 / 计

数器 (T/C)、两个 USART、面向字节的两线接口 TWI、 8 通道 10 位 ADC( 具有可选的可

编程增益 )、具有片内振荡器的可编程看门狗定时器、 SPI 串行端口、与 IEEE 1149.1 规

范兼容的 JTAG 测试接口 ( 此接口同时还可以用于片上调试 ),以及六种可以通过软件选

择的省电模式。空闲模式时 CPU 停止工作,而 SRAM、 T/C、 SPI 端口以及中断系统继

续工作;掉电模式时晶体振荡器停止振荡,所有功能除了中断和硬件复位之外都停止工

作,寄存器的内容则一直保持;省电模式时异步定时器继续运行,以允许用户维持时间基

准,器件的其他部分则处于睡眠状态; ADC 噪声抑制模式时 CPU 和所有的 I/O 模块停止

运行,而异步定时器和 ADC 继续工作,以减少 ADC 转换时的开关噪声; Standby 模式

时振荡器工作而其他部分睡眠,使得器件只消耗极少的电流,同时具有快速启动能力;扩

展 Standby 模式则允许振荡器和异步定时器继续工作。

器件是以 Atmel 的高密度非易失性内存技术生产的。片内 ISP Flash 可以通过 SPI 接口、

通用编程器,或引导程序多次编程。引导程序可以使用任何接口来下载应用程序到应用

Flash存储器。在更新应用Flash存储器时引导Flash区的程序继续运行,实现RWW操作。

通过将 8 位 RISC CPU 与系统内可编程的 Flash 集成在一个芯片内, ATmega128 为许

多嵌入式控制应用提供了灵活而低成本的方案。

ATmega128 AVR 有整套的开发工具,包括 C 编译器,宏汇编,程序调试器 / 仿真器和评估

板。

ATmega103 与

ATmega128 的兼容性

ATmega128 是一个很复杂的微处理器,其 I/O 数目为 AVR 指令集所保留的 64 个 I/O 的超

集。为了保持对 ATmega103 的兼容性, ATmega103 的 I/O 位置在 ATmega128 得到了

保留。多数添加的 I/O 位于扩展的 I/O 空间 $60 到 $FF ( 即位于 ATmega103 的内部 RAM

空间 )。这些地址可以通过指令 LD/LDS/LDD 和 ST/STS/STD 来访问,而不是 IN/OUT 指

令。对于 ATmega103 用户而言,内部 RAM 可能还是个问题。此外,由于中断向量的增

加,若程序使用了绝对地址可能也是个问题。为了解决这些问题,ATmega128 设置了一

个熔丝位 M103C。此熔丝位编程后就可以使 ATmega128 工作于 ATmega103 兼容模式。

此时扩展 I/O 空间将无法使用,而内部 RAM 正好与 ATmega103 的一致。同时扩展的中

断向量也被取消了。

ATmega128百分之百与 ATmega103 引脚兼容,可以在PCB 上取代 ATmega103。应用手

册 “Replacing ATmega103 by ATmega128” 详细告诉用户在用 ATmega128 取代

ATmega103 时需要注意的地方。

ATmega103 兼容模式 通过编程熔丝位 M103C,从 RAM、 I/O 引脚和中断向量的角度 ATmega128 将与

ATmega103 相兼容。但是, ATmega128 的一些新特点也就无法使用了。如下所示:

• 只剩下一个 USART,而且只支持异步模式。波特率寄存器只有低 8 位可用。

• 只有一个16位的定时器/计数器,两个比较寄存器,而不是两个16位定时器/计数器,

三个比较寄存器。

• 不支持两线接口。

• 端口 C 只能输出。

• 端口 G 只能用做第二功能,而不能作为通用 I/O 端口。

• 端口 F 只能作为输入,而不能作为 ADC 的模拟输入引脚。

• 不支持引导程序功能。

• 不能够调节片内 RC 振荡器的频率。

5

ATmega128

2467L–AVR–05/04

• 外部存储器接口无法释放任何一个地址引脚作为通用 I/O,也不能够为不同的外部存

储器地址区配置不同的等待周期。

下面的内容则使 ATmega128 更兼容 ATmega103:

• 在 MCUCSR 里只有 EXTRF 和 PORF。

• 改变看门狗溢出时间没有时序要求。

• 外部中断引脚 3 - 0 只能作为电平中断。

•USART没有 FIFO 缓冲器。

在写操作中, ATmega103 没有使用的 I/O 应该写 0。

引脚说明

VCC 数字电路的电源。

GND 地。

端口 A(PA7..PA0) 端口 A 为 8 位双向 I/O 口,并具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动

特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电

路拉低时将输出电流。复位发生时端口 A 为三态。

端口 A 也可以用做其他不同的特殊功能,请参见 P 68。

端口 B(PB7..PB0) 端口 B 为 8 位双向 I/O 口,并具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动

特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电

路拉低时将输出电流。复位发生时端口 B 为三态。

端口 B 也可以用做其他不同的特殊功能,请参见 P 69。

端口 C(PC7..PC0) 端口 C 为 8 位双向 I/O 口,并具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动

特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电

路拉低时将输出电流。复位发生时端口 C 为三态。

端口 C 也可以用做其他不同的特殊功能,请参见 P 72。在 ATmega103 兼容模式下,端

口 C 只能作为输出,而且在复位发生时不是三态。

端口 D(PD7..PD0) 端口 D 为 8 位双向 I/O 口,并具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动

特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电

路拉低时将输出电流。复位发生时端口 D 为三态。

端口 D 也可以用做其他不同的特殊功能,请参见 P 73。

端口 E(PE7..PE0) 端口 E 为 8 位双向 I/O 口,并具有可编程的内部上拉电阻。其输出缓冲器具有对称的驱动

特性,可以输出和吸收大电流。作为输入使用时,若内部上拉电阻使能,则端口被外部电

路拉低时将输出电流。复位发生时端口 E 为三态。

端口 E 也可以用做其他不同的特殊功能,请参见 P 75。

端口 F(PF7..PF0) 端口 F 为 ADC 的模拟输入引脚。

如果不作为 ADC 的模拟输入,端口 F 可以作为 8 位双向 I/O 口,并具有可编程的内部上

拉电阻。其输出缓冲器具有对称的驱动特性,可以输出和吸收大电流。作为输入使用时,

若内部上拉电阻使能,则端口被外部电路拉低时将输出电流。复位发生时端口 F 为三态。

如果使能了 JTAG 接口,则复位发生时引脚 PF7(TDI)、 PF5(TMS) 和 PF4(TCK) 的上拉

电阻使能。

端口 F 也可以作为 JTAG 接口。

剩余359页未读,继续阅读

资源评论

qq_30784429

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 12Cr1MoV钢主蒸汽管道焊接工艺.pdf

- 12Cr1MoV小径管焊接操作工艺 - .pdf

- 12Cr1MoV异种钢焊接温度场的数值模拟.pdf

- 12Cr2Mo1R珠光体耐热钢的焊接 - .pdf

- 13MnNiMoNbR复合银板焊接裂纹的修复.pdf

- 12MnNiVR钢板焊接裂纹敏感性的试验研究.pdf

- 12MnNiVR钢热处理性能及大热输入焊接韧性.pdf

- 13MnNiMoNbR钢焊接工艺研究.pdf

- 13MnNiMoNbR压力容器高强钢焊接工艺研究.pdf

- 14Cr1MoR新钢种的焊接试验研究.pdf

- 14Cr1MoR-I-0Cr18Ni10Ti复合钢板的焊接 - .pdf

- 13焊接空心球节点的承载能力分析.pdf

- 14CrMoR耐热钢压力容器的埋弧焊焊接工艺应用 - .pdf

- 14CrlMoR+0Crl8Nil0Ti复合钢板焊接.pdf

- 14YTJ108 复合保温钢筋焊接网架混凝土墙(CL建筑体系)构造.pdf

- 15×104_m3双盘浮顶油罐底板焊接工艺.pdf

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功