没有合适的资源?快使用搜索试试~ 我知道了~

lpc177x_8x.pdf LPC177x和LPC178X系列数据手册

需积分: 10 2 下载量 90 浏览量

2020-01-17

10:22:52

上传

评论

收藏 800KB PDF 举报

温馨提示

lpc177x_8x.pdf LPC177x和LPC178X系列数据手册 英文版的 32-bit ARM Cortex-M3 microcontroller; up to 512 kB flash and 96 kB SRAM; USB Device/Host/OTG; Ethernet; LCD; EMC

资源推荐

资源详情

资源评论

DR

AFT

DR

AFT

DRAFT

DR

D

RAFT

DRAFT

DRA

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

D

RAFT DRA

F

T DRAFT DRAFT DRAFT DRA

1. General description

The LPC178x/7x is an ARM Cortex-M3 based microcontroller for embedded applications

requiring a high level of integration and low power dissipation.

The Cortex-M3 is a next generation core that offers better performance than the ARM7 at

the same clock rate and other system enhancements such as modernized debug features

and a higher level of support block integration. The Cortex-M3 CPU incorporates a

3-stage pipeline and has a Harvard architecture with separate local instruction and data

buses, as well as a third bus with slightly lower performance for peripherals. The

Cortex-M3 CPU also includes an internal prefetch unit that supports speculative

branches.

The LPC178x/7x adds a specialized flash memory accelerator to accomplish optimal

performance when executing code from flash. The LPC178x/7x is targeted to operate at

up to 100 MHz CPU frequency.

The peripheral complement of the LPC178x/7x includes up to 512 kB of flash program

memory, up to 96 kB of SRAM data memory, up to 4 kB of EEPROM data memory,

External Memory controller (EMC), LCD (LPC178x only), Ethernet, USB

Device/Host/OTG, a General Purpose DMA controller, five UARTs, three SSP controllers,

three I

2

C-bus interfaces, one eight-channel, 12-bit ADC, a 10-bit DAC, a Quadrature

Encoder Interface, four general purpose timers, two general purpose PWMs with six

outputs each, an ultra-low power RTC with separate battery supply, a windowed watchdog

timer, a CRC calculation engine, up to 165 general purpose I/O pins, and more. The

pinout of LPC178x/7x is intended to allow pin function compatibility with the LPC24xx and

LPC23xx.

2. Features and benefits

Functional replacement for LPC23xx and 24xx family devices.

System:

ARM Cortex-M3 processor, running at frequencies of up to 100 MHz. A Memory

Protection Unit (MPU) supporting eight regions is included.

ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

Multilayer AHB matrix interconnect provides a separate bus for each AHB master.

AHB masters include the CPU, and General Purpose DMA controller. This

interconnect provides communication with no arbitration delays unless two masters

attempt to access the same slave at the same time.

Split APB bus allows for higher throughput with fewer stalls between the CPU and

DMA. A single level of write buffering allows the CPU to continue without waiting for

completion of APB writes if the APB was not already busy.

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller; up to 512 kB flash and

96 kB SRAM; USB Device/Host/OTG; Ethernet; LCD; EMC

Rev. 00.08 — 1 March 2011 Objective data sheet

DR

AFT

DR

AFT

DRAFT

DR

D

RAFT

DRAFT

DRA

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

D

RAFT DRA

F

T DRAFT DRAFT DRAFT DRA

LPC178x_7x All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Objective data sheet Rev. 00.08 — 1 March 2011 2 of 112

NXP Semiconductors

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller

Cortex-M3 system tick timer, including an external clock input option.

Standard JTAG test/debug interface as well as Serial Wire Debug and Serial

WireTrace Port options.

Emulation trace module supports real-time trace.

Boundary scan for simplified board testing.

Non-maskable Interrupt (NMI) input.

Memory:

512 kB on-chip flash program memory with In-System Programming (ISP) and

In-Application Programming (IAP) capabilities. The combination of an enhanced

flash memory accelerator and location of the flash memory on the CPU local

code/data bus provides high code performance from flash.

96 kB on-chip SRAM includes:

64 kB of SRAM on the CPU with local code/data bus for high-performance CPU

access.

Two 16 kB SRAM blocks with separate access paths for higher throughput. These

SRAM blocks may be used for DMA memory as well as for general purpose

instruction and data storage.

4 kB on-chip EEPROM.

LCD controller, supporting both Super-Twisted Nematic (STN) and Thin-Film

Transistors (TFT) displays.

Dedicated DMA controller.

Selectable display resolution (up to 1024 × 768 pixels).

Supports up to 24-bit true-color mode.

External Memory Controller (EMC) provides support for asynchronous static memory

devices such as RAM, ROM and flash, as well as dynamic memories such as single

data rate SDRAM.

Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer

matrix that can be used with the SSP, I2S, UART, CRC engine, Analog-to-Digital and

Digital-to-Analog converter peripherals, timer match signals, GPIO, and for

memory-to-memory transfers.

Serial interfaces:

Ethernet MAC with MII/RMII interface and associated DMA controller. These

functions reside on an independent AHB.

USB 2.0 full-speed dual port device/host/OTG controller with on-chip PHY and

associated DMA controller.

Five UARTs with fractional baud rate generation, internal FIFO, DMA support, and

RS-485/EIA-485 support. One UART (UART1) has full modem control I/O, and one

UART (UART4) supports IrDA, synchronous mode, and a smart card mode

conforming to ISO7816-3.

Three SSP controllers with FIFO and multi-protocol capabilities. The SSP

interfaces can be used with the GPDMA controller.

Three enhanced I2C-bus interfaces, one with a true open-drain output supporting

the full I2C-bus specification and Fast-mode Plus with data rates of 1 Mbit/s, two

with standard port pins. Enhancements include multiple address recognition and

monitor mode.

I

2

S (Inter-IC Sound) interface for digital audio input or output. It can be used with

the GPDMA.

DR

AFT

DR

AFT

DRAFT

DR

D

RAFT

DRAFT

DRA

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

D

RAFT DRA

F

T DRAFT DRAFT DRAFT DRA

LPC178x_7x All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Objective data sheet Rev. 00.08 — 1 March 2011 3 of 112

NXP Semiconductors

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller

CAN controller with two channels.

Digital peripherals:

SD/MMC memory card interface.

Up to 165 General Purpose I/O (GPIO) pins depending on the packaging, with

configurable pull-up/down resistors, open-drain mode, and repeater mode. All

GPIOs are located on an AHB bus for fast access and support Cortex-M3

bit-banding. GPIOs can be accessed by the General Purpose DMA Controller. Any

pin of ports 0 and 2 can be used to generate an interrupt.

Two external interrupt inputs configurable as edge/level sensitive. All pins on

PORT0 and PORT2 can be used as edge sensitive interrupt sources.

Four general purpose timers/counters, with a total of eight capture inputs and ten

compare outputs. Each timer block has an external count input. Specific timer

events can be selected to generate DMA requests.

Quadrature encoder interface that can monitor one external quadrature encoder.

Two standard PWM/timer blocks with external count input option.

Real-Time Clock (RTC) with a separate power domain. The RTC is clocked by a

dedicated RTC oscillator. The RTC block includes 20 bytes of battery-powered

backup registers, allowing system status to be stored when the rest of the chip is

powered off. Battery power can be supplied from a standard 3 V Lithium button cell.

The RTC will continue working when the battery voltage drops to as low as 2.1 V.

An RTC interrupt can wake up the CPU from any reduced power mode.

Windowed Watchdog Timer (WWDT). Windowed operation, dedicated internal

oscillator, watchdog warning interrupt, and safety features.

CRC Engine block can calculate a CRC on supplied data using one of three

standard polynomials. The CRC engine can be used in conjunction with the DMA

controller to generate a CRC without CPU involvement in the data transfer.

Analog peripherals:

12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins,

conversion rates up to 400 kHz, and multiple result registers. The 12-bit ADC can

be used with the GPDMA controller.

10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA

support.

Power control:

Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep

power-down.

The Wake-up Interrupt Controller (WIC) allows the CPU to automatically wake up

from any priority interrupt that can occur while the clocks are stopped in

Deep-sleep, Power-down, and Deep power-down modes.

Processor wake-up from Power-down mode via any interrupt able to operate

during Power-down mode (includes external interrupts, RTC interrupt, PORT0/2

pin interrupt, and NMI).

Brownout detect with separate threshold for interrupt and forced reset.

On-chip Power-On Reset (POR).

Clock generation:

Clock output function that can reflect the main oscillator clock, IRC clock, RTC

clock, CPU clock, USB clock, or the watchdog timer clock.

On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

DR

AFT

DR

AFT

DRAFT

DR

D

RAFT

DRAFT

DRA

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

D

RAFT DRA

F

T DRAFT DRAFT DRAFT DRA

LPC178x_7x All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Objective data sheet Rev. 00.08 — 1 March 2011 4 of 112

NXP Semiconductors

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller

12 MHz Internal RC oscillator (IRC) trimmed to 1% accuracy that can optionally be

used as a system clock.

An on-chip PLL allows CPU operation up to the maximum CPU rate without the

need for a high-frequency crystal. May be run from the main oscillator or the

internal RC oscillator.

A second, dedicated PLL may be used for USB interface in order to allow added

flexibility for the Main PLL settings.

Versatile pin function selection feature allows many possibilities for using on-chip

peripheral functions.

Unique device serial number for identification purposes.

Single 3.3 V power supply (2.4 V to 3.6 V). Temperature range of −40 °C to 85 °C.

Available as LQFP208, TFBGA208, TFBGA180, and LQFP144 package.

3. Applications

<tbd>

DR

AFT

DR

AFT

DRAFT

DR

D

RAFT

DRAFT

DRA

F

T DRAF

D

RAFT DRAFT DRAFT DRAFT DRAFT D

DRAFT

D

RAFT DRA

F

T DRAFT DRAFT DRAFT DRA

LPC178x_7x All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Objective data sheet Rev. 00.08 — 1 March 2011 5 of 112

NXP Semiconductors

LPC178x/7x

32-bit ARM Cortex-M3 microcontroller

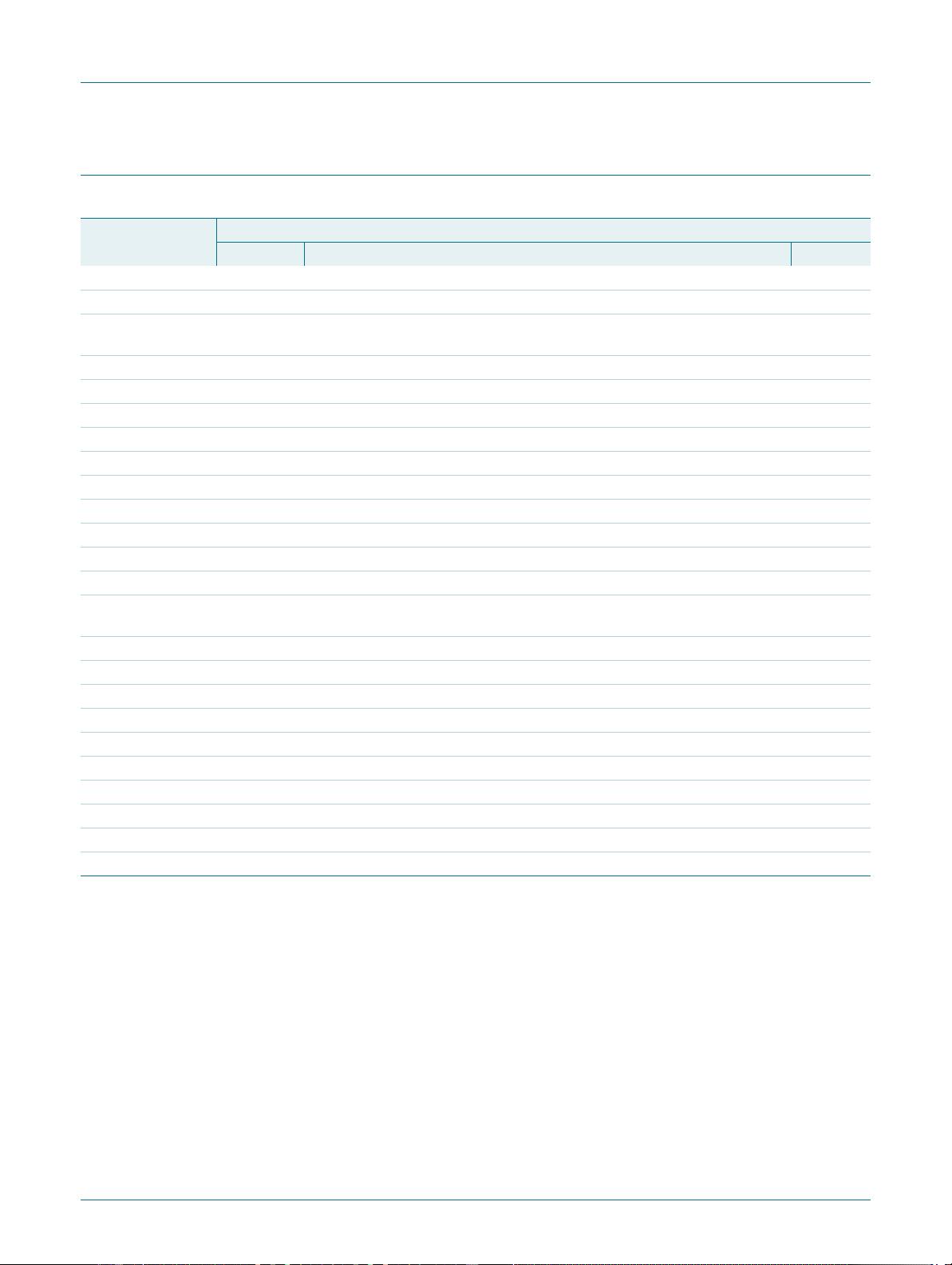

4. Ordering information

Table 1. Ordering information

Type number Package

Name Description Version

LPC1788

LPC1788FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1788FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body

15 × 15 × 0.7 mm

SOT950-1

LPC1788FET180 TFBGA180 thin fine-pitch ball grid array package; 180 balls; body 12 × 12 × 0.8 mm SOT570-2

LPC1788FBD144 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC1787

LPC1787FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1786

LPC1786FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1785

LPC1785FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1778

LPC1778FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1778FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body

15 × 15 × 0.7 mm

SOT950-1

LPC1778FET180 TFBGA180 thin fine-pitch ball grid array package; 180 balls; body 12 × 12 × 0.8 mm SOT570-2

LPC1778FBD144 LQFP144 plastic low profile quad flat package; 144 leads; body 20 × 20 × 1.4 mm SOT486-1

LPC1777

LPC1777FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1776

LPC1776FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1776FET180 TFBGA180 thin fine-pitch ball grid array package; 180 balls; body 12 × 12 × 0.8 mm SOT570-2

LPC1774

LPC1774FBD208 LQFP208 plastic low profile quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC1774FBD144 LQFP144 plastic low profile quad flat package; 144 leads; body 20

× 20 × 1.4 mm

SOT486-1

剩余111页未读,继续阅读

资源评论

PerseverancePrevails

- 粉丝: 19

- 资源: 30

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功