没有合适的资源?快使用搜索试试~ 我知道了~

Systemverilog+UVM搭建SOC

温馨提示

svUVM搭建利用Systemverilog+UVM搭建SOC及ASIC的RTL验证环境

资源推荐

资源详情

资源评论

1

基于

SV+UVM

SV+UVM

SV+UVM

SV+UVM

搭建

SOC/ASIC

SOC/ASIC

SOC/ASIC

SOC/ASIC

验证平台

UVM-1.1 中提供了一个 UBUS 的例子,但是该例子对于刚刚入门的人来说还是需要一定时

间去消化的,本文对该例子进行一步一步的简化,可以帮助理解。

[1-

[1-

[1-

[1- 1

1

1

1 ]

]

]

] 如何顺序的写 UVM

UVM

UVM

UVM 平台( 1

1

1

1 ) -Basic

-Basic

-Basic

-Basic

1. 平台可以在前期规划好 , 但是对于搭建平台的人来说 , 调试永远是最大的问题 , 如果都

将一个个 component 都写完了 , 调试起来还是有点痛苦的 , 所以我更倾向于一步一步的

调试平台;先写一个可以 pass 的基本平台,然后在不断的扩展该平台,最后在各 个

component 中加入所需要的 function 或者 task 。当然,当对搭建平台数量以后,现在基

本对平台中的 component 一次性搭建完成 , 然后调试并添加需要的 function 或者 task 即

可。

2. 最简单的 UVM 平台,一个 interface ,一个 DUT ,一个 TOP ,一个 test ,一个 ENV 就

可以工作了,然后慢慢的添加各个 component ;

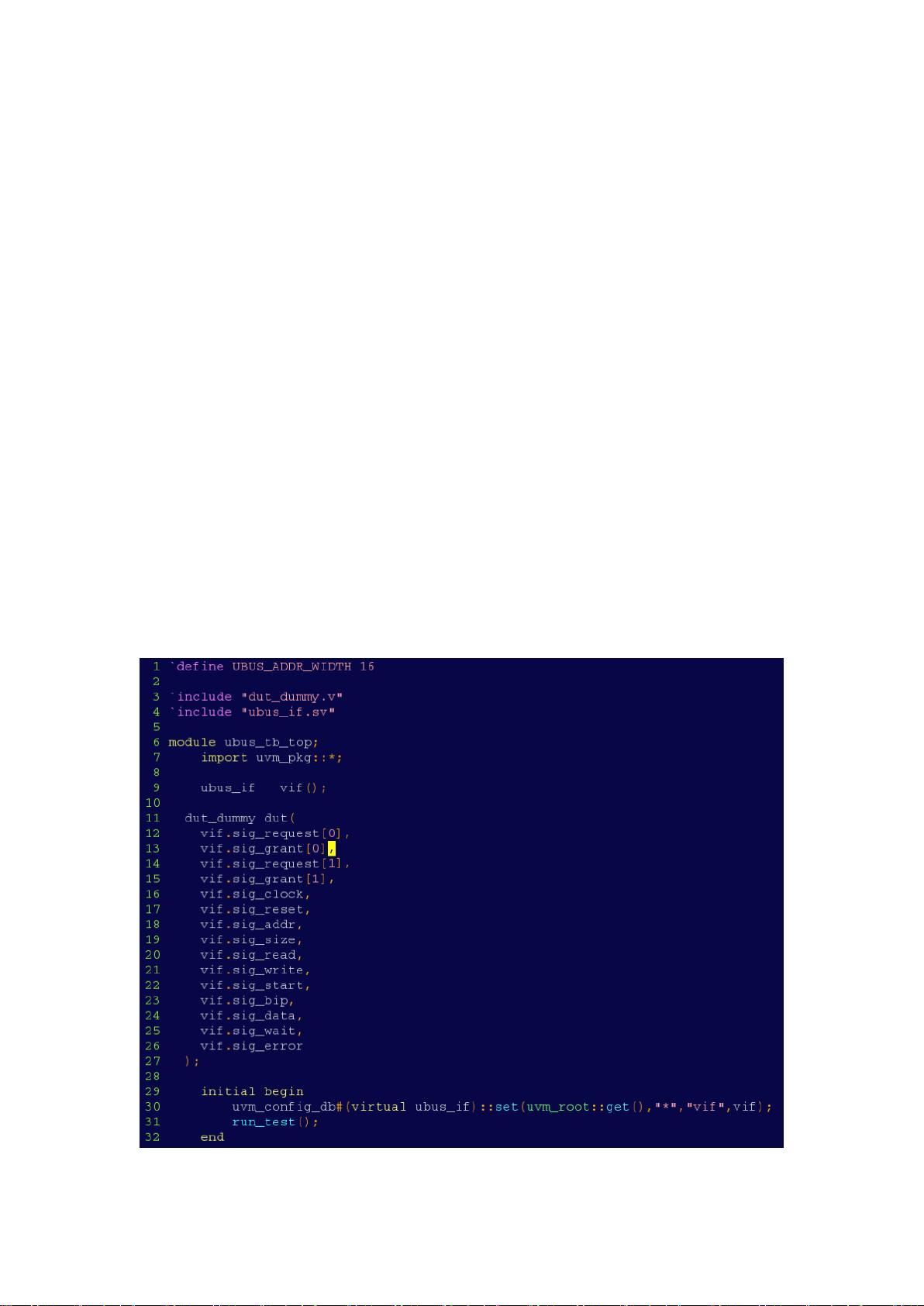

3. 写 interface

4. 写 top module ,在 top 中例化 DUT , interface 和 DUT 在 top 中 include

uvm_config_db#(virtual

uvm_config_db#(virtual

uvm_config_db#(virtual

uvm_config_db#(virtual ubus_if)::set(uvm_root::get(),

ubus_if)::set(uvm_root::get(),

ubus_if)::set(uvm_root::get(),

ubus_if)::set(uvm_root::get(), "*",

"*",

"*",

"*", "vif",

"vif",

"vif",

"vif", vif);

vif);

vif);

vif);

2

run_test();

run_test();

run_test();

run_test();

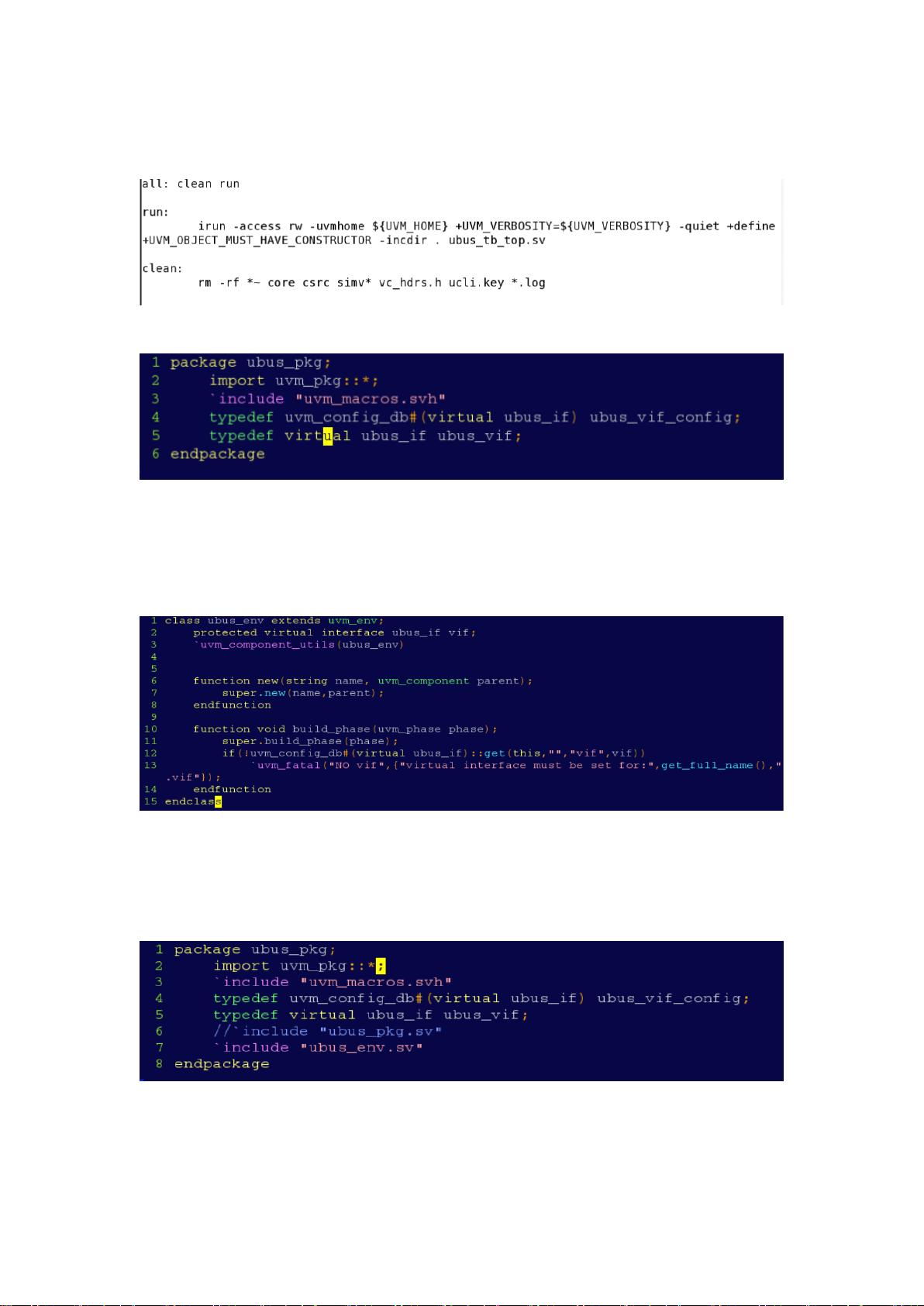

5. 写 Makefile ,此时编译可以通过

6. 写自定义的 package ,然后在 top 中 include 该 package

typedef

typedef

typedef

typedef uvm_config_db#(virtual

uvm_config_db#(virtual

uvm_config_db#(virtual

uvm_config_db#(virtual ubus_if)

ubus_if)

ubus_if)

ubus_if) ubus_vif_config;

ubus_vif_config;

ubus_vif_config;

ubus_vif_config;

typedef

typedef

typedef

typedef virtual

virtual

virtual

virtual ubus_if

ubus_if

ubus_if

ubus_if ubus_vif;

ubus_vif;

ubus_vif;

ubus_vif;

后来证明,这两句话在 ubus

ubus

ubus

ubus 的 env

env

env

env 中根本没有用上;

7. 定义 Environment ,并将该文件加入到自定义的 package 中,这个时候编译不能通过

此处的 get

get

get

get 和 top

top

top

top 中的 set

set

set

set 是一对 , 如果 top

top

top

top 中没有 set

set

set

set 则会报告 · uvm_fatal

uvm_fatal

uvm_fatal

uvm_fatal 中的错误

if(!uvm_config_db#(virtual

if(!uvm_config_db#(virtual

if(!uvm_config_db#(virtual

if(!uvm_config_db#(virtual ubus_if)::get(this,

ubus_if)::get(this,

ubus_if)::get(this,

ubus_if)::get(this, "",

"",

"",

"", "vif",

"vif",

"vif",

"vif", vif))

vif))

vif))

vif))

`uvm_fatal("NOVIF",{"virtual

`uvm_fatal("NOVIF",{"virtual

`uvm_fatal("NOVIF",{"virtual

`uvm_fatal("NOVIF",{"virtual interface

interface

interface

interface must

must

must

must be

be

be

be set

set

set

set for:

for:

for:

for:

",get_full_name(),".vif"});

",get_full_name(),".vif"});

",get_full_name(),".vif"});

",get_full_name(),".vif"});

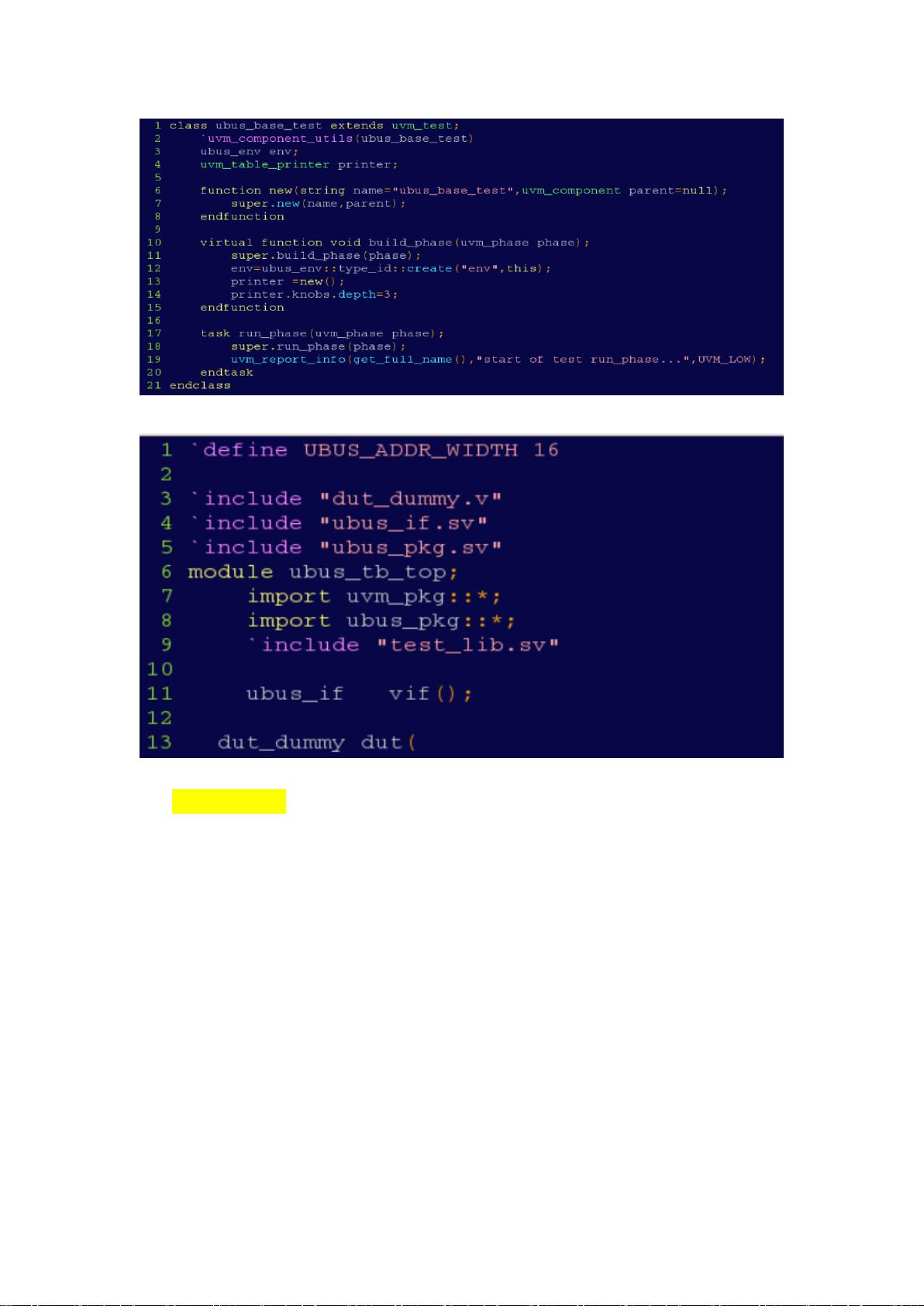

8. 定义 base_test ,需要在 top 中 include 该 test 文件,并在 makefile 中加入编译该 test 的

命令;此时可以再次编译通过,并运行最 basic 的 testcase

3

编译第一次通过

总结一 : 在一个芯片的验证平台中 , 总会给一个最 basic

basic

basic

basic 的 base_test

base_test

base_test

base_test , 但是可能每个人

负责验证的部分是不一样的,比如说我要验证 USB

USB

USB

USB ,那我一定会从 base_test

base_test

base_test

base_test 中派生一 个

usb_base_test

usb_base_test

usb_base_test

usb_base_test 来给自己用 , 这样我可以在 usb_base_test

usb_base_test

usb_base_test

usb_base_test 加入任何我想要的函数 , 而不会影

响到其他人。

总结二 : 如何从 test

test

test

test 中传递参数到 top_tb,

top_tb,

top_tb,

top_tb, 如果用 uvm_config_db

uvm_config_db

uvm_config_db

uvm_config_db 在 base_test

base_test

base_test

base_test 中设置变

量的值 , 那么这些变量在 environment/agent/dirver

environment/agent/dirver

environment/agent/dirver

environment/agent/dirver 等等中可以 get

get

get

get 到的 , 但是在 top_tb

top_tb

top_tb

top_tb 中

不能 get

get

get

get 到的?采用下面的方式就可以

uvm_config_db

uvm_config_db

uvm_config_db

uvm_config_db #(int)::set(null,"uvm_test_top","set_

#(int)::set(null,"uvm_test_top","set_

#(int)::set(null,"uvm_test_top","set_

#(int)::set(null,"uvm_test_top","set_ usb

usb

usb

usb _single_test",1);

_single_test",1);

_single_test",1);

_single_test",1);

总结三 : 需要注意的是 , 不要把定义 interface

interface

interface

interface 的文件 include

include

include

include 在 package

package

package

package 中 , 这会导致

编译不过的。

4

总结四 : uvm_report_info

uvm_report_info

uvm_report_info

uvm_report_info 和宏 `uvm_info

`uvm_info

`uvm_info

`uvm_info 在用法是没有区别的 , 都是用来打印消息的 。

[1-

[1-

[1-

[1- 2

2

2

2 ]

]

]

] 如何顺序的写 UVM

UVM

UVM

UVM 平台( 2

2

2

2 ) -MasterAgent

-MasterAgent

-MasterAgent

-MasterAgent

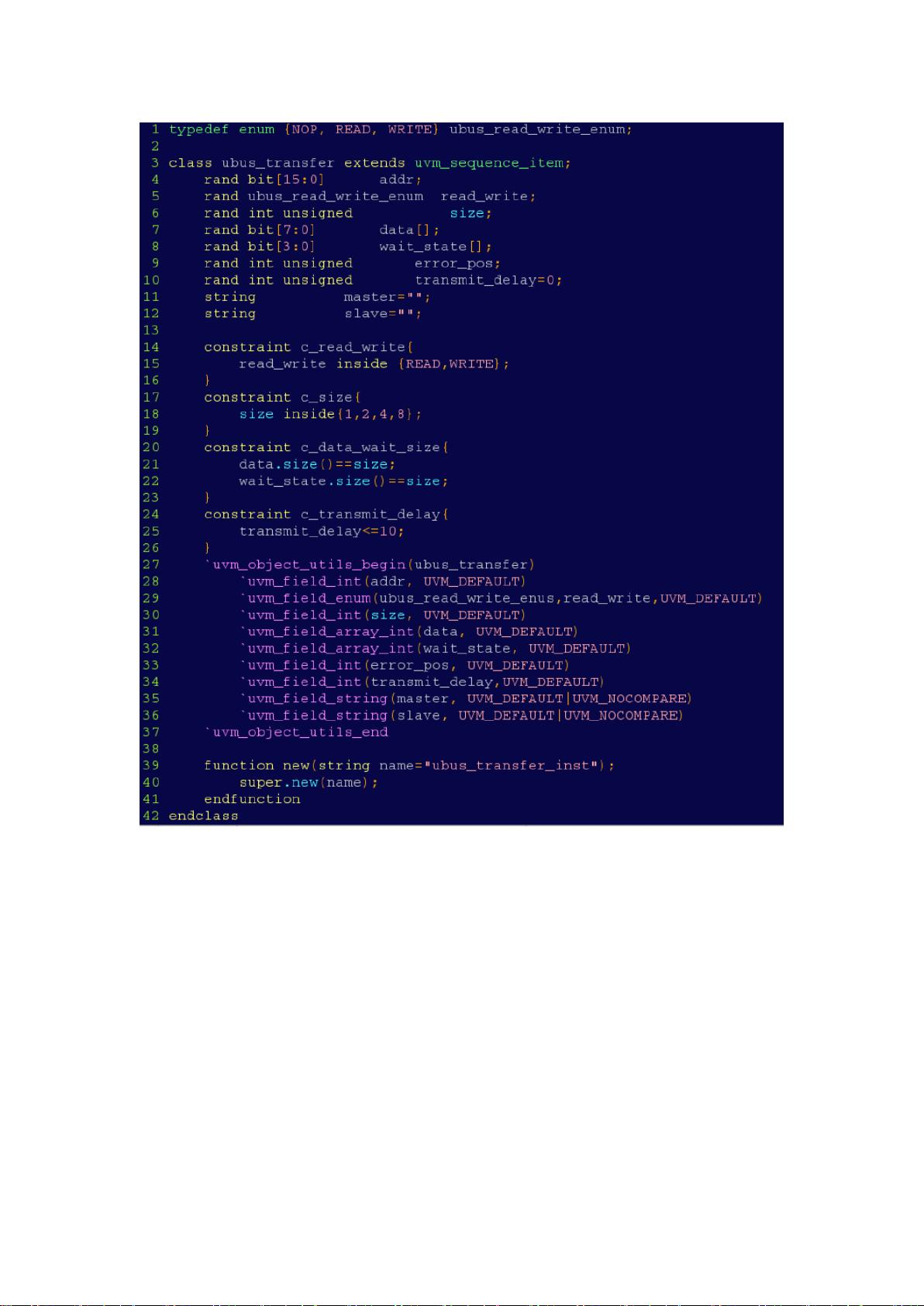

9. 定义 sequence item ,注意,一种类型的 transaction 需要对应一个 driver ;

`uvm_object_utils_begin(ubus_transfer)

`uvm_object_utils_begin(ubus_transfer)

`uvm_object_utils_begin(ubus_transfer)

`uvm_object_utils_begin(ubus_transfer)

`uvm_field_int

`uvm_field_int

`uvm_field_int

`uvm_field_int (addr,

(addr,

(addr,

(addr, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_enum

`uvm_field_enum

`uvm_field_enum

`uvm_field_enum (ubus_read_write_enum,

(ubus_read_write_enum,

(ubus_read_write_enum,

(ubus_read_write_enum, read_write,

read_write,

read_write,

read_write, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_int

`uvm_field_int

`uvm_field_int

`uvm_field_int (size,

(size,

(size,

(size, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_array_int(data,

`uvm_field_array_int(data,

`uvm_field_array_int(data,

`uvm_field_array_int(data, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_array_int(wait_state,

`uvm_field_array_int(wait_state,

`uvm_field_array_int(wait_state,

`uvm_field_array_int(wait_state, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_int

`uvm_field_int

`uvm_field_int

`uvm_field_int (error_pos,

(error_pos,

(error_pos,

(error_pos, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_int

`uvm_field_int

`uvm_field_int

`uvm_field_int (transmit_delay,

(transmit_delay,

(transmit_delay,

(transmit_delay, UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

UVM_DEFAULT)

`uvm_field_string

`uvm_field_string

`uvm_field_string

`uvm_field_string (master,

(master,

(master,

(master, UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

`uvm_field_string

`uvm_field_string

`uvm_field_string

`uvm_field_string (slave,

(slave,

(slave,

(slave, UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

UVM_DEFAULT|UVM_NOCOMPARE)

`uvm_object_utils_end

`uvm_object_utils_end

`uvm_object_utils_end

`uvm_object_utils_end

5

需要思考哪些内容需要在 transaction 中定义?

10. 定义好了 transaction ,就可以开始定义 base sequence 了;注意,在 base_sequence 的

pre_body 和 post_body 中定义 raise_objection 和 drop_objection 是很有好处的;将 base

sequence 定义成虚基类,只有派生后才能进行实例化;

剩余49页未读,继续阅读

资源评论

sunbox982019-04-27初看挺实用,期待进一步阅读

sunbox982019-04-27初看挺实用,期待进一步阅读 验师2019-08-18值得再次回味~

验师2019-08-18值得再次回味~ cs8249808202021-01-26比较基础,还是值得看一下

cs8249808202021-01-26比较基础,还是值得看一下

qq_28582821

- 粉丝: 1

- 资源: 1

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 生菜生长记录数据集(3K+ 记录,7特征) CSV

- 国际象棋检测2-YOLO(v5至v9)、COCO、CreateML、Darknet、Paligemma、TFRecord数据集合集.rar

- RGMII delay问题

- Python结合Pygame库实现圣诞主题动画和音乐效果的代码示例

- 国际象棋检测2-YOLO(v5至v11)、COCO、CreateML、Paligemma、TFRecord、VOC数据集合集.rar

- ssd5课件图片记录保存

- 常用算法介绍与学习资源汇总

- Python与Pygame实现带特效的圣诞节场景模拟程序

- 国际象棋检测11-YOLO(v7至v9)、COCO、Darknet、Paligemma、VOC数据集合集.rar

- 使用Python和matplotlib库绘制爱心图形的技术教程

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功