DS228 March 1, 2011 www.xilinx.com 1

Product Specification

© Copyright 2005-2006, 2009-2011, Xilinx, Inc. XILINX, the Xilinx logo, ISE, Kintex, Spartan, Virtex, and other designated brands included herein are trademarks of

Xilinx in the United States and other countries. MATLAB and Simulink are registered trademarks of The MathWorks, Inc. All other trademarks are the property of their

respective owners.

Introduction

The Xilinx

®

LogiCORE™ IP RAM-based Shift Register

core provides a very efficient multi-bit wide shift

register for use in FIFO-like applications or as a delay

line. Fixed-length shift registers and variable-length

shift registers can be created.

Features

• Drop-in module for Virtex

®

-7 and Kintex™-7,

Virtex-6, Virtex-5, Virtex-4, Spartan

®

-6,

Spartan-3/XA, Spartan-3E/XA,

Spartan-3A/3AN/3A DSP/XA FPGAs

• Generates fast, compact, FIFO-style shift registers

or delay lines using the SRL16/SRL32 mode of the

slice LUTs

• User options to create fixed-length or

variable-length shift registers

• Speed or resource optimization for variable length

shift registers

• Optional output register with clock enable and

synchronous controls for variable length shift

registers

• For use with Xilinx CORE Generator™ and Xilinx

System Generator for DSP 13.1

LogiCORE IP

RAM-based Shift Register v11.0

DS228 March 1, 2011 Product Specification

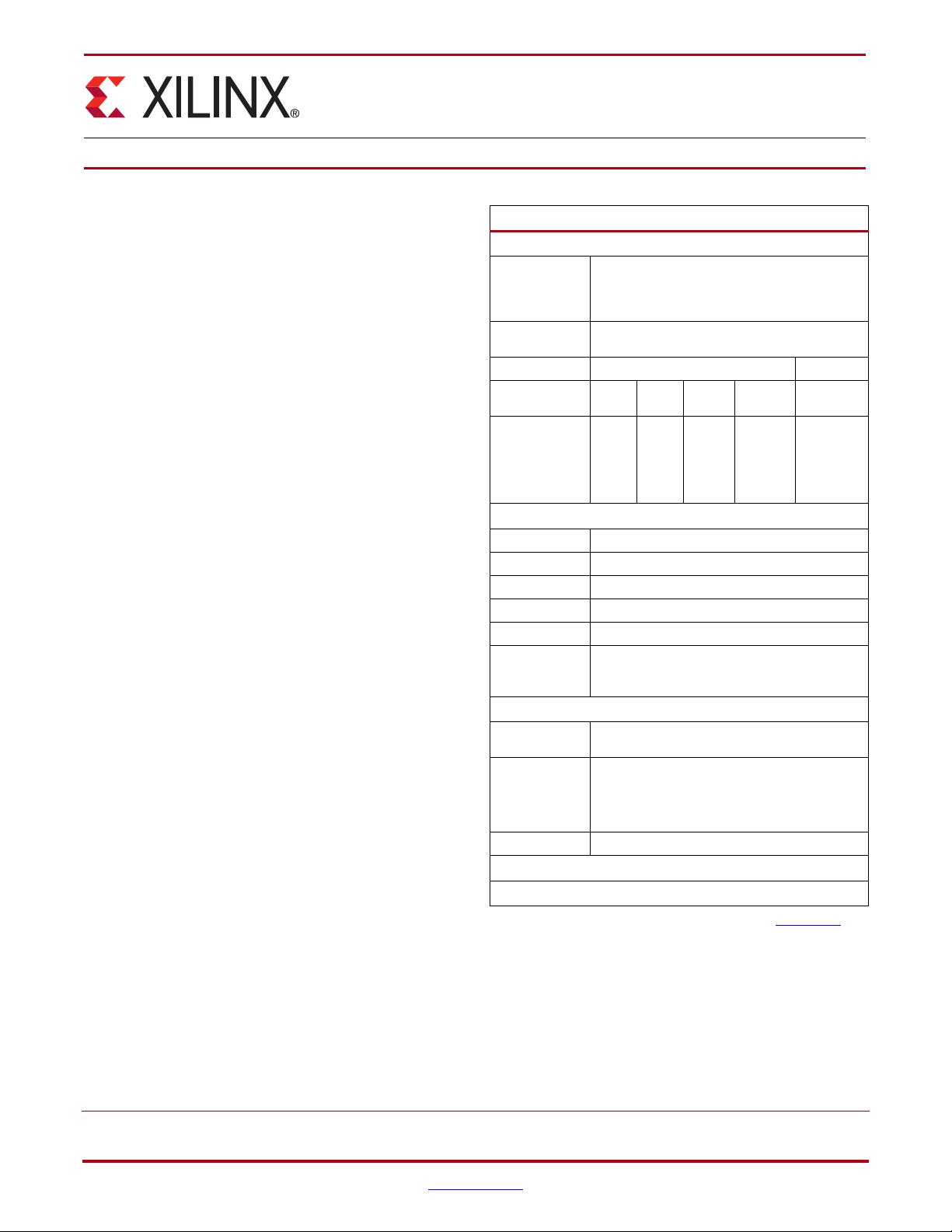

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

1. For a complete listing of supported devices, see the release notes

for this core.

Virtex-7 and Kintex-7

Virtex-6, Virtex-5, Virtex-4,

Spartan-6, Spartan-3/XA, Spartan-3E/XA,

Spartan-3A/3AN/3ADSP/XA

Supported User

Interfaces

Not Applicable

Resources

(2)

2. For more complete device performance numbers, see

Performance and Resource Utilization, page 6.

Frequency

Configuration LUTs FFs

DSP

Slices

Block

RAMs

Max. Freq.

Virtex-5,

variable length,

32-deep,

16-wide shift

register

16 16 0 0 452 MHz

Provided with Core

Documentation Product Specification

Design Files Netlist

Example Design Not Provided

Test Bench Not Provided

Constraints File Not Applicable

Simulation

Model

VHDL behavioral model in the xilinxcorelib library

VHDL UniSim structural model

Verilog UniSim structural model

Tested Design Tools

Design Entry

Tools

CORE Generator tool 13.1

System Generator for DSP 13.1

Simulation

Mentor Graphics ModelSim 6.6d

Cadence Incisive Enterprise Simulator (IES) 10.2

Synopsys VCS and VCS MX 2010.06

ISIM 13.1

Synthesis Tools N/A

Support

Provided by Xilinx, Inc.