ST7796S

320RGB x 480 dot 262K Color with Frame Memory

Single-Chip TFT Controller/Driver

Datasheet

Sitronix reserves the right to change the contents in this document

without prior notice, please contact Sitronix to obtain the latest

version of datasheet before placing your order. No responsibility is

assumed by Sitronix for any infringement of patent or other rights

of third parties which may result from its use.

2013 Sitronix Technology Corporation. All rights reserved.

Version V1.0

2014/11

ST7796S

V1.0 Page 2 of 279 2014/11

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or

disclosed in whole or in part without prior written permission of Sitronix.

LIST OF CONTENT

1

GENERAL DESCRIPTION ..................................................................... 7

2

FEATURES ............................................................................................ 8

3

PAD ARRANGEMENT ......................................................................... 10

3.1.. Output Bump Dimension .................................................................................... 10

3.2.. Bump Dimension ............................................................................................... 11

3.3.. Alignment Mark Dimension ................................................................................ 12

3.4.. Chip Information ................................................................................................ 12

4

PAD CENTER COORDINATES ........................................................... 13

5

BLOCK DIAGRAM ............................................................................... 40

6

PIN DESCRIPTION .............................................................................. 41

6.1.. Power Supply Pins ............................................................................................. 41

6.2.. Interface Logic Pins ........................................................................................... 42

6.3.. Driver Output Pins ............................................................................................. 44

6.4.. Test and Other Pins ........................................................................................... 45

7

DRIVER ELECTRICAL CHARACTERISTICS ...................................... 46

7.1.. Absolute Operation Range ................................................................................ 46

7.2.. DC Characteristics ............................................................................................. 47

7.2.1

DC characteristics for MIPI DSI ...................................................................................... 47

7.2.2

DC Characteristics for Panel Driving ............................................................................. 48

7.3.. Power Consumption .......................................................................................... 50

7.4.. AC Characteristics ............................................................................................. 51

7.4.1

8080 Series MCU Parallel Interface Characteristics: 18/16/9/8-bit Bus ...................... 51

7.4.2

3-SPI Serial Data Transfer Interface Characteristics: ................................................... 53

7.4.3

4-SPI Serial Data Transfer Interface Characteristics: ................................................... 54

7.4.4

RGB Interface Characteristics: ....................................................................................... 55

7.4.5

MIPI Interface Characteristics ......................................................................................... 56

8

INTERFACE ......................................................................................... 59

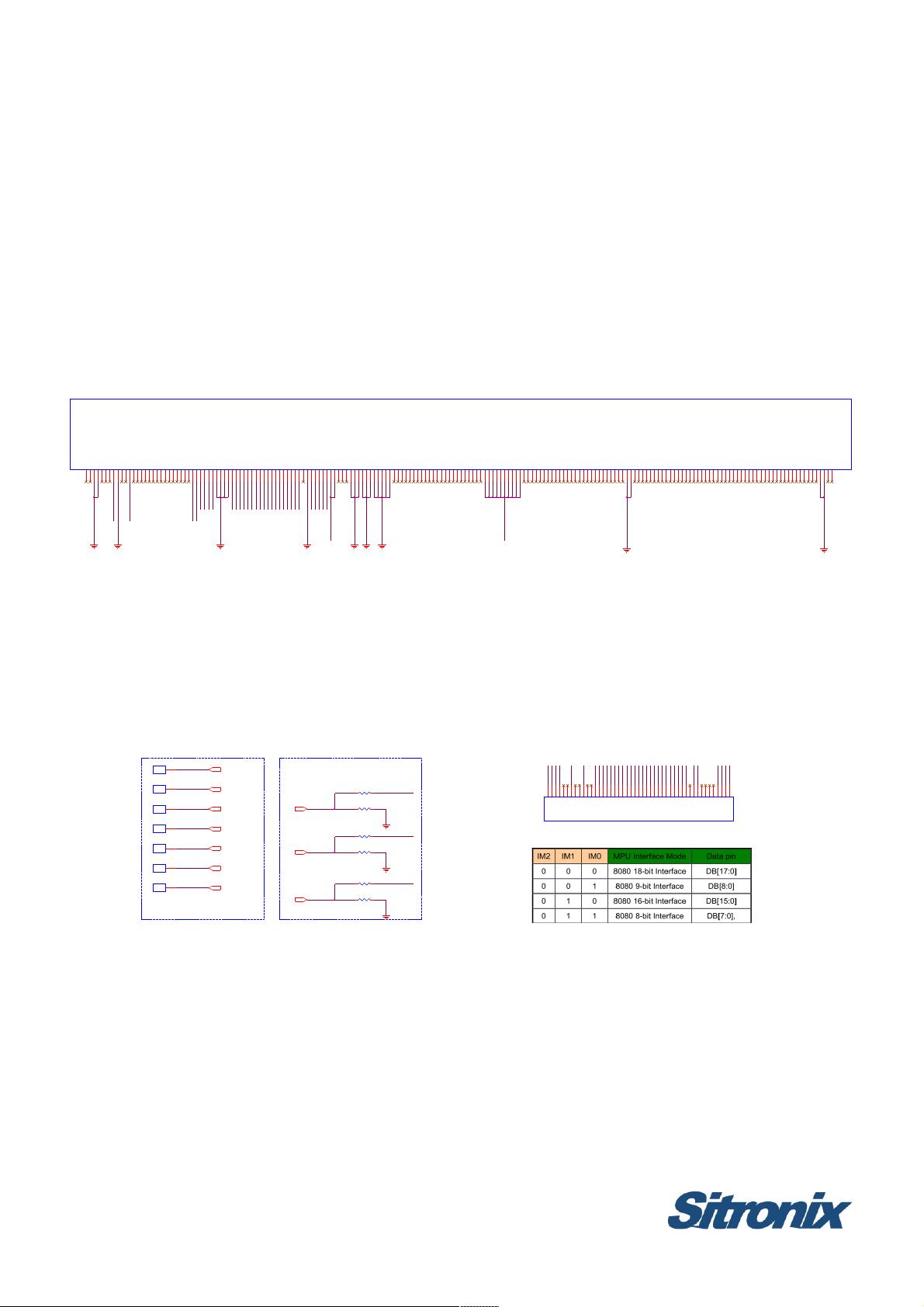

8.1.. MPU Interface Type Selection ........................................................................... 59

8.2.. 8080-Series MCU Interface ............................................................................... 60

8.2.1

8080-Series MCU Write Cycle Sequence ....................................................................... 60

8.2.2

18-bit 8080-Series Interface Write Format ..................................................................... 61

8.2.3

16-bit 8080-Series Interface Write Format ..................................................................... 63

8.2.4

9-bit 8080-Series Interface Write Format ....................................................................... 67

8.2.5

8-bit 8080-Series Interface Write Format ....................................................................... 69

8.2.6

8080-series MCU Read Cycle Sequence ........................................................................ 73

8.2.7

18-bit 8080-Series Interface Read Format ...................................................................... 74

8.2.8

16-bit 8080-Series Interface Read Format ...................................................................... 75

ST7796S

V1.0 Page 3 of 279 2014/11

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or

disclosed in whole or in part without prior written permission of Sitronix.

8.2.9

9-bit 8080-Series Interface Read Format ........................................................................ 76

8.2.10

8-bit 8080-Series Interface Read Format ........................................................................ 77

8.3.. RGB Interface .................................................................................................... 78

8.3.1

RGB Color Format ............................................................................................................ 78

8.3.2

RGB Interface Definition .................................................................................................. 80

8.3.3

RGB Interface Timing ....................................................................................................... 82

8.4.. Serial Peripheral Interface (SPI) ........................................................................ 85

8.4.1

3-Line Interface ................................................................................................................. 85

8.4.2

4-Line Interface ................................................................................................................. 89

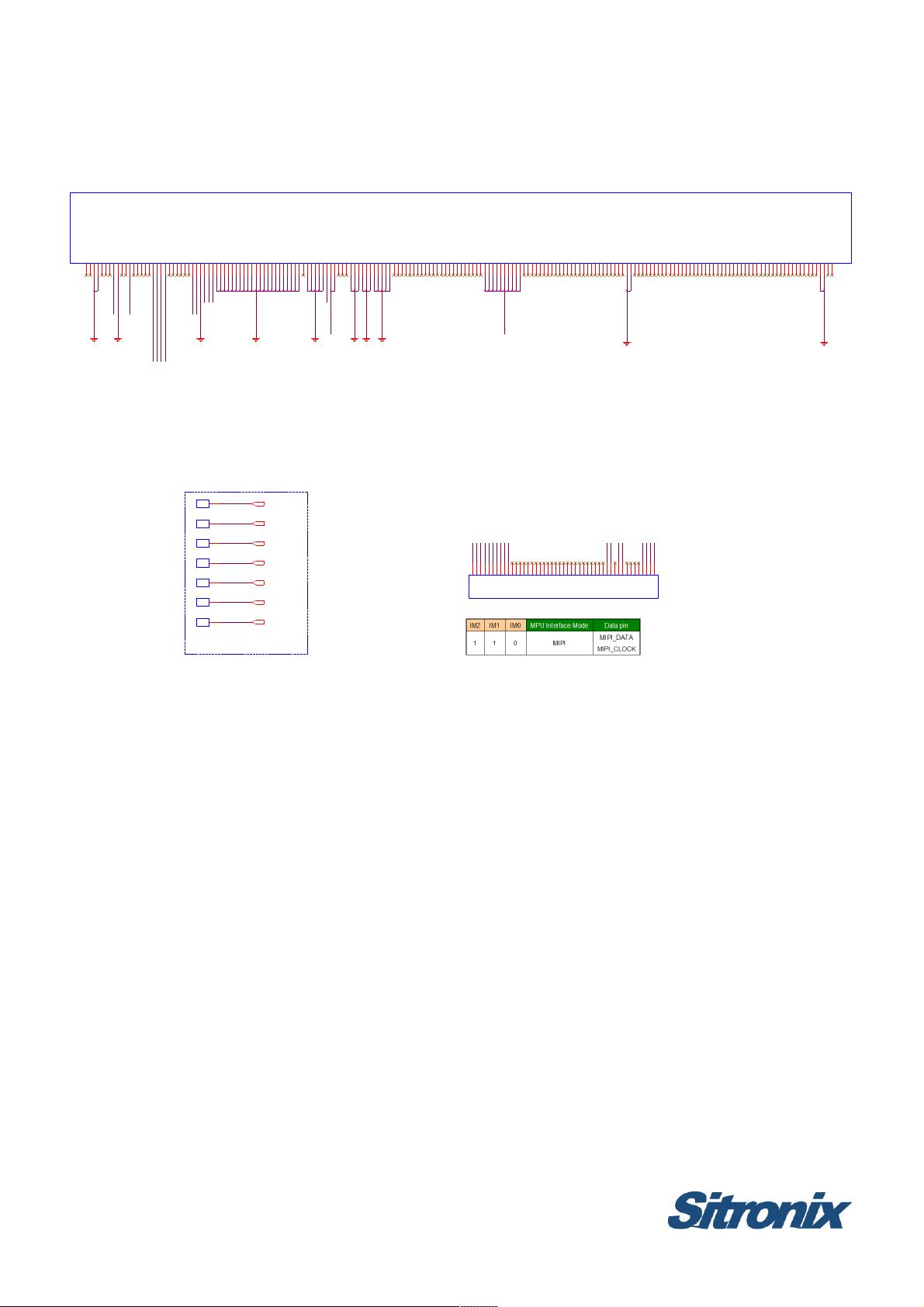

8.5.. Mobile Industry Processor Interface (MIPI) ........................................................ 94

8.5.1

Display Serial Interface (DSI) .......................................................................................... 94

8.5.2

DSI protocol .................................................................................................................... 110

9

COMMAND ......................................................................................... 131

9.1.. Command Table List ........................................................................................ 131

9.2.. Command Table 1 ........................................................................................... 141

9.2.1

NOP (00h) ........................................................................................................................ 141

9.2.2

SWRESET (01h): Software Reset .................................................................................. 141

9.2.3

RDDID (04h): Read Display ID ....................................................................................... 143

9.2.4

Read Number of the Errors on DSI (05h) ..................................................................... 144

9.2.5

RDDST (09h): Read Display Status .............................................................................. 146

9.2.6

RDDPM (0Ah): Read Display Power Mode ................................................................... 149

9.2.7

RDDMADCTL (0Bh): Read Display MADCTL ............................................................... 151

9.2.8

RDDCOLMOD (0Ch): Read Display Pixel Format ........................................................ 153

9.2.9

RDDIM (0Dh): Read Display Image Mode ..................................................................... 155

9.2.10

RDDSM (0Eh): Read Display Signal Mode ................................................................... 156

9.2.11

RDDSDR (0Fh): Read Display Self-Diagnostic Result ................................................ 158

9.2.12

SLPIN (10h): Sleep in ..................................................................................................... 159

9.2.13

SLPOUT (11h): Sleep Out .............................................................................................. 160

9.2.14

PTLON (12h): Partial Display Mode On ........................................................................ 163

9.2.15

NORON (13h): Normal Display Mode On ..................................................................... 164

9.2.16

INVOFF (20h): Display Inversion Off ............................................................................ 165

9.2.17

INVON (21h): Display Inversion On .............................................................................. 166

9.2.18

DISPOFF (28h): Display Off ........................................................................................... 167

9.2.19

DISPON (29h): Display On ............................................................................................. 169

9.2.20

CASET (2Ah): Column Address Set ............................................................................. 170

9.2.21

RASET (2Bh): Row Address Set ................................................................................... 172

9.2.22

RAMWR (2Ch): Memory Write ....................................................................................... 173

9.2.23

RAMRD (2Eh): Memory Read ........................................................................................ 174

ST7796S

V1.0 Page 4 of 279 2014/11

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or

disclosed in whole or in part without prior written permission of Sitronix.

9.2.24

PTLAR (30h): Partial Area .............................................................................................. 176

9.2.25

VSCRDEF (33h): Vertical Scrolling Definition ............................................................. 178

9.2.26

TEOFF (34h): Tearing Effect Line OFF ......................................................................... 180

9.2.27

TEON (35h): Tearing Effect Line On ............................................................................. 181

9.2.28

MADCTL (36h): Memory Data Access Control ............................................................ 183

9.2.29

VSCSAD (37h): Vertical Scroll Start Address of RAM ................................................ 185

9.2.30

IDMOFF (38h): Idle Mode Off ......................................................................................... 187

9.2.31

IDMON (39h): Idle mode on ........................................................................................... 188

9.2.32

COLMOD (3Ah): Interface Pixel Format ....................................................................... 190

9.2.33

WRMEMC (3Ch): Write Memory Continue ................................................................... 191

9.2.34

RDMEMC (3Eh): Read Memory Continue ..................................................................... 193

9.2.35

STE (44h): Set Tear Scanline......................................................................................... 194

9.2.36

GSCAN (45h): Get Scanline ........................................................................................... 196

9.2.37

WRDISBV (51h): Write Display Brightness .................................................................. 197

9.2.38

RDDISBV (52h): Read Display Brightness Value ........................................................ 198

9.2.39

WRCTRLD (53h): Write CTRL Display .......................................................................... 199

9.2.40

RDCTRLD (54h): Read CTRL value Display ................................................................. 201

9.2.41

WRCABC (55h): Write Adaptive Brightness Control .................................................. 202

9.2.42

RDCABC (56h): Read Content Adaptive Brightness Control .................................... 204

9.2.43

WRCABCMB (5Eh): Write CABC Minimum Brightness .............................................. 205

9.2.44

RDCABCMB (5Fh): Read CABC Minimum Brightness ............................................... 207

9.2.45

RDFCS (Aah): Read First Checksum ............................................................................ 208

9.2.46

RDCFCS (Afh): Read Continue Checksum .................................................................. 208

9.2.47

RDID1 (Dah): Read ID1 ................................................................................................... 209

9.2.48

RDID2 (DBh): Read ID2 .................................................................................................. 210

9.2.49

RDID3 (DCh): Read ID3 .................................................................................................. 211

9.3.. Command Table 2 ........................................................................................... 212

9.3.1

IFMODE (B0h): Interface Mode Control ........................................................................ 212

9.3.2

FRMCTR1 (B1h): Frame Rate Control (In Normal Mode/Full Colors) ........................ 213

9.3.3

FRMCTR2 (B2h): Frame Rate Control 2 (In Idle Mode/8 colors) ................................ 214

9.3.4

FRMCTR3 (B3h): Frame Rate Control3 (In Partial Mode/Full Colors) ....................... 215

9.3.5

DIC (B4): Display Inversion Control ............................................................................. 216

9.3.6

BPC(B5): Blanking Porch Control ................................................................................ 217

9.3.7

DFC(B6): Display Function Control .............................................................................. 218

9.3.8

EM(B7): Entry Mode Set ................................................................................................. 222

9.3.9

PWR1(C0h): Power Control 1 ........................................................................................ 223

9.3.10

PWR2 (C1h): Power Control 2 ....................................................................................... 224

9.3.11

PWR3 (C2h): Power Control 3 ....................................................................................... 227

ST7796S

V1.0 Page 5 of 279 2014/11

Sitronix Confidential The information contained herein is the exclusive property of Sitronix and shall not be distributed, reproduced, or

disclosed in whole or in part without prior written permission of Sitronix.

9.3.12

VCMPCTL(C5h): VCOM Control .................................................................................... 227

9.3.13

VCM Offset (C6h): Vcom Offset Register ..................................................................... 229

9.3.14

NVMADW (D0h): NVM Address/Data Write .................................................................. 230

9.3.15

NVMBPROG (D1h): NVM Byte Program ....................................................................... 231

9.3.16

NVM Status Read(D2h) .................................................................................................. 232

9.3.17

RDID4 (D3h): Read ID4 ................................................................................................... 233

9.3.18

PGC (E0h): Positive Gamma Control ........................................................................... 233

9.3.19

NGC (E1h): Negative Gamma Control .......................................................................... 235

9.3.20

DGC1(E2h): Digital Gamma Control 1 .......................................................................... 236

9.3.21

DGC2 (E3h): Digital Gamma Control 2 ......................................................................... 237

9.3.22

DOCA (E8h): Display Output Ctrl Adjust ..................................................................... 237

9.3.23

CSCON (F0h): Command Set Control .......................................................................... 239

9.3.24

SPI Read Control (FBh) .................................................................................................. 240

10

Function Description ........................................................................ 241

10.1.. Display Data RAM ........................................................................................... 241

10.1.1

Configuration .................................................................................................................. 241

10.1.2

Memory to display address mapping ........................................................................... 242

10.2.. Address Control ............................................................................................... 243

10.3.. Data Transfer Break and Recovery ................................................................. 245

10.4.. Data Transfer Pause ........................................................................................ 246

10.5.. Data Transfer Mode ......................................................................................... 246

10.5.1

Method 1 .......................................................................................................................... 246

10.5.2

Method 2 .......................................................................................................................... 247

10.6.. Normal Display On or Partial Mode On, Vertical Scroll Off .............................. 247

10.7.. Vertical Scroll Mode ......................................................................................... 249

10.7.1

Rolling scroll ................................................................................................................... 249

10.7.2

Vertical Scroll Example .................................................................................................. 250

10.8.. Tearing Effect .................................................................................................. 251

10.8.1

Tearing effect line modes .............................................................................................. 251

10.8.2

Tearign effect line timings ............................................................................................. 252

10.8.3

Example 1: MPU Write is faster than panel read ......................................................... 254

10.8.4

Example 2: MPU write is slower than panel read ........................................................ 255

10.9.. Gamma Correction .......................................................................................... 255

10.10.. Gray voltage generator for digital gamma correction .................................... 260

10.11.. Display Dimming ........................................................................................... 261

10.11.1

Dimming Requirement ................................................................................................... 261

10.11.2

Definition of brightness transition time ....................................................................... 262

10.12.. Content Adaptive Brightness Control (CABC) ............................................... 264

评论0