没有合适的资源?快使用搜索试试~ 我知道了~

Lenovo B465 (Bitland BM5016) Laptop Schematics.pdf

需积分: 5 0 下载量 161 浏览量

2023-12-28

15:40:43

上传

评论

收藏 1.7MB PDF 举报

温馨提示

试读

54页

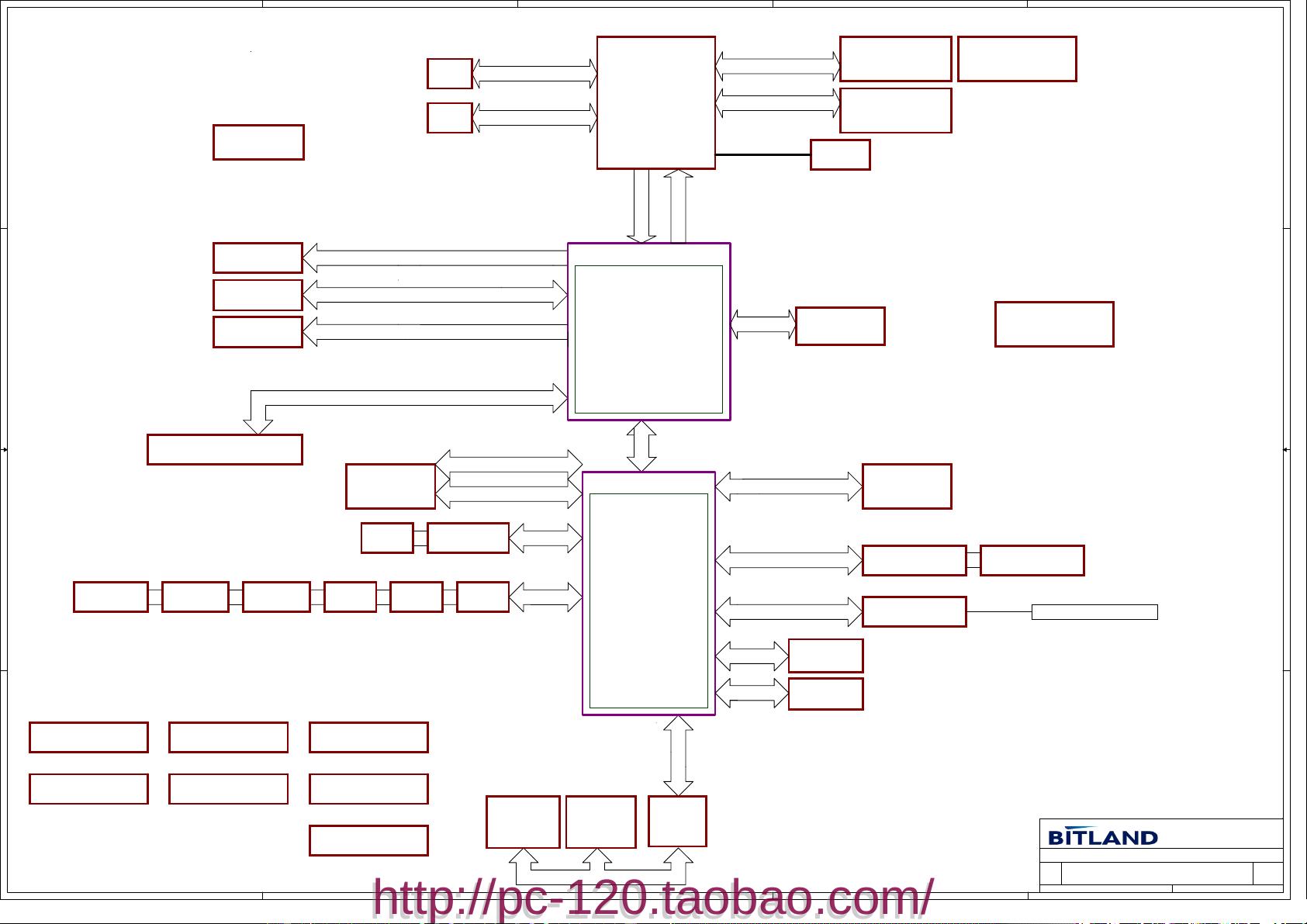

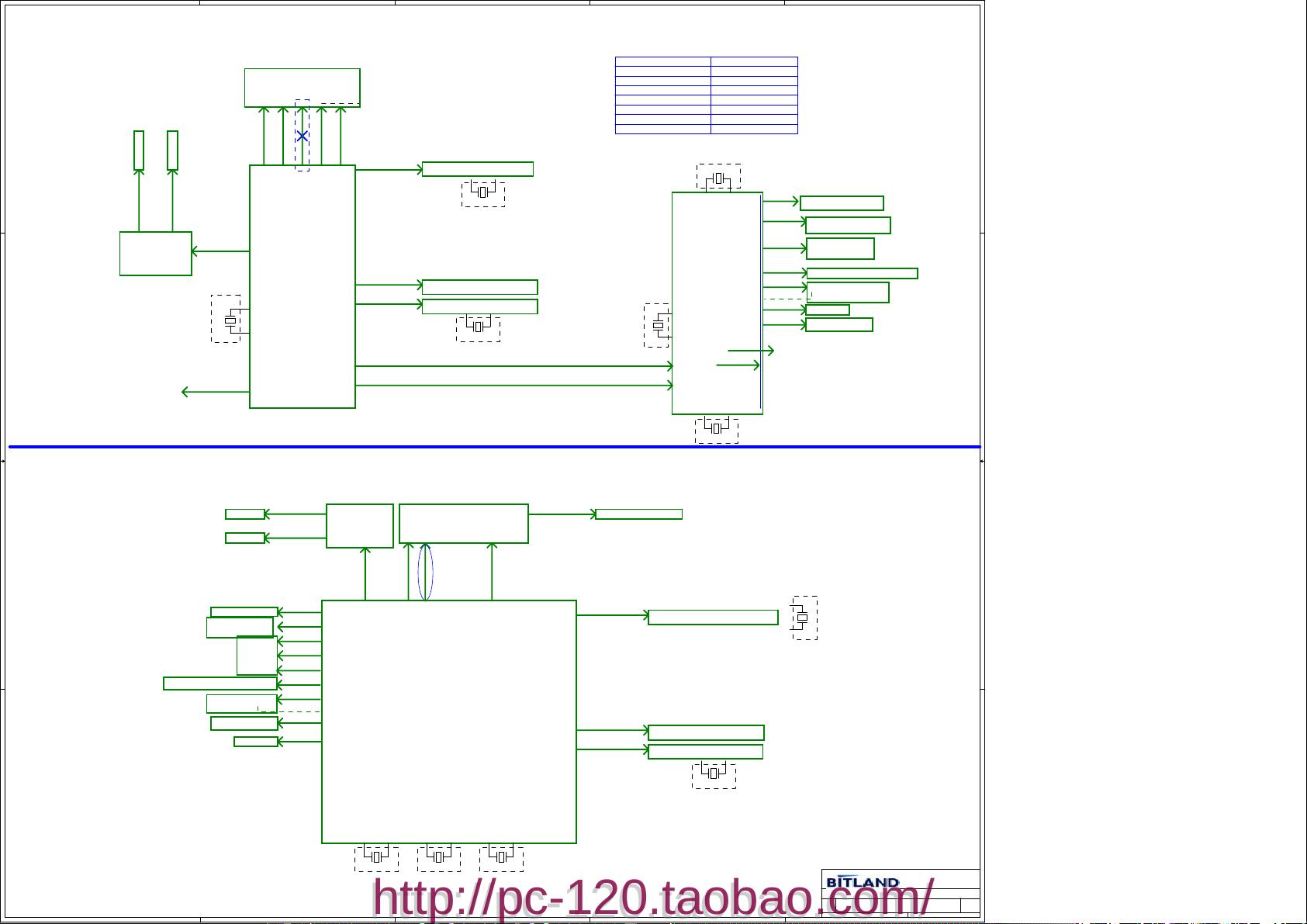

Lenovo B465 (Bitland BM5016) Laptop Schematics

资源推荐

资源详情

资源评论

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

X4

USB#1USB#3

46

48

LAN&CARDREADER JMC261

I2C I/F

7

USB 2.0

USB#0

ACPI 1.1

PCIE

SB820M

BATTERY CHAGER

HD AUDIO

LPC I/F

SPI I/F

CPU CORE

8

9

GUAM S1G4 SCHEMATIC DESIGN

28

SPI ROM

SPI I/F

HW MONITOR

28

CPU MEMORY POWER

SYSTEM MAIN POWER

13

30

BOOTSTRAPS

ROM (SB)

HW MONITOR I/F

HD AUDIO I/F

SATA III I/F

46

26,27,28,29

46

AZALIA CODEC

CX20671

42

PRELIMINARY

Mobile 2.5" HDD Mobile ODD

CPU Tempreture Sensor

11

1.5V/1.5VDUAL/

1.8V/3.3V/5V

DISCHARGE CIRCUIT

55

RESET,FAN

& ENABLES

PS2

TOUCH PAD

SCANNED

MATRIX

KEYBOARD

SIM

card

socket

49

41

41

INT. RTC

USB2.0 (14)+1.1(2)

SATA III (6 PORTS)

PCI/PCI BDGE

HW MONITOR

4 X1 PCIE GEN2 I/F

GB MAC

EC

INT. CLK GEN.

1V1DUAL/VLDT/

VCC_NB/+1.1V

10

USB#6

Finger Print

Reader

45

USB#7

Bluetooth

45

LVDS MUX

LVDS CON

43

GPP PCIE INTERFACE

AMD S1G4 CPU

RS880M

14,15,16,17

DX10 IGP

1 X4 PCIE I/F WITH SB

1 X16 PCIE I/F

6 X1 PCIE I/F

LVDS/TVOUT/TMDS

EXTERNAL CLOCK GENERATOR

20

21,22,23,24,25

24

BOOTSTRAPS

ROM(NB)

I2C I/F

CRT MUX

VGA CON

44

16x16

LINK0

DISPLAY PORT X2

HyperTransport

IN

OUT

HyperTransport LINK0 CPU I/F

UNBUFFERED DDR3

NEAR SODIMM

UNBUFFERED DDR3

FAR SODIMM

18,19

18,19

SLG8LP625

Channel A

16

16

SB-TSI

52

Ambient Light Sensor

Channel B

DDR III, 1333MT/S

HDT

16

SCAN

16

Side Port Memory

Optional CPU

Temperature sensor

GPP INTERFACE

PARK_XT_S3

X16 PCIE MUX

MINIPCIE

IT8502E

EC

49

47

MINIPCIE WIFI

31--40

USB 2.0

USB#8

USB 2.0

USB#4

USB#5

CAM

45

4949

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

1

BM5016

BLOCK DIAGRAM

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

1

BM5016

BLOCK DIAGRAM

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

1

BM5016

BLOCK DIAGRAM

1.0

http://pc-120.taobao.com/

http://pc-120.taobao.com/

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

TABLE OF CONTENTS

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

2

BM5016

TABLE OF CONTENTS

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

2

BM5016

TABLE OF CONTENTS

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

2

BM5016

TABLE OF CONTENTS

1.0

http://pc-120.taobao.com/

http://pc-120.taobao.com/

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

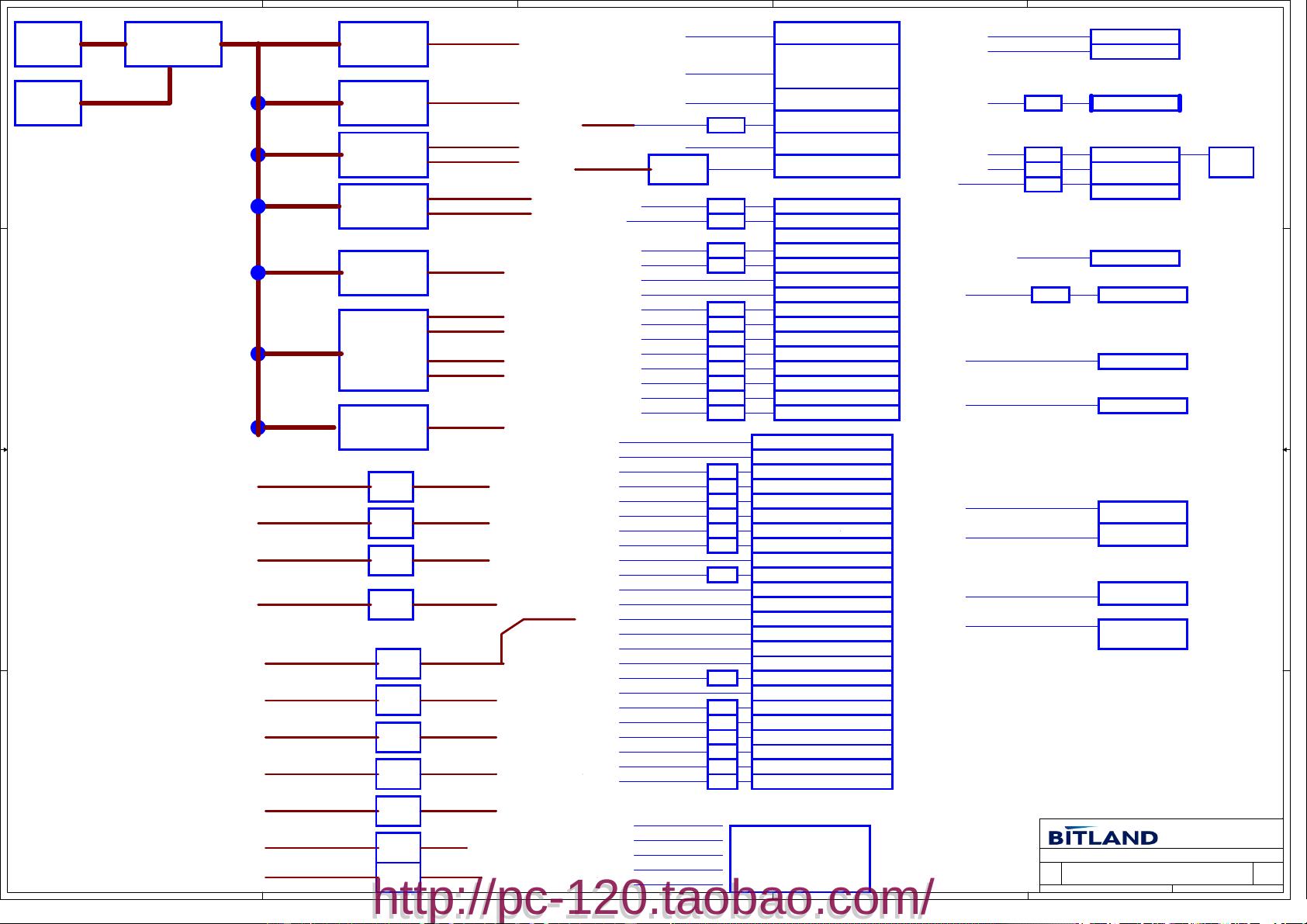

+1.8V SW

MAX8716-2/2

+1.8V@1.3A

+1.8V

+1.1V

RS880M

VDDPCIE 1.1V 1.1A

VDDHTTX 1.2V 0.68A

PLLs 1.8V 0.1A

VDDC 1.0V-1.1V 7.6A

VLDT

BEAD

VDDHTRX+HT 1.1V 0.68A

BEAD

AVDD 3.3V 0.125A

VDDA18 1.8V 0.64A

+VCC_NB

VDDG33 3.3V 0.06A

VDDG18 1.8V 0.005A

VDD18_MEM 1.8V 0.005A

VDD_MEM 1.8V 0.23A

+1.8V

VDDLT18 0.22A

VDDLT33 0A

PLLs 1.1/1.2V 0.23A

BEAD

BEAD

BEAD

BEAD

AOZ1024

PWM

+5V

BEAD

BEAD

BEAD

BEAD

+3.3V

+1.5V

+1.5V

+1.8V

+1.8V

+3.3V

+3.3V

+1.1V

+1.1V

BEAD

BEAD

VDD CORE

1.375-1.500V 36A

BEAD

VLDT

VDDNB CORE

0.9V 4A

CPU_VDD_RUN

CPU_VDDNB_RUN

CPU_VDDA_RUN

VDD MEM TPDA

VDDR 1.5A

CPU_VDDIO_SUS

VDDR

VCCA 2.5V

VLDT 1.2V TPDA

AMD S1G4

+VCC_NB_RUN

+1V~1.2V SW

+1.1V SW

ISL6228

+1.1VDUAL@10A

SWITCH

+1.5V

CPU_VDDIO_SUS

+1.1V

SATA HD0,1

SWITCH

+1.1V DUAL

+1.5V@1A

VDDIO_AZ_S 3.3V OR 1.5V

AZ_VDDIO_DUAL

VDDAN_11_PCIE 1.1V 1A

AMD SB800

VDDPL_33_PCIE 3.3V 0.030A

VDDAN_33_USB_S 3.3V 0.2A

VDDAN_11_SATA 1.1V 0.8A

VDDIO_33_S 3.3V

VDDIO_33_PCIGP 3.3V 0.020A

VDDRF_GBE_S

VDDCR_11 1.1V 0.5A

VDDAN_11_USB_S 1.2V 0.2A

+3.3V

VDDIO_18_FC 1.8V 0.050A

+1.1V

+1.8V

BEAD

BEAD

+3.3V

VDDPL_33_SATA 3.3V 0.020A

+1.1V

BEAD

BEAD

+3.3V

VDDAN_11_CLK 1.1V 0.4A

BEAD

+3.3VDUAL

BEAD

+1.1VDUAL

VDDCR_11_USB_S 1.1V

+1.1V

BEAD

+1.1VDUAL

BEAD

+1.1V

VDDIO_33_GBE_S 3.3V

VDDCR_11_GBE_S 1.1V

VDDIO_GBE_S 3.3V

VDDIO_GBE_S/2

+3.3VDUAL

+1.1VDUAL

PHY_VDDIO_DUAL

VDDCR_11_S 1.1V

VDDCD_11_USB 1.1V

VDDPL_11_SYS 1.1 V SYS PLL

VDDPL_33_SYS 3.3V SYS PLL

VDDPL_33_USB_S 3.3 V USB PLL

VDDAN_33_S 3.3V HWM

VDDXL_33_S 3.3V

BEAD

BEAD

BEAD

BEAD

BEAD

BEAD

+3.3VDUAL

+3.3VDUAL

+3.3VDUAL

+3.3VDUAL

+3.3V

+1.1V

+1.1VDUAL

+1.1VDUAL

BATTERY

11.1V 62WHr

BATTERY

CHARGER

ISL6251

CLOCK GEN

3.3V

SWITCH

+3.3V

SWITCH

CPU core

PWM

ISL6265A

CPU_VDDNB_RUN@4A

+5V

+3.3VDUAL

+5VDUAL

CPU_VDDA_RUN +3.3V

VTT_MEM 0.5A

+3.3V

BEAD

AC ADAPTOR

15-16V 90W

HD CODEC

3V

5V

+3.3VALW

CPU_VDDIO_SUS

CPU_VDD_RUN@38A

+VIN

2.5V LDO

DDRiII SODIMMX2--SYSTEM

VDD MEM 4A

MEM_VTT

+5VALW

+5V SW

+3V SW

+5V LDO

+3V LDO

tps51125

+3.3VDUAL@8A

+5VDUAL@8A

CPU core

PWM

ISL6265A

CPU_VDDIO_SUS@9A

DDR3 PWM

LDO VTT

TPS51128&RT9199GSP

MEM_VTT@1.5A

MINI PCIE SLOT0,1,2

+3.3V

BEAD

+5V

BEAD

1.5V (S0, S1) 0.5A

each

3.3V (S3, S5) 2.75A

each

SATA ODD

+1.5V

+3.3VDUAL

5V (S3, S5) TBD

+5V

5V (S0, S1) TBD

+5V

USB X2 FR

5VDual

+5VDUAL

SMSC1100--EC

3.3V 0.5A

AUDIO

OP

+3.3VDUAL

LCD PANEL

3.3V 1.5A

SW

BACK LIGHT

+VDD_MAIN

LED_BL

+VIN

+3.3V

+1.5VDUAL

1.5V LDO

+3.3VDUAL

SWITCH

+3.3VDUAL

S3,S4,S5

+3.3VDUAL

BEAD

VDDC PWM

TPS51128

VDDC@15A

SWITCH

MVDDQ

SWITCH

+3VRUN

SWITCH

1.8V_REG 1.5A

SWITCH

CPU_VDDIO_SUS +1.5V 4A

+3.3VDUAL

CPU_VDDIO_SUS 1.1V_1.0V_PWR

+3.3VDUAL

AMD SB800

PARK_XT_S3

1.8V_REG

+3VRUN

MVDDQ

VDDC

1.1V_1.0V_PWR

2.6A

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

3

BM5016

POWER DELIVERY CHART

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

3

BM5016

POWER DELIVERY CHART

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

3

BM5016

POWER DELIVERY CHART

1.0

http://pc-120.taobao.com/

http://pc-120.taobao.com/

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

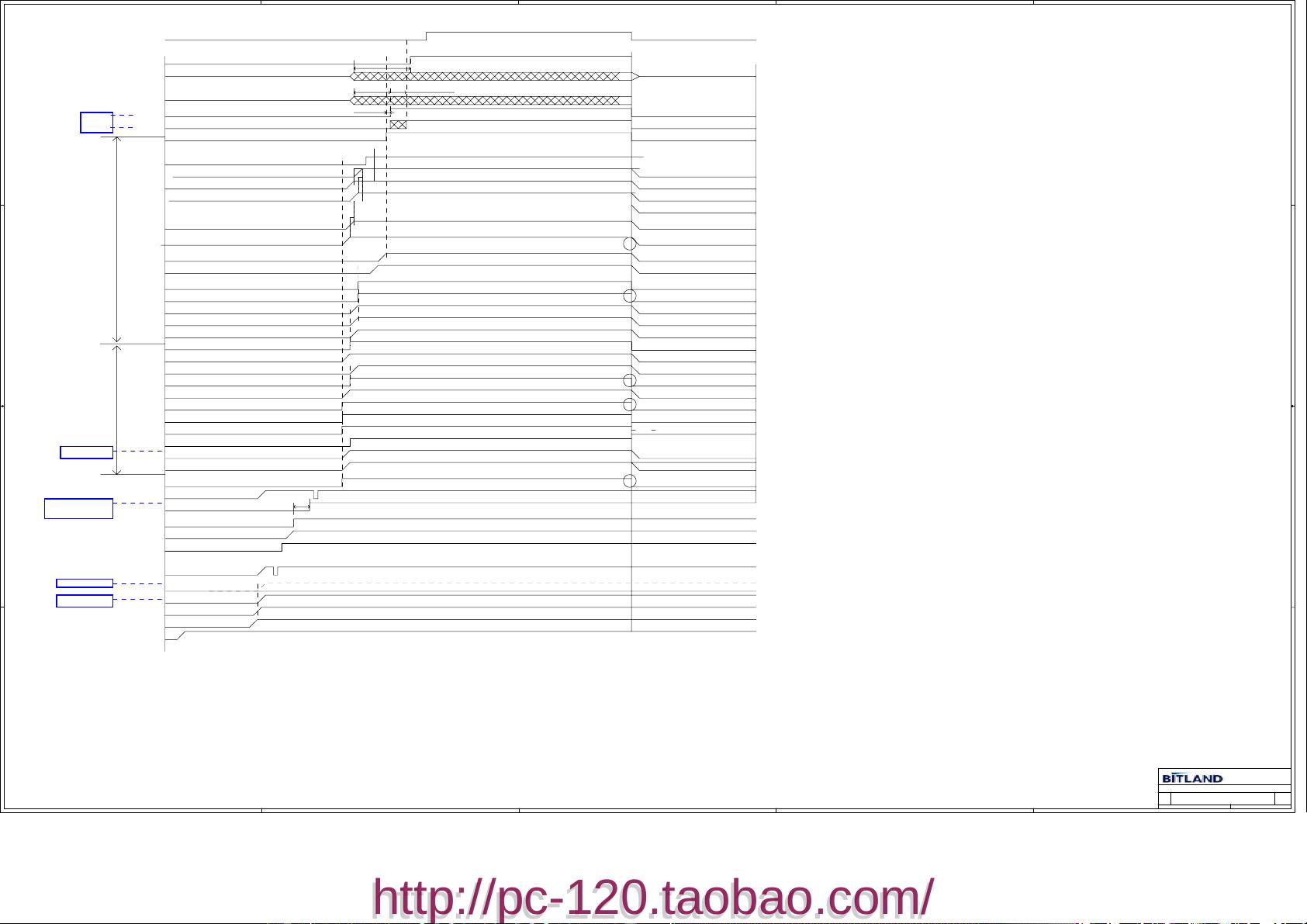

+1.5V

DUAL RAILS

RSMRST#

delay

Battery inserted/AC IN

GROUP A GROUP B

1)+1.5V SWITCH TO +1.5VDUAL 2)LASSO_PWRON 3)LPCPD# for TPM 4) TO SB&KBCSB_PWRGD

>1 mS

Req.

+5V/+3.3V

+1.8V

CPU_VDDIO_SUS

MEM_VTT

MEM_VREF

SLP_S3#

(CPU_VDDA_2.5_RUN)

VDDA_PWRGD

CPU_VDD_RUN

VRM_PWRGD

CPU_VDDNB_RUN

CPU_VDDR

CPU_CLKP/N running

CPU_LDT_RST#

CPU_PWROK

to S3

A_VBAT

+VIN/+12V_HD

+5VALW/+3.3VALW

AC_OK

(ACIN detect)

AC not present scenario = LOW AC present= high

20mS

SLP_S5#

+5VDUAL/+3.3VDUAL/+1.5VDUAL/+1.1VDUAL

When IMC, always on at all time( always PWR)

Power button pressed

+1.1V

VCC_NB

VLDT

Power button pressed

KBC is powered by

A_VBAT & +3.3VALW

LDO:5.4V

(from DCIN)

KBC is ready

VDD_DUAL_EN

CPU_THM/SB/SB_SCL1/2

SB_KB/SPI/LPC ROM PWRS

V3V5DUAL_PWRGD

1V1DUAL_PWRGD

SYSTEM_DUAL_PG_DELAY

PWR_BTN#_EC

Power button from EC to SB

VTT only will be shut down in S3 mode, and VTT for DDR3 SODIMM only.

VDRAM_PWRGD

5V/3.3V_GATE

+2.5V_LDO

CPU MEM CTL &

DDR3 SODIMM PWRS

RC=0

RC=0

RC=0

RC=~4.7ms

RC=~22ms

+1.2V_PWRGD

RC=0

1V8_PWRGD

VRM_PWRGD AND 1V8_PWRGD

VCC_NB should not ramp before 1.1v

1V5_PWRGD/DNI

+1.2V_PWRGD

SLP_S3#

SYS_RST#

KBC_GPIO77/DNI

1V1DUAL_PWRGD

Power on Sequence required:

SB800:

1, +3.3VDUAL ramp before +1.1VDUAL

2, +3.3V ramp before +1.8v

3, +1.8V ramp before +1.1v

4, +3.3v ramp before +1.1v

5, +3.3VALW_R ramping down time > 300us

6, 50uS <= All power rails except +3.3VALW_R <= 40mS

7, 100uS <= +3.3VALW_R <= 40mS

RS880:

1, 0 <(+3.3V) - (+1.8v) < 2.1

2, +1.8V ramp before +1.1v

3. +1.1V ramp before VCC_NB

NB_PWRGD

NB_PWRGD_IN

SB OUTPUT

SB INPUT

(SB TO CPU)

(SB TO CPU)

running

>1 mS Req.

>1 mS Req.

VCC_NB(all NB power) valid before NB_PWRGD.

MVDDQ

PCIE_REFCLKP/N

1.1V_1.0V_PWR

RC=~ms

RC=~ms

RC=~ms

RC=~ms

PARK-XT_PGOOD

VDDC

1.8V_REG

T1>=0

T2>0

T3>0

VDD_CT

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

D

4

BM5016

POWER SEQUENCE CHART

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

D

4

BM5016

POWER SEQUENCE CHART

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

D

4

BM5016

POWER SEQUENCE CHART

1.0

http://pc-120.taobao.com/

http://pc-120.taobao.com/

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

CPU_CLKP/N

PARK_XT

PARK_XT

PCIE_REFCLKP/N

A-LINK

A-LINK

PCIE_RCLKP/N

FOR SATA

EXT CLK MODE

FOR MASTER FOR RTC FOR SATA

PCIE_RCLKP/N

SATA_X1

SATA_X2

25M_X1

25M_X2

DNI

PORT2:WLAN

MINIPCIE SLOT (SB800, 1 LANE)

PORT2:WIFI

SB_PCIE_PE2_CLKREQ#

MINIPCIE SLOT (SB800, 1 LANE)

JMC261

PCIE GPP I/F (RS880M, 1 LANE)

PCIE GPP I/F (RS880M, 1 LANE)

JMC261

HT_REFCLKP/N

GPPSB_REFCLK 100M DIFF

100M DIFF(IN/OUT)*

HT_REFCLKP

RS880M

NB CLOCK INPUT TABLE

NC or 100M DIFF OUTPUT

* RS880M can be used as clock buffer to output two PCIE referecence clocks

By deault, chip will configured as input mode, BIOS can program it to output mode.

100M DIFF

100M DIFF

14M SE (1.1V)

NB CLOCKS

vref

HT_REFCLKN

REFCLK_P

REFCLK_N

GFX_REFCLK

GPP_REFCLK

GPP_REFCLK

GPP_REFCLK

SB_OSC

DNI

CPU_HT_CLKP/N

NB_DISP_CLKP/N

REFCLKP/N

NB_REFCLK_P/N

100MHZ

CPU_CLKP/N

NB_HT_CLKP/N

SLT_GFX_CLKP/N

GPP_CLK2P/N

GPP_CLK3P/N

LPCCLK0

LPCCLK1

LPCCLK0

LPCCLK1

RTCCLK

RTCCLK

PCICLK0

PCICLK1

PCICLK2

PCICLK3

FOR DEBUG PORT

PCI_CLK4

33MHZ

PCICLK4

STRAPS SETTING,

PCIE GEN1/PCIE GEN2

STRAPS

SETTING,

UNUSED

CLOCKS

SPI ROM & HEADER

SPI_CLK

xxHZ

SPI_CLK

AZ_BITCLK

25M Hz

SMSC_CLK

33MHZ

PCI_CLK2

33MHZ

PCI_CLK3

33MHZ

FOR DEBUG PORT

LPC_CLK0

SMSC_CLK

33MHZ

EC/STRAPS SETTING :EC ENABLE

33MHZ

STRAPS SETTING,

CLOCKS ENABLE

LPC_CLK1

33MHZ

PCI_CLK0

33MHZ

48MHZ

PCICLK1

STRAPS SETTING,

UNUSED CLOCKS

PCICLK2

PCICLK3

PCICLK4

CLK_48M_USB

PCI_CLK4

PCI_CLK2

PCI_CLK3

100MHZ

33MHZ

NC

SPI ROM & HEADER

SPI_CLK

xxHZ

SPI_CLK

GBE_RXCLK

GBE_TXCLK

PCI_CLK0

100MHZ

PCIE GFX PARK_XT(RS880M, 16 LANES)

AZ_BIT_CLK

SIG4 CPU

AZ_BITCLK

LPC_CLK0

EC/STRAPS SETTING :EC ENABLE

A_SODIMM

USBCLK

33MHZ

LPC_CLK1

33MHZ

SB_NBLINK_RCLKP/N

100MHZ

AMD

CLOCK GENERATOR

AMD SB820M

HD AUDIO

AZ_BIT_CLK

24MHZ

32.768K Hz

B_SODIMM

SPM_CLK

SIDE PORT MEMORY CHIP

xxxMHZ

MEM_MA_CLK1_P/N

MEM_MA_CLK2_P/N

MEM_MB_CLK1_P/N

MEM_MB_CLK2_P/N

CLK_REQ3 in SB

CLK_REQ2 in SB

SB_MXM_CLKREQ#

CLK_REQ in CLK GEN

100MHZ

PCIE_LAN_CLKP/N

100MHZ

25M Hz

RS880M

RS880M

AMD NORTHBRIDGE

NB_GFX_REFCLKP/N

100MHZ

GPP REF_CLK

100MHZ

HT_REFCLKP/N

100MHZ

NB_OSC

EXT_PCIE_PE2_CLKREQ#

EXT_PCIE_LAN_CLKREQ#

PCICLK0

14.318MHZ

100MHZ

PCIE GFX PARK_XT(RS880M, 16 LANES)

EXT_PCIE_PE2_CLKREQ#

PCIE_REFCLKP/N

25M Hz

SIG4 CPU

200MHZ

A_SODIMM

EXTERNAL CLOCK MODE

INTERNAL CLOCK MODE

NBLINK_RCLKP/N

100MHZ

100MHZ

AMD

AMD NORTHBRIDGE

CLOCK GENERATOR

EXTERNAL

AMD SB800

200MHZ

HD AUDIO

24MHZ

25M Hz

32.768K Hz

14.31818MHz

SBSRC_CLKP/N

B_SODIMM

PCIE_PE2_CLKP/N

100MHZ

PCIE_LAN_CLKP/N

100MHZ

DNI

STRAPS SETTING,

CLOCKS ENABLE

STRAPS SETTING,

PCIE GEN1/PCIE GEN2

27M Hz

25M Hz

27M Hz

25M Hz

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

5

BM5016

CLOCK DISTRIBUTION

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

5

BM5016

CLOCK DISTRIBUTION

1.0

Bitland Information Techonogy Co.,Ltd.

Notebook R&D Division

Title

Size

Date:

Rev

Sheet of

Document Number

Thursday, August 05, 2010 54

Custom

5

BM5016

CLOCK DISTRIBUTION

1.0

http://pc-120.taobao.com/

http://pc-120.taobao.com/

剩余53页未读,继续阅读

资源评论

JOZECN

- 粉丝: 746

- 资源: 2381

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 微软常用运行库 游戏运行库 VC++各个版本

- 微信小程序开发教程.pptx

- MyBatis动态SQL是一种强大的特性,它允许我们在SQL语句中根据条件动态地添加或删除某些部分,从而实现更加灵活和高效的数据

- 锐捷网络认证中心网络管理.pdf

- MyBatis动态SQL是一种强大的特性,它允许我们在SQL语句中根据条件动态地添加或删除某些部分,从而实现更加灵活和高效的数据

- SD8233LF是一款用于单按键触摸及接近感应开关,其用途是替代传统的机械型开关芯片IC

- 基于YOLOv5的烟雾火焰检测算法研究

- 基于STM32的联合调试侦听设备解决方案原理图PCB源文件调试工具视频(大赛作品)

- MyBatis动态SQL是一种强大的特性,它允许我们在SQL语句中根据条件动态地添加或删除某些部分,从而实现更加灵活和高效的数据

- MyBatis动态SQL是一种强大的特性,它允许我们在SQL语句中根据条件动态地添加或删除某些部分,从而实现更加灵活和高效的数据

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功