没有合适的资源?快使用搜索试试~ 我知道了~

Dell Inspiron 1521 (Quanta FX5).pdf

需积分: 5 0 下载量 144 浏览量

2023-12-28

15:37:35

上传

评论

收藏 1.56MB PDF 举报

温馨提示

试读

50页

Dell Inspiron 1521 (Quanta FX5).pdf

资源推荐

资源详情

资源评论

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

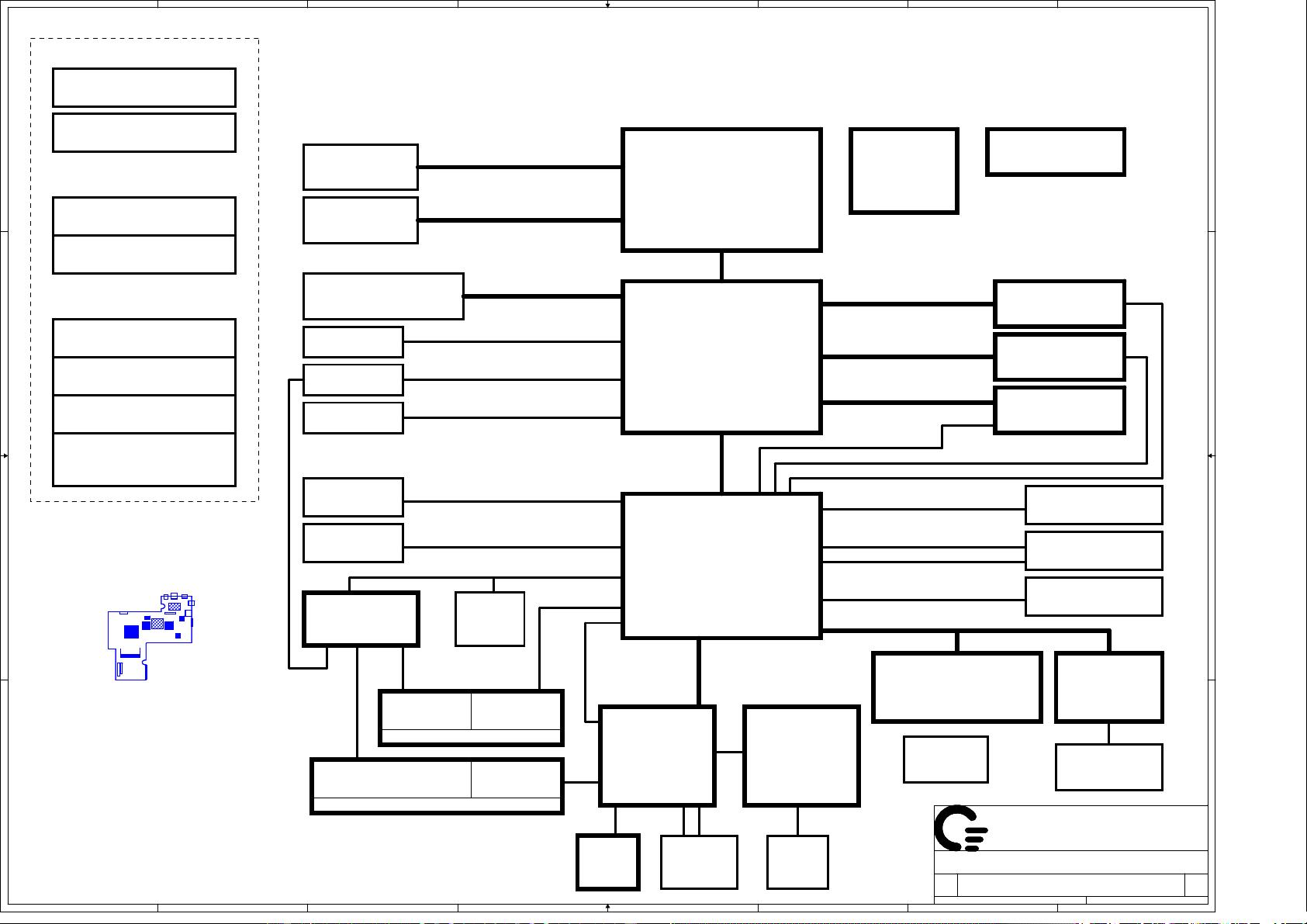

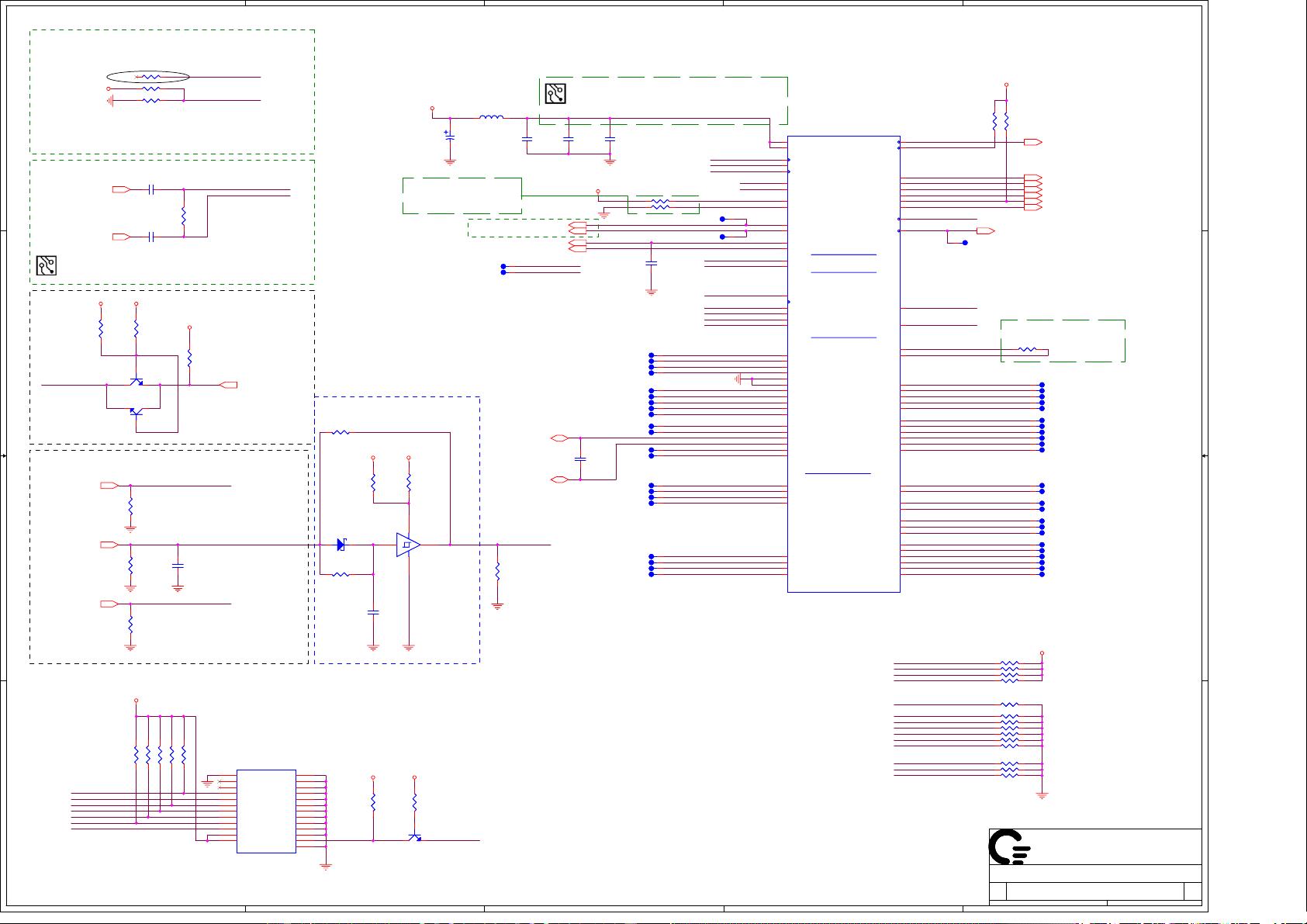

Schematic Block Diagram1

161Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

Schematic Block Diagram1

161Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

Schematic Block Diagram1

161Friday, May 04, 2007

PG 31

MDC

PG 27

SATA

IHDA

CLOCK

PG 18

AUDIO/AMP

PG 33,34

DDR2-SODIMM1

DDR2-SODIMM2

PG 20

CRT CONN.

S/PDIF

PG32

Panel CONN.

LVDS

PG 19

667/800 MHZ DDR II

667/800 MHZ DDR II

TVOUT

VGA

PG 7,8

PG 7,8

USB2.0 (P0,P1)

USB2.0 (P2,P3)

External USBX4

PG 28

SPI PS/2

Touchpad/

Keyboard

CIR

PG 29

LPC

128 Pins VTQFP

PG 32

REV : A00

PG 24

SATA - HDD

IDE

SIO

128 Pins VTQFP

SIO

PG 30

(EXT SIDE)

(EXT BACK)

MEC5025

128KB Flash

TMKBC

ECE5021

BC

SLG84605TTR

USER

INTERFACE

PG 38

EMC4001

FAN & THERMAL

PG 35

FX5 SAPPORO-INTEGRATED

R5C833

EXPRESS-CARD

MINI-CARD x2

PG 25

1394

8-in-1 Card Reader

PG 21,22,23

WLAN & WPAN

33MHz PCI

FLASH

PG 27

R5538

PG 24

BC

Audio Jacks

RJ45/Magnetics

BCM 4401

PG 36

PG 37

TVout CONN.

PG 20

Turion 64 Rev.F Dual-Core/

(638 S1g1 socket)

Dual-Core 35W

AMD S1

465 FCBGA

RS690T

HT_LINK

SB600

549 BGA

A_LINK

MINI-CARD

PG 26

WWAN

PCIEx1

PCIEx1

PCIEx2

USB2.0 (P6)

USB2.0 (P4)

USB2.0 (P9)

REGULATOR

PG 43

+1.8V_SUS/+0.9V_DDR_VTT

+1.5V_RUN

RUN POWER SW

PG 46

DC/DC

AC/BATT

CONNECTOR

BATT

CHARGER

PG 41

PG 40

PG 45

CPU VR

PG 44

REGULATOR

PG 39

SYSTEM

RESET CIRCUIT

PG 42

+3.3V_SUS/+5V_SUS/+15V_SUS

POWER

VCC_NB & +1.2V_ALW_SUS

PG 9,10,11,12,13

PG 14,15,16,17

PG 3,4,5,6

CD-ROM

USB2.0 (P5)

External USB

PG 28

PG 13

400 MHZ DDR II

DDR2-MEMORY DEVICE

8MX16X4 84-PIN FBGA

USB2.0 (P8) (GX2)

Camera

SNIFFER

PG 34

PG 34

Digital MIC

SPI

(B0)

PG 38

BlueTooth

USB2.0 (P7)

FX5 M/B PCBFX5 M/B PCB

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

A A

B B

C C

D D

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

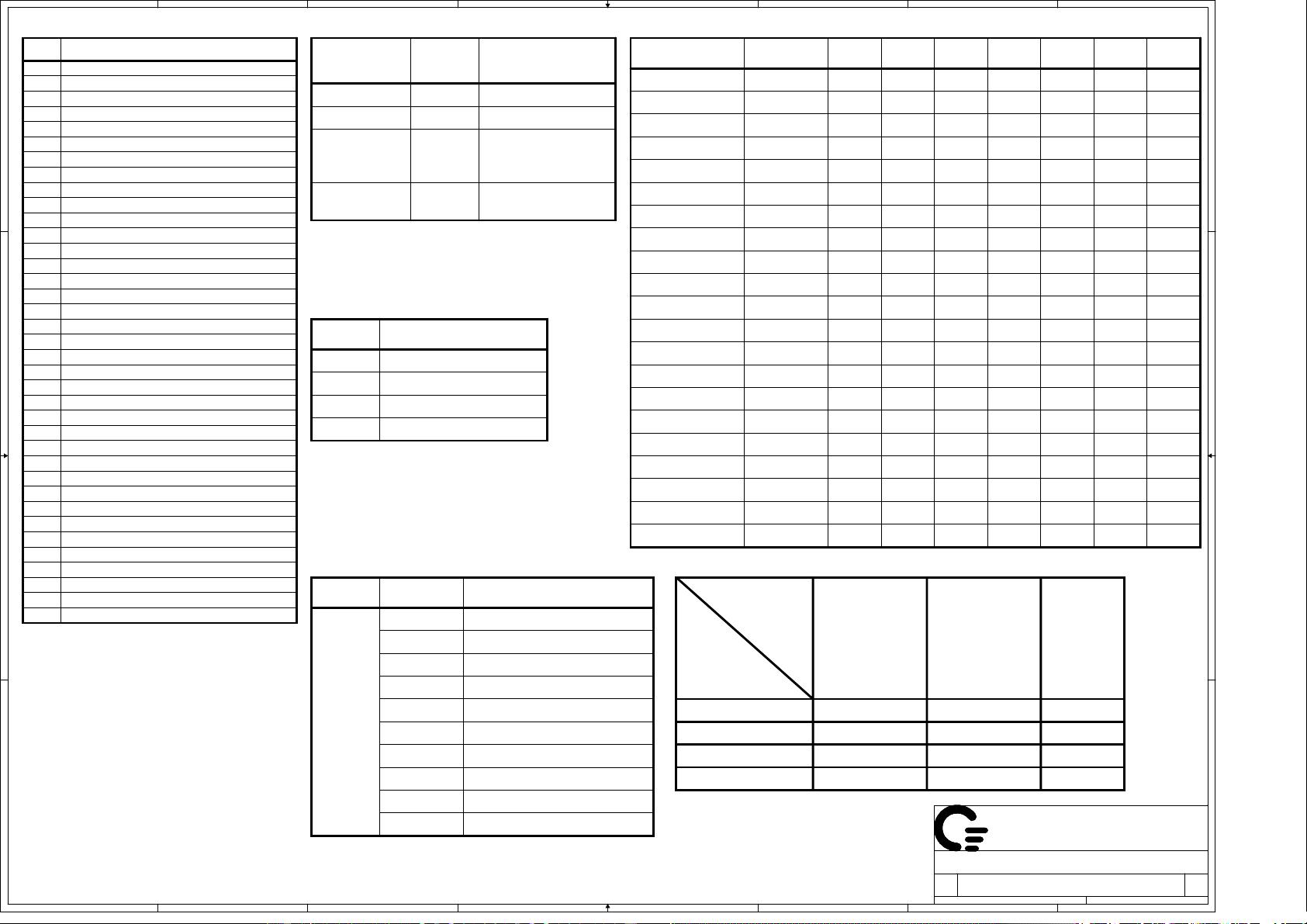

Index, DNI, Power & Ground

261Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

Index, DNI, Power & Ground

261Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

Index, DNI, Power & Ground

261Friday, May 04, 2007

Control

Signal

+3.3V_SUS

SIO (ECE5011)

S0/M0

S3/M1 S4/M1

S3/

M-off

S4/

M-off

S5/

M-off

36

+1.2V_ALW_SUS,+NB_VCORE

45

46

48

EMI CAP & SCREW HOLE

+5V_RUN

49

MINI-PCI

+1.8V_SUS,+0.9V_DDR_VTT,+1.5V_RUN

Audio CODEC(STAC9205)&

LAN (BCM4401)

37

Schematic Block Diagram

Turion 64

RS690T

14-17

7-8

DDRII SO-DIMMX2

Clock Generator

LCD Conn. & CK-SSCD

8-IN-1 CARD READER

FLASH,RTC&KC

TP&CIR

AUDIO CONN Digital MIC/Camera

LAN JACK

DCIN,BATT CONNECTOR

System Reset Circuit

SIO (MEC5025)

39

Charger

40

41

42

43

44

50

SMBUS BLOCK

+VCC_VCRE

CRT&TV CONN

51

VHCORE(MAX8774)

+3.3V_ALW,+5V_ALW

RUN Power Switch

POWER BLOCK

Chipset Power Block

33

+5V_SUS

38

SWITCH&LED

3-6

+LCDVCC

9-13

18

20

19

21-23

+1.2V_RUN

+2.5V_RUN

+NB_VCORE

+1.2V_ALW_SUS

+15V_ALW

+3.3V_WLAN

+3.3V_RUN

USB

WWAN

SATA (HDD&CD_ROM)

Express Card & Smart Card

27

24

25

FAN & Thermal

26

28

Front Page

29

30

31

32

34

35

+1.8V_SUS

Pg# Description

1

2

+3.3V_LAN

+0.9V_DDR_VTT

SB600

+1.8V_RUN

INDEX Power States

Power Rail S3/M1

+3.3V_ALW

+5V_ALW

PCI-E

Lane0

Lane1

Lane2

Lane3

MINI CARD-3 WWAN

Destination (S/Y)

MINI CARD-1 WLAN

MINI CARD-2 WPAN

EXPRESS CARD

Power

Plan

+15V_ALW

+5V_ALW

+3.3V_ALW

+1.2V_ALW_SUS

State

+5V_SUS

+3.3V_SUS

+1.8V_SUS

+0.9V_DDR_VTT

+5V_RUN

+3.3V_RUN

+2.5V_RUN

+1.8V_RUN

+1.5V_RUN

+1.2V_RUN

+VCC_CORE

+NB_CORE

S0

S3

S5 S4/AC

S5 S4 on battery

ON

ON

ON

ON

ON ON

OFF

OFF

OFF OFF

OFF

OFF

PCI Device

Cardbus (OZ601)

Docking

MediaCard & 1394

(R5C832)

LOM (4401)

AD17

AD24

AD17

AD16

IDSEL

REQ# / GNT# -

PIRQ (S/Y)

N/A

N/A

REQ1# / GNT#1 -

PIRQC# (Media Card),

PIRQD# (1394) & SERIRQ.

REQ0# / GNT#0 -

PIRQB#.

PM Table

IC Chips

SB600

3

Right side Pair Top as viewed in the front

USB Port# Destination (S/Y)

0

4

5

6

7

8

9

1

2

Right side Pair Bot. as viewed in the front

Rear Side Top

Rear Side Bottom

Left side Pair Tot as viewed in the front

Camera

Express Card

3rd Mini Card USB(WPAN)

Left side Pair Bot. as viewed in the front

WWAN

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

HT_CTLOUT1HT_CTLIN1

HT_CTLOUT#1HT_CTLIN#1

HT_CADIN09

HT_CADIN29

HT_CADIN#139

HT_CADIN#79

HT_CADIN89

HT_CADIN#119

HT_CADIN#159

HT_CADIN39

HT_CADIN149

HT_CADIN#129

HT_CADIN69

HT_CADIN#69

HT_CADIN159

HT_CADIN#29

HT_CADIN#109

HT_CADIN#59

HT_CADIN79

HT_CADIN119

HT_CADIN#99

HT_CADIN#39

HT_CADIN#49

HT_CADIN49

HT_CADIN#89

HT_CADIN19

HT_CADIN99

HT_CADIN#19

HT_CADIN109

HT_CADIN129

HT_CADIN#149

HT_CADIN59

HT_CADIN#09

HT_CADIN139

HT_CADOUT14 9

HT_CADOUT#1 9

HT_CADOUT#10 9

HT_CADOUT13 9

HT_CADOUT3 9

HT_CADOUT2 9

HT_CADOUT#14 9

HT_CADOUT#13 9

HT_CADOUT#5 9

HT_CADOUT0 9

HT_CADOUT#12 9

HT_CADOUT#8 9

HT_CADOUT5 9

HT_CADOUT11 9

HT_CADOUT#15 9

HT_CADOUT15 9

HT_CADOUT#2 9

HT_CADOUT#3 9

HT_CADOUT#0 9

HT_CADOUT#7 9

HT_CADOUT12 9

HT_CADOUT7 9

HT_CADOUT#6 9

HT_CADOUT9 9

HT_CADOUT4 9

HT_CADOUT#11 9

HT_CADOUT#4 9

HT_CADOUT1 9

HT_CADOUT#9 9

HT_CADOUT6 9

HT_CADOUT8 9

HT_CADOUT10 9

HT_CLKOUT1 9

HT_CLKOUT#0 9

HT_CLKOUT#1 9

HT_CLKOUT0 9

HT_CLKIN19

HT_CLKIN09

HT_CLKIN#09

HT_CLKIN#19

HT_CTLIN#09

HT_CTLIN09

HT_CTLOUT0 9

HT_CTLOUT#0 9

+1.2V_RUN

+1.2V_RUN

+1.2V_RUN

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

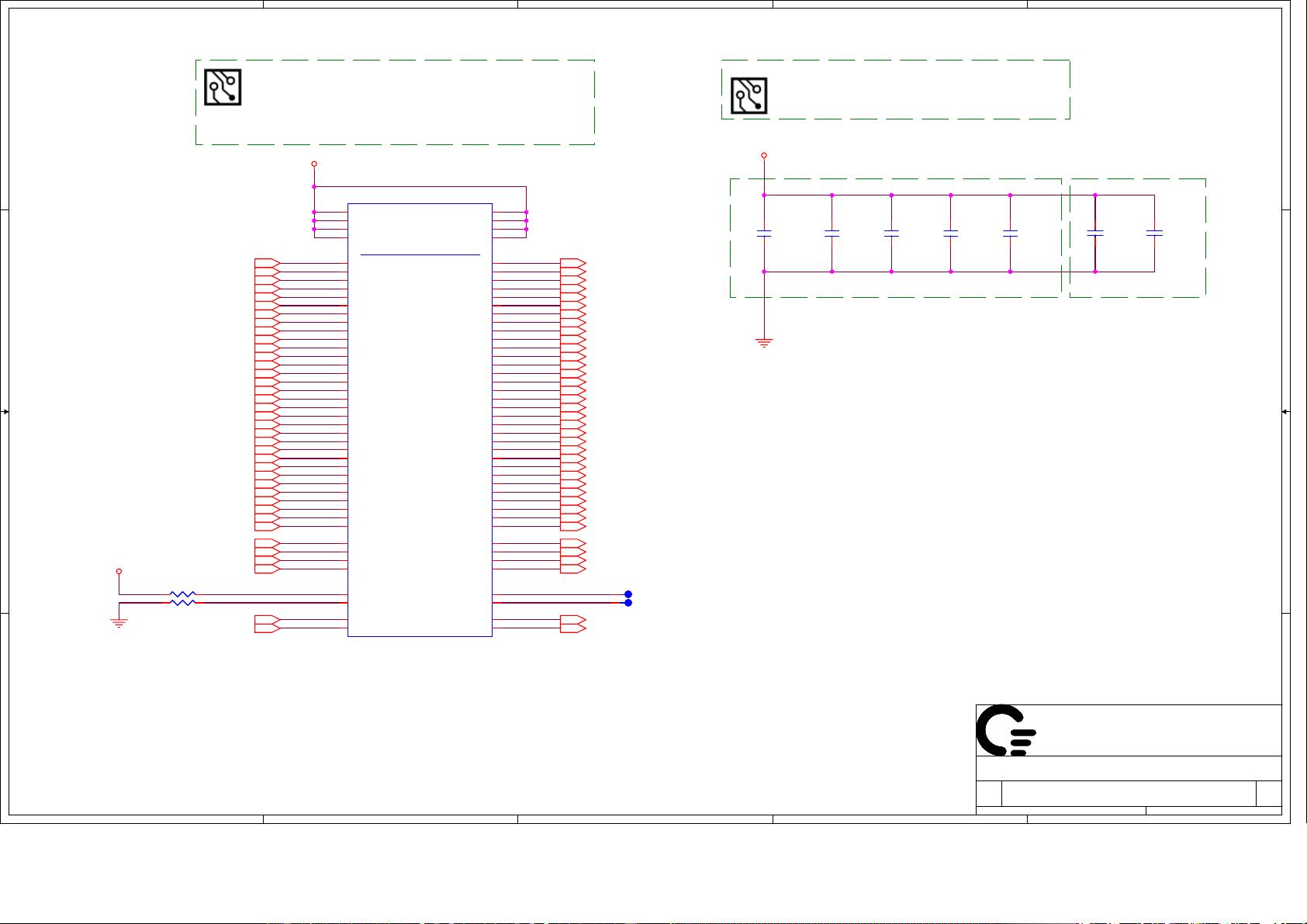

ATHLON64 HT I/F

361Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 HT I/F

361Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 HT I/F

361Friday, May 04, 2007

PROCESSOR HYPERTRANSPORT INTERFACE

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

Athlon 64 S1

Processor Socket

VLDT_Ax AND VLDT_Bx ARE CONNECTED TO THE LDT_RUN POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

PLACE CLOSE TO VLDT0 POWER PINS

TO OTHER HT POWER PINS

LAYOUT: Place bypass cap on topside of board

NEAR HT POWER PINS THAT ARE NOT CONNECTED DIRECTLY

TO DOWNSTREAM HT DEVICE, BUT CONNECTED INTERNALLY

Place T96 and T98 less

than 100mils from CPU

Place R167 and R166 less

than 100mils from CPU

X5R NPO

R167 51R167 51

C565

4.7U/6.3V/0603

C565

4.7U/6.3V/0603

C589

0.22U/6.3V

C589

0.22U/6.3V

C572

180P/50V

C572

180P/50V

12

C155

4.7U/6.3V/0603

C155

4.7U/6.3V/0603

T98T98

T96T96

C562

180P/50V

C562

180P/50V

12

R166

51

R166

51

C566

4.7U/6.3V/0603

C566

4.7U/6.3V/0603

C578

0.22U/6.3V

C578

0.22U/6.3V

U18AU18A

VLDT_A3

D4

VLDT_A2

D3

VLDT_A1

D2

VLDT_A0

D1

VLDT_B3

AE5

VLDT_B2

AE4

VLDT_B1

AE3

VLDT_B0

AE2

L0_CADIN_H15

N5

L0_CADIN_L15

P5

L0_CADIN_H14

M3

L0_CADIN_L14

M4

L0_CADIN_H13

L5

L0_CADIN_L13

M5

L0_CADIN_H12

K3

L0_CADIN_L12

K4

L0_CADIN_H11

H3

L0_CADIN_L11

H4

L0_CADIN_H10

G5

L0_CADIN_L10

H5

L0_CADIN_H9

F3

L0_CADIN_L9

F4

L0_CADIN_H8

E5

L0_CADIN_L8

F5

L0_CADIN_H7

N3

L0_CADIN_L7

N2

L0_CADIN_H6

L1

L0_CADIN_L6

M1

L0_CADIN_H5

L3

L0_CADIN_L5

L2

L0_CADIN_H4

J1

L0_CADIN_L4

K1

L0_CADIN_H3

G1

L0_CADIN_L3

H1

L0_CADIN_H2

G3

L0_CADIN_L2

G2

L0_CADIN_H1

E1

L0_CADIN_L1

F1

L0_CADIN_H0

E3

L0_CADIN_L0

E2

L0_CADOUT_H15

T4

L0_CADOUT_L15

T3

L0_CADOUT_H14

V5

L0_CADOUT_L14

U5

L0_CADOUT_H13

V4

L0_CADOUT_L13

V3

L0_CADOUT_H12

Y5

L0_CADOUT_L12

W5

L0_CADOUT_H11

AB5

L0_CADOUT_L11

AA5

L0_CADOUT_H10

AB4

L0_CADOUT_L10

AB3

L0_CADOUT_H9

AD5

L0_CADOUT_L9

AC5

L0_CADOUT_H8

AD4

L0_CADOUT_L8

AD3

L0_CADOUT_H7

T1

L0_CADOUT_L7

R1

L0_CADOUT_H6

U2

L0_CADOUT_L6

U3

L0_CADOUT_H5

V1

L0_CADOUT_L5

U1

L0_CADOUT_H4

W2

L0_CADOUT_L4

W3

L0_CADOUT_H3

AA2

L0_CADOUT_L3

AA3

L0_CADOUT_H2

AB1

L0_CADOUT_L2

AA1

L0_CADOUT_H1

AC2

L0_CADOUT_L1

AC3

L0_CADOUT_H0

AD1

L0_CADOUT_L0

AC1

L0_CLKIN_H1

J5

L0_CLKIN_L1

K5

L0_CLKIN_H0

J3

L0_CLKIN_L0

J2

L0_CTLIN_H0

N1

L0_CTLIN_L0

P1

L0_CTLOUT_H0

R2

L0_CTLOUT_L0

R3

L0_CLKOUT_H0

Y1

L0_CLKOUT_L0

W1

L0_CLKOUT_H1

Y4

L0_CLKOUT_L1

Y3

L0_CTLIN_H1

P3

L0_CTLIN_L1

P4

L0_CTLOUT_H1

T5

L0_CTLOUT_L1

R5

A

A

B

B

C

C

D

D

E

E

4 4

3 3

2 2

1 1

DDR_A_MA14

DDR_A_MA15

DDR_A_MA12

DDR_A_MA13

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_B_MA1

DDR_B_MA10

DDR_B_MA4

DDR_B_MA7

DDR_B_MA3

DDR_B_MA2

DDR_B_MA6

DDR_B_MA13

DDR_B_MA0

DDR_B_MA8

DDR_B_MA9

DDR_B_MA11

DDR_B_MA5

DDR_B_MA12

DDR_B_MA14

DDR_B_MA15

M_ZP

M_ZN

DDR_A_D48

DDR_A_D13

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D8

DDR_A_D14

DDR_A_D15

DDR_B_D16

DDR_B_D21

DDR_B_D23

DDR_B_D20

DDR_B_D22

DDR_B_D19

DDR_B_D18

DDR_B_D17

DDR_B_D3

DDR_B_D1

DDR_B_D2

DDR_B_D0

DDR_B_D6

DDR_B_D5

DDR_B_D7

DDR_B_D4

DDR_B_D9

DDR_B_D11

DDR_B_D12

DDR_B_D8

DDR_B_D10

DDR_B_D14

DDR_B_D13

DDR_B_D15

DDR_A_DQS#0

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#7

DDR_A_DQS#6

DDR_A_DQS0

DDR_A_DQS4

DDR_A_DQS1

DDR_A_DQS3

DDR_A_DQS2

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS5

DDR_A_D29

DDR_A_D28

DDR_A_D31

DDR_A_D27

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D30

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D57

DDR_A_D60

DDR_A_D58

DDR_A_D59

DDR_A_D56

DDR_A_D61

DDR_A_D62

DDR_A_D63

DDR_B_DQS#0

DDR_B_DQS#6

DDR_B_DQS#3

DDR_B_DQS#1

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#2

DDR_B_DQS#7

DDR_B_DQS5

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS7

DDR_B_DQS2

DDR_B_DQS6

DDR_B_DQS0

DDR_B_DM5

DDR_B_DM0

DDR_B_DM4

DDR_B_DM3

DDR_B_D25

DDR_B_D24

DDR_B_D27

DDR_B_D31

DDR_B_D30

DDR_B_D28

DDR_B_D26

DDR_B_D32

DDR_B_D29

DDR_A_DM0

DDR_A_DM3

DDR_A_DM1

DDR_A_DM4

DDR_A_DM2

DDR_A_DM7

DDR_A_DM6

DDR_A_DM5

DDR_A_D49

DDR_A_D55

DDR_A_D50

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D51

DDR_B_DQS1

DDR_A_D1

DDR_A_D0

DDR_A_D2

DDR_A_D7

DDR_A_D5

DDR_A_D4

DDR_A_D3

DDR_A_D6

DDR_B_DM6

DDR_B_DM7

DDR_B_DM2

DDR_B_DM1

DDR_A_D17

DDR_A_D21

DDR_A_D22

DDR_A_D19

DDR_A_D20

DDR_A_D16

DDR_A_D18

DDR_A_D23

DDR_B_D37

DDR_B_D36

DDR_B_D35

DDR_B_D33

DDR_B_D34

DDR_B_D41

DDR_B_D38

DDR_B_D40

DDR_B_D39

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_B_D44

DDR_B_D46

DDR_B_DQS#0

DDR_B_DQS#6

DDR_B_DQS#3

DDR_B_DQS#1

DDR_B_D47

DDR_B_D45

DDR_B_D42

DDR_B_D49

DDR_B_D43

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#2

DDR_B_DQS#7

DDR_B_DQS5

DDR_B_DQS3

DDR_B_D52

DDR_B_D56

DDR_B_D48

DDR_B_D53

DDR_B_D51

DDR_B_D63

DDR_B_DQS4

DDR_B_DQS7

DDR_B_DQS2

DDR_B_DQS6

DDR_B_DQS0

DDR_B_D58

DDR_B_D54

DDR_B_D50

DDR_B_D61

DDR_B_D55

DDR_B_DQS1

DDR_B_D59

DDR_B_D62

DDR_B_D60

DDR_B_D57

DDR_A_DQS#0

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#7

DDR_A_DQS#6

DDR_A_DQS0

DDR_A_DQS4

DDR_A_DQS1

DDR_A_DQS3

DDR_A_DQS2

DDR_A_DQS6

DDR_A_DQS7

DDR_A_DQS5

+0.9V_CPU_M_VREF_SUS

CPU_VTT_SUS_SENSE

DDR_A_BS27,8

DDR_A_BS07,8

DDR_A_BS17,8

DDR_A_RAS#7,8

DDR_A_WE#7,8

DDR_A_CAS#7,8

DDR_A_MA[0..15]7,8

DDR_B_BS2 7,8

DDR_B_CAS# 7,8

DDR_B_BS0 7,8

DDR_B_BS1 7,8

DDR_B_MA[0..15] 7,8

DDR_B_RAS# 7,8

DDR_B_WE# 7,8

M_CLK_DDR1 7

M_CLK_DDR0 7

M_CLK_DDR#1 7

M_CLK_DDR#0 7

M_CLK_DDR3 7

M_CLK_DDR2 7

M_CLK_DDR#3 7

M_CLK_DDR#2 7

M_ODT3 7,8

M_ODT1 7,8

M_ODT2 7,8

M_ODT0 7,8

DDR_CS3_DIMMA#7,8

DDR_CS2_DIMMA#7,8

DDR_CS1_DIMMA#7,8

DDR_CS0_DIMMA#7,8

DDR_CS0_DIMMB#7,8

DDR_CS1_DIMMB#7,8

DDR_CS2_DIMMB#7,8

DDR_CS3_DIMMB#7,8

DDR_CKE3_DIMMB7,8

DDR_CKE2_DIMMB7,8

DDR_CKE1_DIMMA7,8

DDR_CKE0_DIMMA7,8

CPU_VTT_SUS_SENSE43

+1.8V_SUS

+1.8V_SUS

+0.9V_DDR_VTT

+V_DDR_VREF

DDR_A_D[0..63] 7

DDR_B_DQS#[0..7]7

DDR_B_DQS[0..7]7

DDR_A_DQS#[0..7]7

DDR_A_DQS[0..7]7

DDR_B_D[0..63]7

DDR_B_DM[0..7]7 DDR_A_DM[0..7] 7

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

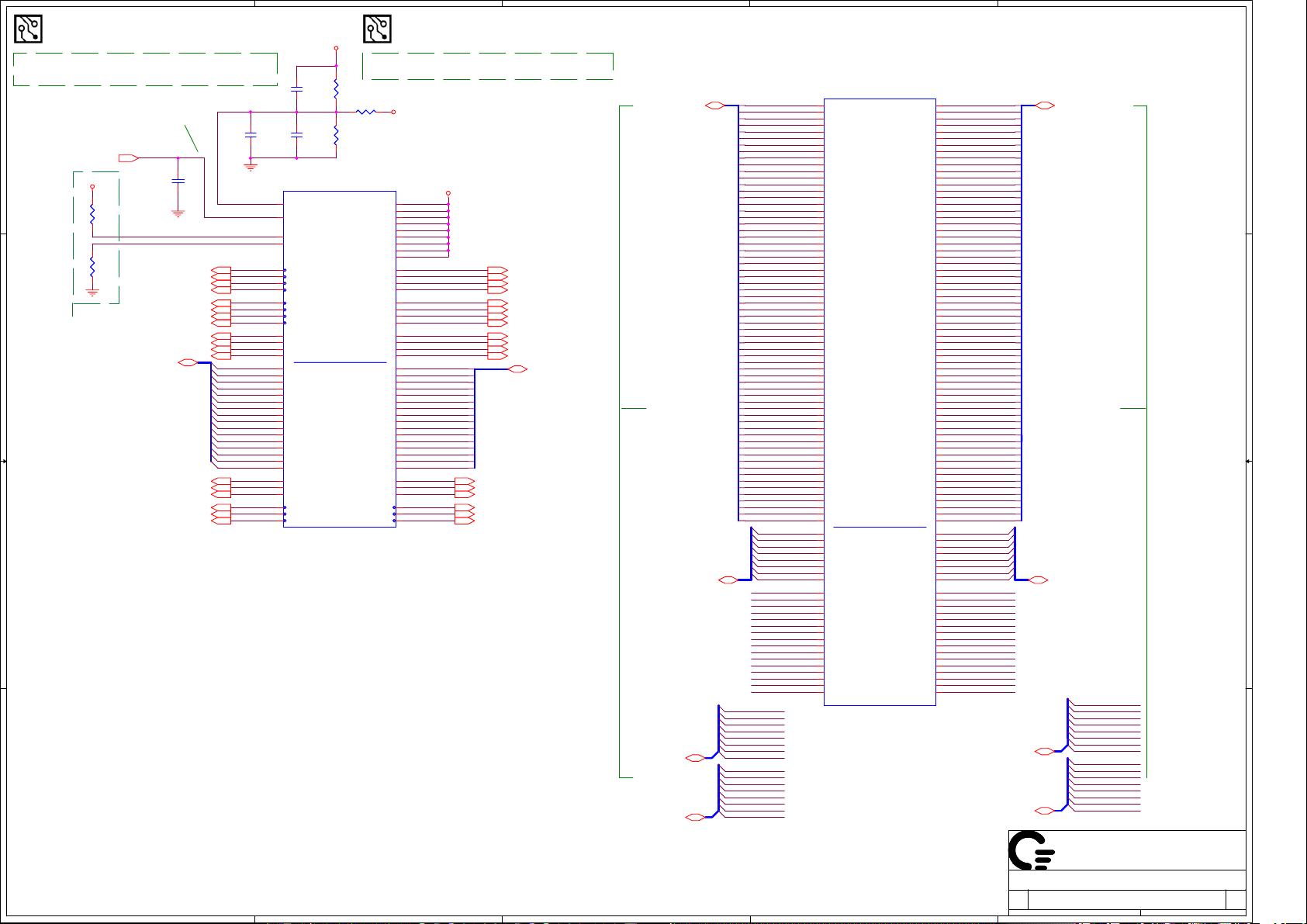

ATHLON64 DDRII MEMORY

461Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 DDRII MEMORY

461Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 DDRII MEMORY

461Friday, May 04, 2007

PLACE THEM CLOSE TO

CPU WITHIN 1"

ON THE BOARD TO DECOUPLING NEAR THE CPU PACKAGE

VDD_VTT_SUS_CPU IS CONNECTED TO THE VDD_VTT_SUS POWER

SUPPLY THROUGH THE PACKAGE OR ON THE DIE. IT IS ONLY CONNECTED

Athlon 64 S1

Processor Socket

Processor DDR2 Memory Interface

Athlon 64 S1

Processor Socket

To SODIMM socket A (near)

To SODIMM socket B (Far)

CPU_VTT_SUS_SENSE

should be routed as 10mils

and 10mils spacing from any

adjacent signals in X, Y, Z

directions.

Place Capacitors for +0.9V_CPU_M_VREF_SUS < 1" from the RS690T.

+0.9V_CPU_M_VREF_SUS trace length < 6", trace width > 15mils and

20mils spacing from any adjacent signals in X, Y, Z directions.

C700

0.1U/10V

C700

0.1U/10V

R578

1K/F

R578

1K/F

R579

1K/F

R579

1K/F

R231

39.2/F

R231

39.2/F

1 2

C694

0.1U/10V

C694

0.1U/10V

R577

*0_0603_NC

R577

*0_0603_NC

1 2

C683

1N/50V

C683

1N/50V

DDR: DATA

U18C

DDR: DATA

U18C

MB_DM7

AD12

MB_DM6

AC16

MB_DM5

AE22

MB_DM4

AB26

MB_DM3

E25

MB_DM2

A22

MB_DM1

B16

MB_DM0

A12

MA_DM7

Y13

MA_DM6

AB16

MA_DM5

Y19

MA_DM4

AC24

MA_DM3

F24

MA_DM2

E19

MA_DM1

C15

MA_DM0

E12

MA_DATA0

G12

MA_DATA1

F12

MA_DATA2

H14

MA_DATA3

G14

MA_DATA4

H11

MA_DATA5

H12

MA_DATA6

C13

MA_DATA7

E13

MA_DATA8

H15

MA_DATA9

E15

MA_DATA10

E17

MA_DATA11

H17

MA_DATA12

E14

MA_DATA13

F14

MA_DATA14

C17

MA_DATA15

G17

MA_DATA16

G18

MA_DATA17

C19

MA_DATA18

D22

MA_DATA19

E20

MA_DATA20

E18

MA_DATA21

F18

MA_DATA22

B22

MA_DATA23

C23

MA_DATA24

F20

MA_DATA25

F22

MA_DATA26

H24

MA_DATA27

J19

MA_DATA28

E21

MA_DATA29

E22

MA_DATA30

H20

MA_DATA31

H22

MA_DATA32

Y24

MA_DATA33

AB24

MA_DATA34

AB22

MA_DATA35

AA21

MA_DATA36

W22

MA_DATA37

W21

MA_DATA38

Y22

MA_DATA39

AA22

MA_DATA40

Y20

MA_DATA41

AA20

MA_DATA42

AA18

MA_DATA43

AB18

MA_DATA44

AB21

MA_DATA45

AD21

MA_DATA46

AD19

MA_DATA47

Y18

MA_DATA48

AD17

MA_DATA49

W16

MA_DATA50

W14

MA_DATA51

Y14

MA_DATA52

Y17

MA_DATA53

AB17

MA_DATA54

AB15

MA_DATA55

AD15

MA_DATA56

AB13

MA_DATA57

AD13

MA_DATA58

Y12

MA_DATA59

W11

MA_DATA60

AB14

MA_DATA61

AA14

MA_DATA62

AB12

MA_DATA63

AA12

MA_DQS_L0

H13

MA_DQS_L1

G15

MA_DQS_L2

C21

MA_DQS_L3

G21

MA_DQS_L4

AC23

MA_DQS_L5

AB20

MA_DQS_L6

W15

MA_DQS_L7

W13

MA_DQS_H0

G13

MA_DQS_H1

G16

MA_DQS_H2

C22

MA_DQS_H3

G22

MA_DQS_H4

AD23

MA_DQS_H5

AB19

MA_DQS_H6

Y15

MA_DQS_H7

W12

MB_DATA0

C11

MB_DATA1

A11

MB_DATA2

A14

MB_DATA3

B14

MB_DATA4

G11

MB_DATA5

E11

MB_DATA6

D12

MB_DATA7

A13

MB_DATA8

A15

MB_DATA9

A16

MB_DATA10

A19

MB_DATA11

A20

MB_DATA12

C14

MB_DATA13

D14

MB_DATA14

C18

MB_DATA15

D18

MB_DATA16

D20

MB_DATA17

A21

MB_DATA18

D24

MB_DATA19

C25

MB_DATA20

B20

MB_DATA21

C20

MB_DATA22

B24

MB_DATA23

C24

MB_DATA24

E23

MB_DATA25

E24

MB_DATA26

G25

MB_DATA27

G26

MB_DATA28

C26

MB_DATA29

D26

MB_DATA30

G23

MB_DATA31

G24

MB_DATA32

AA24

MB_DATA33

AA23

MB_DATA34

AD24

MB_DATA35

AE24

MB_DATA36

AA26

MB_DATA37

AA25

MB_DATA38

AD26

MB_DATA39

AE25

MB_DATA40

AC22

MB_DATA41

AD22

MB_DATA42

AE20

MB_DATA43

AF20

MB_DATA44

AF24

MB_DATA45

AF23

MB_DATA46

AC20

MB_DATA47

AD20

MB_DATA48

AD18

MB_DATA49

AE18

MB_DATA50

AC14

MB_DATA51

AD14

MB_DATA52

AF19

MB_DATA53

AC18

MB_DATA54

AF16

MB_DATA55

AF15

MB_DATA56

AF13

MB_DATA57

AC12

MB_DATA58

AB11

MB_DATA59

Y11

MB_DATA60

AE14

MB_DATA61

AF14

MB_DATA62

AF11

MB_DATA63

AD11

MB_DQS_L0

B12

MB_DQS_L1

C16

MB_DQS_L2

A23

MB_DQS_L3

E26

MB_DQS_L4

AC26

MB_DQS_L5

AF22

MB_DQS_L6

AD16

MB_DQS_L7

AE12

MB_DQS_H0

C12

MB_DQS_H1

D16

MB_DQS_H2

A24

MB_DQS_H3

F26

MB_DQS_H4

AC25

MB_DQS_H5

AF21

MB_DQS_H6

AE16

MB_DQS_H7

AF12

R235

39.2/F

R235

39.2/F

1 2

C647

*470P/50V_NC

C647

*470P/50V_NC

12

U18B

DDR II: CMD/CTRL/CLK

U18B

DDR II: CMD/CTRL/CLK

VTT1

D10

VTT2

C10

VTT3

B10

VTT4

AD10

VTT6

AC10

VTT7

AB10

VTT8

AA10

VTT9

A10

MEMVREF

W17

VTT_SENSE

Y10

MEMZN

AE10

MEMZP

AF10

MA0_CS_L3

V19

MA0_CS_L2

J22

MA0_CS_L1

V22

MA0_CS_L0

T19

MB_CKE1

H26

MB_CKE0

J23

MA_CKE1

J20

MA_CKE0

J21

MA_ADD13

V24

MA_ADD12

K24

MA_ADD11

L20

MA_ADD10

R19

MA_ADD9

L19

MA_ADD8

L22

MA_ADD7

L21

MA_ADD6

M19

MA_ADD5

M20

MA_ADD4

M24

MA_ADD3

M22

MA_ADD2

N22

MA_ADD1

N21

MA_ADD0

R21

MA_BANK1

R20

MA_BANK0

T22

MA_RAS_L

T20

MA_CAS_L

U20

MA_WE_L

U21

MB_RAS_L

U24

MB_CAS_L

V26

MB_WE_L

U22

MB_BANK1

T26

MB_BANK0

U26

MB_ADD13

W25

MB_ADD12

L23

MB_ADD11

L25

MB_ADD10

U25

MB_ADD9

L24

MB_ADD8

M26

MB_ADD7

L26

MB_ADD6

N23

MB_ADD5

N24

MB_ADD4

N25

MB_ADD3

N26

MB_ADD2

P24

MB_ADD1

P26

MB_ADD0

T24

MA0_CLK_H2

Y16

MA0_CLK_L2

AA16

MA0_CLK_H1

E16

MA0_CLK_L1

F16

MB0_CLK_H2

AF18

MB0_CLK_L2

AF17

MB0_CLK_H1

A17

MB0_CLK_L1

A18

MB0_CS_L3

Y26

MB0_CS_L2

J24

MB0_CS_L1

W24

MB0_CS_L0

U23

MA0_ODT0

U19

MA0_ODT1

V20

MA_BANK2

K22

MA_ADD15

K19

MA_ADD14

K20

MB0_ODT0

W26

MB0_ODT1

W23

MB_BANK2

K26

MB_ADD14

J26

MB_ADD15

J25

VTT5

W10

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

LDT_STOP#_R

CPU_PWRGD

LDT_RST#

CPU_HTREF1

CPU_HTREF0

CPU_PRESENT#

CPU_RSVD_MA0_CLK0_P

CPU_RSVD_MB0_CLK3_N

CPU_RSVD_MA0_CLK3_N

CPU_RSVD_MA0_CLK0_N

CPU_RSVD_MB0_CLK3_P

CPU_RSVD_MB0_CLK0_P

CPU_RSVD_MB0_CLK0_N

CPU_RSVD_MA0_CLK3_P

CPU_RSVD_VIDSTRB0

CPU_RSVD_VIDSTRB1

CPU_MA_RESET#

CPU_RSVD_VDDNB_FB_P

CPU_RSVD_VDDNB_FB_N

CPU_MB_RESET#

CPU_RSVD_CORE_TYPE

CPU_TEST10_ANALOGOUT

CPU_TEST28_L_PLLCHRZ_N

CPU_TEST26_BURNIN#

CPU_TEST29_H_FBCLKOUT_P

CPU_TEST08_DIG_T

CPU_TEST28_H_PLLCHRZ_P

CPU_TEST21_SCANEN

CPU_TEST23_TSTUPD

CPU_TEST29_L_FBCLKOUT_N

CPU_TEST25_L_BYPASSCLK_L

H_THERMDA

CPU_TEST17_BP3

H_THERMDC

CPU_TEST3_GATE0

CPU_TEST19_PLLTEST0

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST6_DIECRACKMON

CPU_TEST2_DRAIN0

CPU_TEST16_BP2

CPU_TEST18_PLLTEST1

CPU_TEST07_ANALOG_T

+2.5V_CPU_VDDA_RUN

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_CLKIN_SC_P

CPU_CLKIN_SC_N

CPU_SID_R

CPU_SIC_R

CPU_SID_R

CPU_SIC_R

CPU_DBRDY

CPU_TRST#

CPU_TDI

CPU_TCK

CPU_TMS

CPU_TDO

CPU_DBREQ#

CPU_TEST26_BURNIN#

CPU_TEST25_H_BYPASSCLK_H

CPU_TEST25_L_BYPASSCLK_L

CPU_TEST19_PLLTEST0

CPU_TEST21_SCANEN

CPU_PRESENT#

CPU_TEST18_PLLTEST1

LDT_RST#

CPU_PWRGD

H_THERMTRIP#

LDT_RST#CPU_RESET#

CPU_DBRDY

CPU_TDO

CPU_VDDIO_SUS_FB_H

CPU_VDDIO_SUS_FB_L

CPU_VDDIO_SUS_FB_L

CPU_VDDIO_SUS_FB_H

CPU_TEST15_BP1

CPU_TEST14_BP0

CPU_TEST12_SCANSHIFTENB

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST20_SCANCLK2

CPU_PROCHOT#

CPU_RSVD_16

CPU_RSVD_17

CPU_RSVD_15

CPU_RSVD_19

CPU_RSVD_20

CPU_RSVD_18

CPU_TEST27_SINGLECHAIN

CPU_TEST27_SINGLECHAIN

CPU_DBREQ#

CPU_TRST#

CPU_TDI

CPU_TMS

CPU_TCK

CPU_TEST20_SCANCLK2

CPU_TEST24_SCANCLK1

CPU_TEST22_SCANSHIFTEN

CPU_TEST12_SCANSHIFTENB

CPU_TEST15_BP1

CPU_TEST14_BP0

LDT_STOP# LDT_STOP#_R

CPU_PROCHOT#

VID4 44

VID0 44

VID2 44

CPU_PSI# 44

VID3 44

VID5 44

VID1 44

CPU_CLK#18

CPU_CLK18

CPU_VDD_RUN_FB_L44

CPU_VDD_RUN_FB_H44

H_THERMDC35

H_THERMDA35

LDT_STOP#11,14

LDT_RST#14

CPU_PWRGD14

H_THERMTRIP# 35

CPU_VDDIO_SUS_FB_H43

CPU_VDDIO_SUS_FB_L43

EC_CPU_PROCHOT# 29

+1.2V_RUN

+1.8V_SUS

+1.8V_SUS

+1.8V_SUS

+1.8V_SUS

+1.8V_RUN+3.3V_RUN

+2.5V_RUN

+1.8V_SUS

+3.3V_SUS

+3.3V_SUS

+1.8V_RUN+1.8V_SUS

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 CTRL & DEBUG

561Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 CTRL & DEBUG

561Friday, May 04, 2007

Title

Size Document Number Rev

Date: Sheet

of

QUANTA

COMPUTER

FX5 1A

ATHLON64 CTRL & DEBUG

561Friday, May 04, 2007

AMD NPT S1 SOCKET

Processor Socket

ATHLON Control and Debug

ROUTE AS 80 Ohm DIFFERENTIAL PAIR

PLACE IT CLOSE TO CPU WITHIN 1"

LAYOUT: ROUTE VDDA TRACE APPROX. 50 mils WIDE (USE 2x25

mil TRACES TO EXIT BALL FIELD) AND 500 mils LONG. This trace

should be kept at least 20 mil from all other signal.

The AMD SI feature has errata, and will not be mplemented.

To Power

PSI_L is a Power Status Indicator signal. This signal is asserted when the

processor is in a low powerstate. PSI_L should be connected to the power

supply controller, if the controller supports “skipmode, or diode emulation

mode”. PSI_L is asserted by the processor during the C3 and S1 states.

HDT CONNECTOR

Place R168 and R165 < 1.5".

Route CPU_HTREF1/0 with 5mils trace

width and 10mils spacing from other

signals in X, Y, Z directions

for CPU rev.F.

If for rev.G , populate R195, R194 and depopulate R193.

SB this pin is 3.3V,need it level-shift.

1.Keep trace to resistor less then 600mils from cpu

and trace to ac caps less than 1250mils

2.CPUCLK and CPUCLK# mismatch <35mils.

Note:Place R218 on the Top of the board that

is acessible, and that shorting across this

resistor will toggle the Hyper Transport reset

signal.

SB600 ONLY

Place C625< 100mils from CPU.

Checkferrite bead with an approximate impedance of

35 , a maximum DC resistance of 40 m , and

a current rating of at least 500 mA.

T148T148

T35T35

MISC

U18D

MISC

U18D

VDDA2

F8

VDDA1

F9

RESET_L

B7

PWROK

A7

LDTSTOP_L

F10

HT_REF1

P6

HT_REF0

R6

VDDIO_FB_H

W9

VDDIO_FB_L

Y9

CLKIN_H

A9

CLKIN_L

A8

DBRDY

G10

TMS

AA9

TCK

AC9

TRST_L

AD9

TDI

AF9

TDO

AE9

DBREQ_L

E10

VID4

C6

VID3

A6

VID2

A4

VID1

C5

VID0

B5

THERMTRIP_L

AF6

SIC

AF4

SID

AF5

VDD_FB_H

F6

VDD_FB_L

E6

VID5

A5

PROCHOT_L

AC7

PSI_L

A3

TEST2

AB6

TEST3

Y6

TEST4

W8

TEST5

W7

TEST6

AA6

TEST7

C3

TEST8

C4

TEST10

K8

TEST26

AE6

TEST27

AF8

TEST28_L

H8

TEST28_H

J7

TEST20

AF7

TEST21

AB8

TEST22

AE8

TEST23

AD7

TEST24

AE7

TEST12

AC8

TEST14

C7

TEST15

F7

TEST16

E7

TEST17

D7

TEST9

C2

TEST13

AA7

TEST18

H10

TEST19

G9

TEST25_L

E8

TEST25_H

E9

TEST29_H

C9

TEST29_L

C8

RSVD0

P20

RSVD1

P19

RSVD2

N20

RSVD3

N19

RSVD4

R26

RSVD5

R25

RSVD6

P22

RSVD7

R22

RSVD8

H16

RSVD9

B18

RSVD10

B3

RSVD11

C1

RSVD12

H6

RSVD13

G6

RSVD14

D5

RSVD15

R24

RSVD16

W18

RSVD17

R23

RSVD18

AA8

RSVD19

H18

RSVD20

H19

CPU_PRESENT_L

AC6

T103T103

R168 44.2/FR168 44.2/F

T106T106

C623

100U/6.3V/3528

C623

100U/6.3V/3528

T149T149

R686

20K/F

R686

20K/F

12

T143T143

R544*220_NC R544*220_NC

1 2

R216 *300_NCR216 *300_NC

C634

0.22U/6.3V

C634

0.22U/6.3V

T130T130

T110T110

T112T112

R589

*4.7K_NC

R589

*4.7K_NC

R209 *300_NCR209 *300_NC

T121T121

R546 80.6/FR546 80.6/F

R221 *300_NCR221 *300_NC

R516 1K/FR516 1K/F

D39

RB751V40T1G

D39

RB751V40T1G

2 1

T34T34

C608

4.7U/6.3V/0603

C608

4.7U/6.3V/0603

T102T102

Q48

*MMST3904_NC

Q48

*MMST3904_NC

2

13

R194 *300_NCR194 *300_NC

R193 300R193 300

T125T125

T33T33

C625

470P/50V/NPO

C625

470P/50V/NPO

1 2

T127T127

R523

*10K_NC

R523

*10K_NC

T100T100

T95T95

R213

680

R213

680

12

T117T117

R566 510/FR566 510/F

R210

300

R210

300

R700

*0_NC

R700

*0_NC

12

R232

169/F_0603

R232

169/F_0603

R270

680

R270

680

12

T31T31

R541 300R541 300

T126T126

T144T144

T115T115

T145T145

C183

3900p_25V

C183

3900p_25V

T136T136

R527

300

R527

300

T147T147

U38

NL17SZ17DFT2G

U38

NL17SZ17DFT2G

2

5

4

3

T42T42

R521

4.7K

R521

4.7K

1 2

R535 510/FR535 510/F

T69T69

R212 *300_NCR212 *300_NC

T97T97

R536 *300_NCR536 *300_NC

T99T99

Q42

MMST3904-7-F

Q42

MMST3904-7-F

2

13

C827

*0.1U/10V_NC

C827

*0.1U/10V_NC

R549*220_NC R549*220_NC

1 2

R575 300R575 300

T47T47

T101T101

R218

680

R218

680

12

R223*220_NC R223*220_NC

1 2

T128T128

R165 44.2/FR165 44.2/F

R520

10K

R520

10K

R206 300R206 300

T131T131

R568*220_NC R568*220_NC

1 2

T113T113

C635

3300P_50V

C635

3300P_50V

R530 *300_NCR530 *300_NC

R547*220_NC R547*220_NC

1 2

C185

3900p_25V

C185

3900p_25V

R685

*0_NC

R685

*0_NC

12

C632

470P/50V/X7R

C632

470P/50V/X7R

12

T142T142

T134T134

R699

0

R699

0

12

T37T37

T139T139

JHDT1

*HDT conn_NC

JHDT1

*HDT conn_NC

GND

1

GND

2

Resreved

3

GND

4

Resreved

5

GND

6

DBREQ_L

7

GND

8

DBRDY

9

GND

10

TCK

11

GND

12

TMS

13

GND

14

TDI

15

GND

16

TRST_L

17

GND

18

TDO

19

GND

20

VDDIO

21

GND

22

VDDIO

23

RESET_L

24

GND

25

Q61

*MMST3904-7-F_NC

Q61

*MMST3904-7-F_NC

2

1 3

T119T119

R542 300R542 300

T120T120

T123T123

T30T30

L58

BLM18PG330SN1D_0603

L58

BLM18PG330SN1D_0603

R195 *300_NCR195 *300_NC

R587

*4.7K_NC

R587

*4.7K_NC

T133T133

C81447P/50V C81447P/50V

12

T118T118

T39T39

T124T124

T132T132

T70T70

R540 *300_NCR540 *300_NC

T122T122

R708

*680_NC

R708

*680_NC

12

T32T32

剩余49页未读,继续阅读

资源评论

JOZECN

- 粉丝: 746

- 资源: 2384

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜最新资源

- 基于matlab实现的一些优化算法,如基因,粒子群,布谷鸟,差分进化算法,模拟退火算法,带压缩因子的粒子群优化等.rar

- 基于matlab实现的遗传算法、免疫算法、退火算法、粒子群算法、鱼群算法、蚁群算法和神经网络算法等常用智能算法的MATLAB实现

- 基于matlab实现的蚁群算法是模拟蚁群觅食行为的一种优化算法

- 基于matlab实现的应用启发式算法-粒子群算法PSO,解决物流配送中心选址问题,结果好的解决了上述问题,值得参考.rar

- 基于matlab实现的用BP神经网络做风能预测,其中使用了PSO优化BPNN的初始权值和阈值.rar

- 基于matlab实现的用pso,对pid控制器进行优化设计.rar

- 第一讲.zip

- 基于matlab实现的用电负荷预测-msvm是在svm的基础上提出的多输出回归模型

- 基于matlab实现的有约束条件的粒子群算法,其中的代码对于解决一些约束问题.rar

- 基于matlab实现的智能微电网中利用粒子群算法实现多目标优化(有完整数据可运行).rar

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功