5

5

4

4

3

3

2

2

1

1

DD

CC

BB

AA

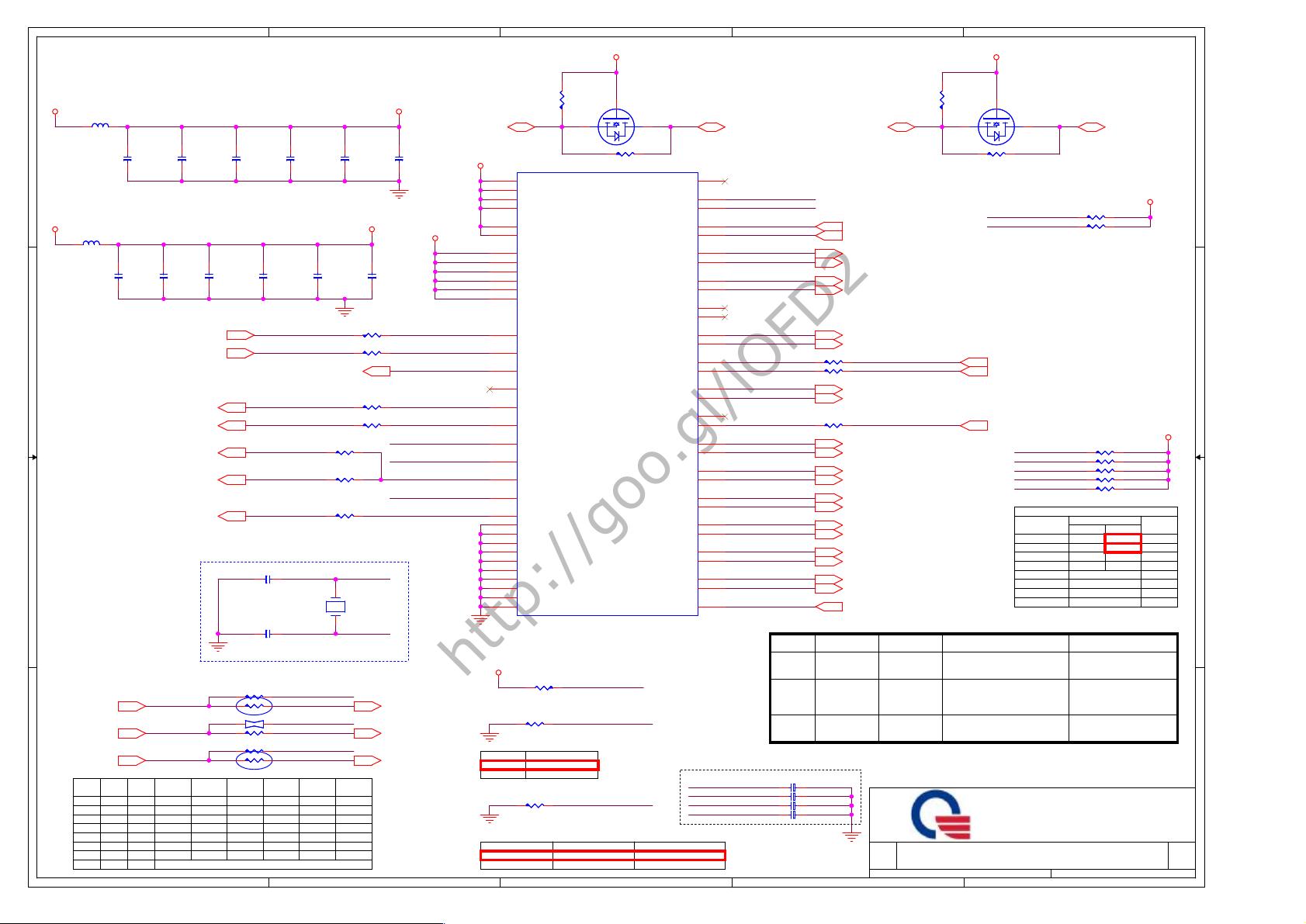

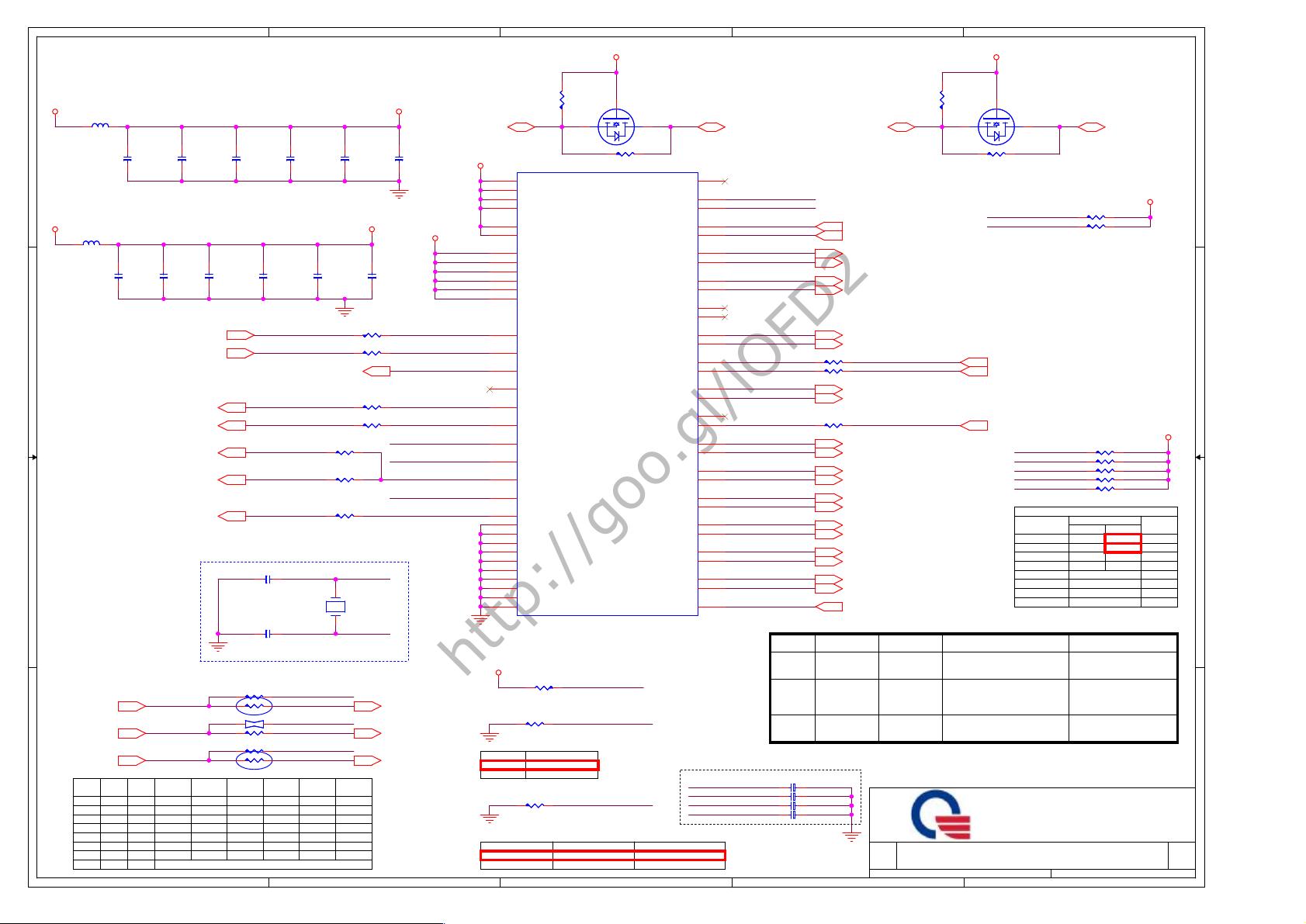

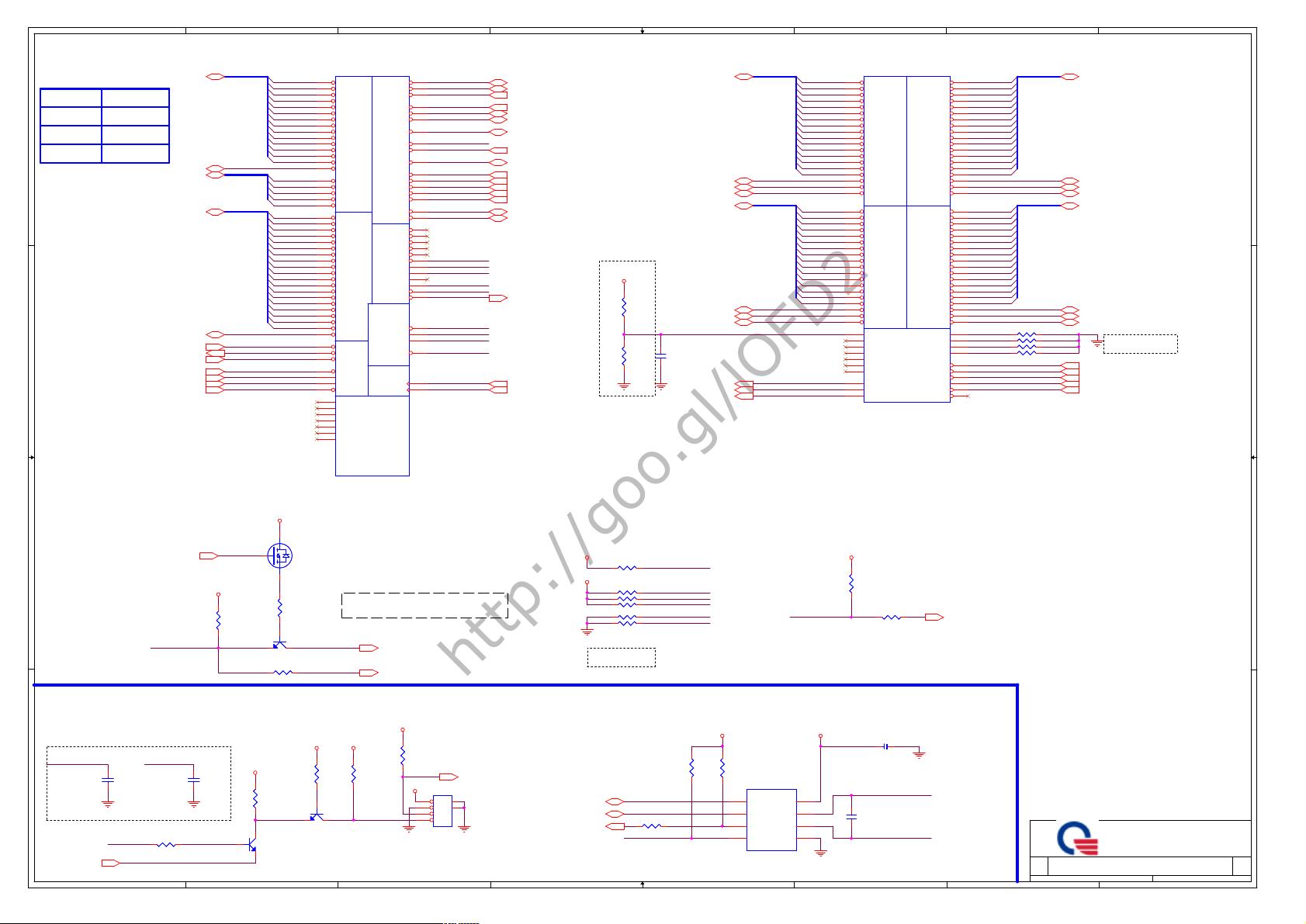

CR#_ACLKREQ#_SATA

CR#_BCLKREQ#_LAN

PCLK_DEBUG

PCLK_ICH_R

PCICLK_EC_R

CG_XOUT

CG_XIN

CG_XOUT

CG_XIN

CLK48_ICH

FSB

CLK14_ICH

CLK48_ICH_R

FSB

CLK14_ICH_R

MCH_BSEL0

MCH_BSEL1

MCH_BSEL2

CLK14_ICH_R

CLK48_ICH_R

SMBCK1

SMBDT1

PM_STPPCI#

PM_STPCPU#

PM_STPPCI#

PM_STPCPU#

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_MCH_BCLK

CLK_MCH_BCLK#

CR#_H

CR#_G CLKREQ#_MINI1

PECLK_MINI1

PECLK_MINI1#

DREFSSCLK

DREFSSCLK#

DREFCLK#

DREFCLK

VR_PWRGD_CK410

PECLK_ICH

PECLK_ICH#

PECLK_SATA

PECLK_SATA#

PECLK_LAN

PECLK_LAN#

CR#_E

CR#_A

CR#_B

CR#_E

CR#_G

CR#_H

CPU_BSEL2

CPU_BSEL0

CPU_BSEL1

CLK48_ICH_R

CLK14_ICH_R

PCLK_ICH_R

PCICLK_EC_R

CLK48_CARD

PCLK_ICH_R

PCICLK_EC_R

PCLK_ICH

PCICLK_EC

PCLK_DEBUG

PCLK_SMBPDAT_SMB

PECLK_MINI2

PECLK_MINI2#

PECLK_3GPLL#

PECLK_3GPLL

CLKREQ#_MCH

CLKREQ#_LAN(21)

PCLK_DEBUG(19)

CLK48_ICH(14)

CLK14_ICH(14)

CPU_BSEL0(4)

CPU_BSEL1(4)

CPU_BSEL2(4)

MCH_BSEL0 (7)

MCH_BSEL1 (7)

MCH_BSEL2 (7)

SMBCK1(16,19,21) PCLK_SMB (14,19)SMBDT1(16,19,21) PDAT_SMB (14,19)

PM_STPCPU# (14)

PM_STPPCI# (14)

CLK_CPU_BCLK (4)

CLK_CPU_BCLK# (4)

CLK_MCH_BCLK (6)

CLK_MCH_BCLK# (6)

PECLK_MINI1 (19)

PECLK_MINI1# (19)

DREFCLK (7)

DREFCLK# (7)

VR_PWRGD_CK410 (14)

DREFSSCLK (7)

DREFSSCLK# (7)

PECLK_ICH (13)

PECLK_ICH# (13)

PECLK_SATA (12)

PECLK_SATA# (12)

PECLK_LAN (21)

PECLK_LAN# (21)

CLKREQ#_SATA(14)

CLK48_CARD(21)

CLKREQ#_MINI1 (19)

PCLK_ICH(13)

PCICLK_EC(18)

PECLK_MINI2 (19)

PECLK_MINI2# (19)

PECLK_3GPLL# (7)

PECLK_3GPLL (7)

CLKREQ#_MCH (7)

CLKREQ#_MINI2 (19)

+3V_VDD_CLK

+1.05V_VDD_CLK

+1.05V +1.05V_VDD_CLK

+3V+3V

+3V

+3V

+3V +3V_VDD_CLK

+3V

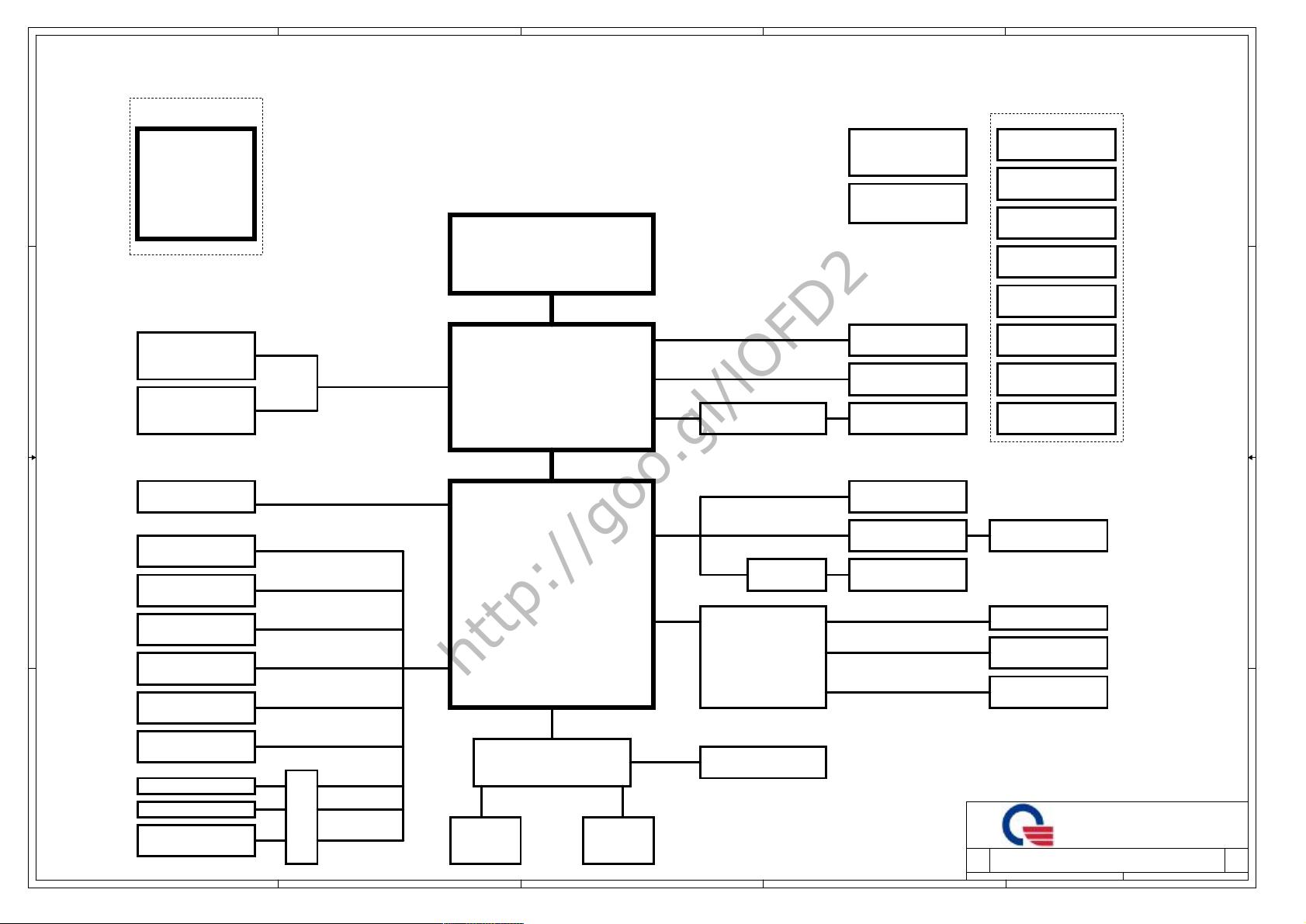

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

CLOCK GENERATOR CK505

1A

3 32Tuesday, September 29, 2009

ZE8

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

CLOCK GENERATOR CK505

1A

3 32Tuesday, September 29, 2009

ZE8

Size Document Number Rev

Date: Sheet of

Quanta Computer Inc.

PROJECT :

CLOCK GENERATOR CK505

1A

3 32Tuesday, September 29, 2009

ZE8

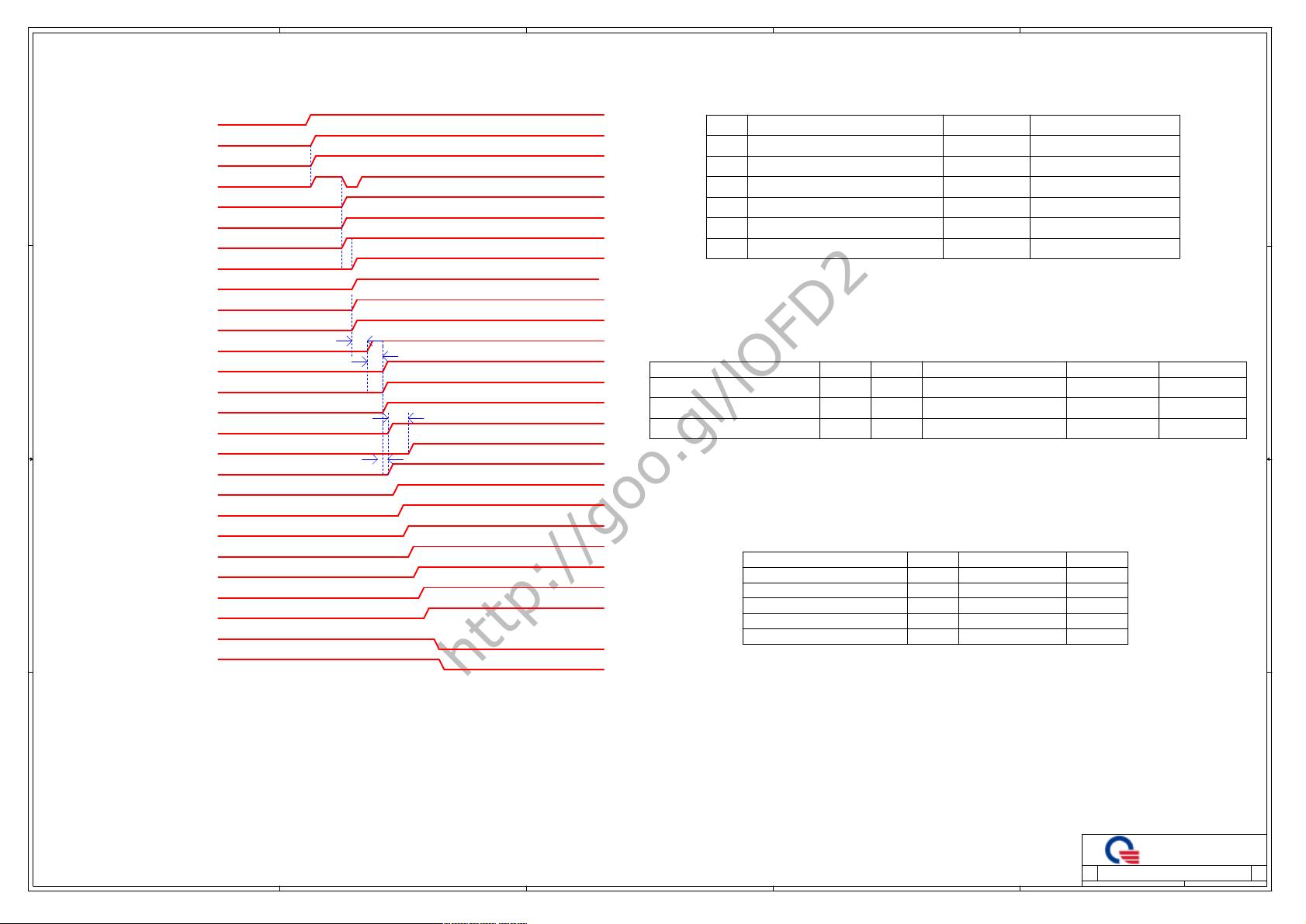

LCDCLK_SEL Pin 20/21 Pin 24/25

DOT_96/DOT96# LCDCLK/LCDCLK#

SRC_0/SRC_0# 27M/27M_SS

ITP_EN Pin 53/54

0

1

SRC_8/SRC_8#

ITP/ITP#

FSC

0

1

FSB FSA CPU

(MHz)

SRC

(MHz)

PCI

(MHz)

REF

(MHz)

DOT96

(MHz)

USB

(MHz)

000 266.6

133.3

200.0

166.6

333.3

100.0

400.0

100.0 33.3 14.318 96.0 48.0

Reserved

Clock Request Table

CLKREQ#

CR#_A

CR#_B

CR#_C

CR#_D

CR#_E

CR#_F

CR#_G

CR#_H

SRC0 SRC2

01

SRC4LCDCLK

SRC0 SRC2

SRC4LCDCLK

SRC6

SRC8

SRC9

SRC10

MAPPING Control

SATA

LAN

N/A

N/A

MINI2

N/A

MINI1

MCH

Clock Generator (CLK)

96.0 48.0100.0 33.3 14.318

96.0 48.0100.0 33.3 14.318

96.0 48.0100.0 33.3 14.318

96.0 48.0100.0 33.3 14.318

96.0 48.0100.0 33.3 14.318

96.0 48.0100.0 33.3 14.318

0

0

0

1

1

1

1

0

1

1

0

1

1

0

1

1

0

1

1

0

0

If XDP is not implemented the 1-k ±10% resistor is not required.

Layout notice: placed within 500-mils of CK505M

SLG8SP513VTR ,ICS9LPRS365BKLFT

PCI2/TME

PCI_4/

SEL_LCDCLK#

PCIF-5/ITP_EN

Pin 11

Pin 13

Pin 14

ICS9LPRS365

(ALPRS365000)

SLG8SP513VTR

(AL8SP513000)

(default)

(default)

PCI2/TME

PCI4/

27_Select

PCIF-5/ITP_EN

PULL HIGH PULL DOWN

NO OVERCLOCKING NORMAL RUN

PIN 24/25 IS 27MHz PIN 24/25

IS SRC/DOT

PIN 53/54 IS CPUITP PIN 53/54 IS SRC8

(default)

<MAIN> : SLG8SP513VTR(AL8SP513000)

<SECOND> : ICS9LPRS365BKLFT(ALPRS365000)

SMbus address D2

FAE suggest: place Cap before Resistor

0603 : card reader

use external crystal

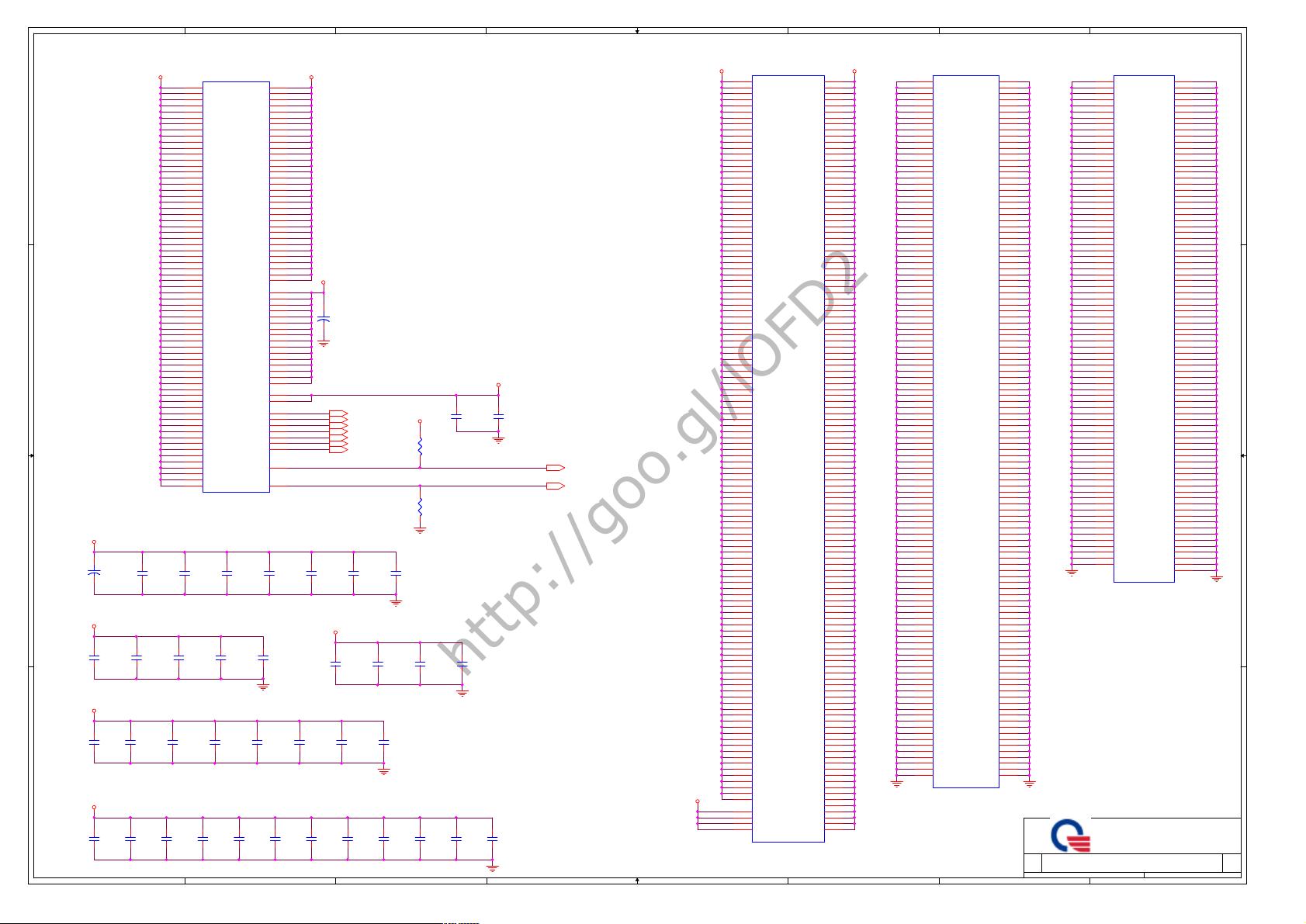

R143 475/F_4R143 475/F_4

R157

4.7K_4

R157

4.7K_4

R117 33_4R117 33_4

C228

0.1u/10V_4

C228

0.1u/10V_4

C239

0.1u/10V_4

C239

0.1u/10V_4

L17 PBY160808T-301Y-N/2A/300ohm_6L17 PBY160808T-301Y-N/2A/300ohm_6

R146 475/F_4R146 475/F_4

R118 33_4R118 33_4

Q6

2N7002

Q6

2N7002

3

2

1

R142 10K_4R142 10K_4

R127 1K_4R127 1K_4

C237

10u/10V_8

C237

10u/10V_8

R135 2.2K_4R135 2.2K_4

C220 *33p/50V_4C220 *33p/50V_4

R137 1K_4R137 1K_4

R133 *22_4R133 *22_4

R144 3G@10K_4R144 3G@10K_4

C231

0.1u/10V_4

C231

0.1u/10V_4

R119 1K_4R119 1K_4

R158 *0_4R158 *0_4

Q5

2N7002

Q5

2N7002

3

2

1

C230

0.1u/10V_4

C230

0.1u/10V_4

R152

4.7K_4

R152

4.7K_4

R124 22_4R124 22_4

C240

10u/10V_8

C240

10u/10V_8

R141 Short_4R141 Short_4 R140 10K_4R140 10K_4

R148 2.2K_4R148 2.2K_4

R149 2.2K_4R149 2.2K_4

C232

*0.1u/10V_4

C232

*0.1u/10V_4

R147 3G@475/F_4R147 3G@475/F_4

R139 10K_4R139 10K_4

C223

0.1u/10V_4

C223

0.1u/10V_4

R12210K_4 R12210K_4

C236

0.1u/10V_4

C236

0.1u/10V_4

R153 *0_4R153 *0_4

C219 *33p/50V_4C219 *33p/50V_4

R131 10K_4R131 10K_4

C234

0.1u/10V_4

C234

0.1u/10V_4

CK505

QFN

U7

SLG8SP513

CK505

QFN

U7

SLG8SP513

VDD_SRC_IO_2

43

VDD_48

16

VSS_SRC3

49

PCI0/CR#_A

8

PCI2/TME

11

NC

55

XTAL_OUT

2

SCLK

7

SDA

6

REF0/FSC/TESTSEL

5

VDD_SRC_IO_3

52

VDD_CPU_IO

56

VSS_REF

1

SRC8#/ITP#

53

PCIF5/ITP_EN

14

PCI3

12

VSS_PLL3

26

VDD_96_IO

19

VSS_48

18

VSS_IO

22

SRC1/SE1

24

VSS_SRC1

30

VSS_PCI

15

SRC5#/CPU_STOP#

44

SRC10

41

SRC8/ITP

54

VDD_CPU

62

PCI1/CR#_B

10

FSB/TEST/MODE

64

PCI4/LCDCLK_SEL

13

SRC2#/SATA#

29

SRC5/PCI_STOP#

45

VDD_SRC

46

VSS_CPU

59

SRC10#

42

XTAL_IN

3

USB_48/FSA

17

VDD_PLL3_IO

27

SRC2/SATA

28

SRC3/CR#_C

31

SRC4

34

SRC6

48

SRC7/CR#_F

51

SRC9

37

SRC11/CR#_H

40

SRC3#/CR#_D

32

SRC4#

35

SRC6#

47

SRC7#/CR#_E

50

SRC9#

38

SRC11#/CR#_G

39

CPU1#

57

CPU1

58

CPU0#

60

CPU0

61

VDD_PCI

9

VDD_SRC_IO_1

33

VDD_PLL3

23

VDD_REF

4

VSS_SRC2

36

SRC1#/SE2

25

SRC0/DOT96

20

SRC0#/DOT96#

21

CKPWRGD/PWRDWN#

63

VSS_BODY

65

R134 10K_4R134 10K_4

C229 *33p/50V_4C229 *33p/50V_4

C226 27p/50V_4C226 27p/50V_4

R132 10K_4R132 10K_4

Y1

14.318MHZ

Y1

14.318MHZ

21

R121 475/F_4R121 475/F_4

R145 10K_4R145 10K_4

C225 33p/50V_4C225 33p/50V_4

C227

0.1u/10V_4

C227

0.1u/10V_4

C238

0.1u/10V_4

C238

0.1u/10V_4

R126 33_4R126 33_4

L16 PBY160808T-301Y-N/2A/300ohm_6L16 PBY160808T-301Y-N/2A/300ohm_6

C224 *33p/50V_4C224 *33p/50V_4

R138 475/F_4R138 475/F_4

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜

信息提交成功

信息提交成功