没有合适的资源?快使用搜索试试~ 我知道了~

Axioo Neon MNC (Clevo W760s W765s) Laptop Schematics.pdf

需积分: 5 0 下载量 190 浏览量

2023-12-28

15:34:58

上传

评论

收藏 1.18MB PDF 举报

温馨提示

试读

39页

图纸

资源推荐

资源详情

资源评论

Schematic Diagrams

B-1

B.Schematic Diagrams

Appendix B: Schematic Diagrams

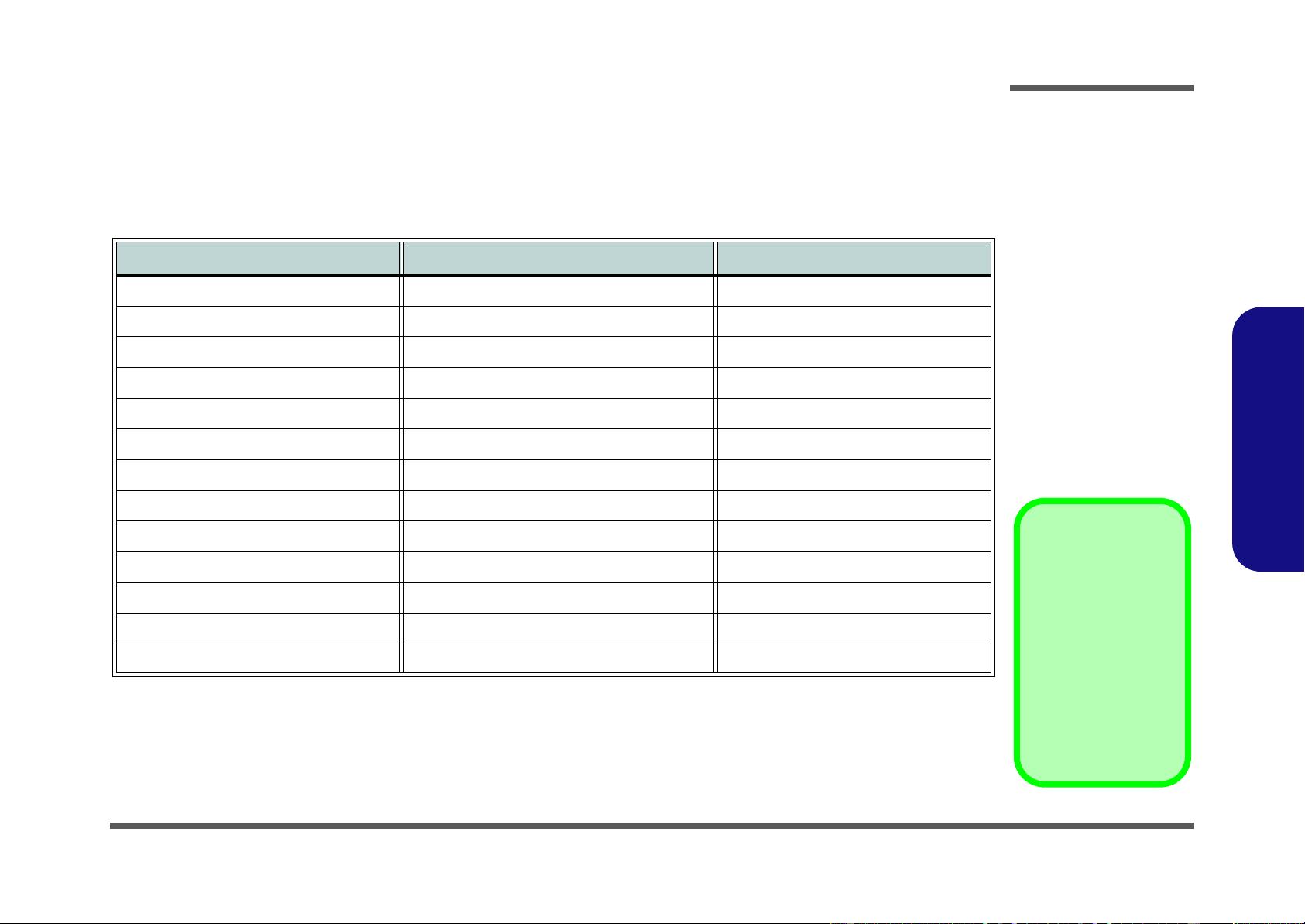

This appendix has circuit diagrams of the W760S/W765S notebook’s PCB’s. The following table indicates where to find

the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 968 PCI, IDE, MuTIOL, SPI 1/4 - Page B - 15 LED, PC Beep, TP, FP - Page B - 28

Penryn (Socket-P) 1/2 - Page B - 3 968 PCIE, LAN, GPIO 2/4 - Page B - 16 System/Ext-VGA Power - Page B - 29

Penryn (Socket-P) 2/2 - Page B - 4 968 USB SATA 3/4 - Page B - 17 AC-IN, Charger - Page B - 30

SiSM672 Host, PCIE 1/5 - Page B - 5 968 PWR, GND 4/4 - Page B - 18 VCORE - Page B - 31

SiSM672 DRAM 2/5 - Page B - 6 Clock Generator & Clock Buffer - Page B - 19 VDD3, VDD5) - Page B - 32

SiSM672 MuTIOL VGA 3/5 - Page B - 7 PHY Realtek 8201CL - Page B - 20 1.05VS, 1.2V, 1.5V - Page B - 33

SiSM672 PWR 4/5 - Page B - 8 KBC ITE8512E - Page B - 21 1.8V, 0.9VS - Page B - 34

SiSM672 GND 5/5 - Page B - 9 JMB385, Card Reader - Page B - 22 Click BD, Finger BD for M76 - Page B - 35

DDRII SO-DIMM - 1 - Page B - 10 Audio Codec ALC662 - Page B - 23 Multi Function Board - Page B - 36

DDRII SO-DIMM - 2 - Page B - 11 Audio AMP - Page B - 24 Audio Board - Page B - 37

SiS307ELV - Page B - 12 SATA HDD, PWR, LID - Page B - 25 Power Switch Board for M74 - Page B - 38

Panel, CRT - Page B - 13 Multi I/O, ODD, 3G, Click BD for M74 - Page B - 26 External ODD Board for W76 - Page B - 39

Inverter, Bluetooth, Fan - Page B - 14 New Card, Mini PCIE, USB - Page B - 27

Table B - 1

Schematic

Diagrams

Version Note

The schematic dia-

grams in this chapter

are based upon ver-

sion 6-7P-M74SA-001.

If your mainboard (or

other boards) are a lat-

er version, please

check with the Service

Center for updated di-

agrams (if required).

Schematic Diagrams

B - 2 System Block Diagram

B.Schematic Diagrams

System Block Diagram

Sheet 1 of 38

System Block

Diagram

5 33/6 67( /80 0) MHz

(USB3)

SiS968

IN T S PK

MINI PCIE

25 MH z

56 pin s TSS OP

F ING ER P RIN TE R B OA RD

USB, SPDIF, MIC IN

NORTH BRIDGE

(USB5)

10/100M PH Y

SPK_R, RJ-11

EC SMBUS

NV N10M-GE1

SOUTH BRIDGE

GOLANUSB4

HEADPHONE

RTL8201CL

(O pt ion al )

CLEVO M740S System Block Diagram

TPA

6047A4

PATA-133

INT. K/B

32.768 KHz

(USB0)

533 balls BGA

Intel Penryn

AZALIA LINK

EC

17.1* 8.1* 1.2m m

SATA I/II 3.0Gb/s

9.8* 6.4* 1.2m m

U SB & Pho ne

J ack B 'd

USB2

LPC

(USB1)

17.1*8.1*1.2mm

23*23*2.5mm

ITE 8502E

7IN1

35* 35*2 .7m m

Colck Generator

RJ-11

SYSTEM POWER,GPU CORE

EXTERNAL VGA

479 pins socket P

Synaptic

HP

OUT

CLICK BOARD

FSB

Bluetooth

VDD3,VDD5,3.3V,5V

Clock Buffer

SO-DIMM0

USB2.0

Azalia Codec

9*9*1.7mm

1 00 MHz

FingerPrint

ICS9P935

128 pi ns LQ FP

66 7/8 00 MHz

U SB6

3G CARD

AC-IN,CHARGER

SHEET 9

48pins LQF P

TOUCH PAD

PROCESSOR

CARD READER

RJ-45

( Opt io na l)

35* 35*2 .4m m

SATA ODD

14 .31 8 MHz

AZALIA

MDC

MODULE

M emor y T erm ina tio n

MODEM, CCD

SOCKET

MuTIOL 1G

PCIE

SATA HDD,

LID

27* 27*2.5m m

1.05VS,1.5V,1.2V

33 MHz

+VCORE

Mini PCIE

SHEET 10

M76SU

SPI

SOCKET

570balls mBGA

SO-DIMM1

852balls TEBGA

SOCKET

2 8p ins S SOP

LVDS (TV)

F75383M

JMB385

CRT

MDC CON

1 2 MHz

24 MHz

CCD

MIC

IN

IN T M IC

DDRII

810602-1703

SMART

FAN

9*9* 1.6mm

14*14 *1.6m m

SiSM672

New Card

48p in s L QF P

THERMAL

SENSOR

Realtek

ALC662

LCD CONNECTOR,

INVERTER

DDRII

AUDIO AMP

SiS307ELV

16 9ba ll s B GA

SPD IF

OUT

32 .7 68K Hz

(USB7)

MULTI I/O BOARD

1.8V,0.9VS

ICS9LPR600

24 pin s TSS OP

GMAC

Audio Board

SMART

BATTERY

48 0 M bps

13* 13*1. 7mm

Schematic Diagrams

Penryn (Socket-P) 1/2 B - 3

B.Schematic Diagrams

Penryn (Socket-P) 1/2

Sheet 2 of 38

Penryn (Socket-P)

1/2

H_ D#0

CPU_BSEL2

H_ A# 28

H_ THRMTRIP# 2 2

H_ DSTBN# 04

H_D #4 2

H_ D#4

L ayo ut N ote :

H_F ERR#

H_D #5 0

H_ REQ #1

Z0205

H_ HIT# 4

H_INIT #

Z0 2 2 4

H_DPSLP# 6

H_D #4 7

H_D #5 6

H_ DSTBN# 14

CPU_ BSEL 1

COMP0

H_ TDI

H_A# 9

H_ THERMDA

H_ D#[6 3:0 ]4

H_ BR 0# 4

R80 54.9_1%_04

6 -14 -5 60 3B- 11 B

H_ D#5

H_ PREQ#

R 9 2 5 1_ 1% _0 4

H_ TRDY# 4

H_NMI

H_D #3 3

R132 56_04

R1 35

*1 00 K_0 4

H_D #4 4

H_N MI

H_ THERMDA

3.3V

H_ RS#1 4

H_ DBSY# 4

H_D #5 3

H_BR0 #

H_DPW R# _R

H_D #4 3

H_DPSLP#

H_ TDO

5 6_0 4

H_ D#8

H_ D#1 5

R125 56_04

C los e to Th er ma l I C

H_SMI#

H_ D#[6 3:0 ]4

Z0203

H_A2 0M#

CPU_ BSEL 225

THERM_ALERT# 27

H_D #5 8

H_ A# 29

H_A# 10

R1 38 1 0K_ 04

C154 100P_50V_04

R 14 2 * 2 0m il _s ho r t - N M N P

Lay ou t not e:

H_ RS#2 4

H_ D#2 6

R58 39.2_1%_04

Z0206

H_ BR0 #

R127 56_04

SMC_CPU_ THERM 2 7

H_D #6 2

H_DINV# 14

Z0204

R44 9

27 . 4_ 1% _0 4

H_DPW R#_ R

H_D #3 6

H_A# 6

1. 0 5V S

H_ REQ #3

H_ D#3 1

H_A# 5

( Si S Recomm andation 200p)

H_PW RGD 4

H_ TRST#

A DM1 03 2 100 0p

F 753 83 M 220 0p

PS I # 3 7

H_D #6 0

H_ D#2

H_ BPM1#

R134 56_04

H_ D#7

R441

5 4. 9 _1 % _ 04

ADDR

GROUP_0

AD DR

GROUP_1

CONTROL

XDP/ITP SI GNALS

H CLK

THERMAL

R ESER VED

ICH

JSKT1A

Penry n

N3

P5

P2

L2

P4

P1

R1

Y2

U5

R3

W6

U4

Y5

U1

R4

T5

T3

W2

W5

Y4

J4

U2

V4

M4

N5

T2

V3

B2

D2

D2 2

L5

L4

K5

M3

N2

J1

A6

H1

M1

V1

D3

A22

A21

E2

AD4

AD3

AD1

AC4

G5

F1

C2 0

E1

H5

F21

A5

G6

E4

D2 0

C4

B3

C6

B4

H4

AC2

AC1

D2 1

K3

H2

K2

J3

L1

C1

F3

F4

G3

A3

D5

AC5

AA6

AB3

C7

A24

B25

AB5

G2

AB6

W3

AA4

AB2

AA3

F6

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[3]#

A[30]#

A[31]#

RSVD[01]

RSVD[02]

RSVD[03]

RSVD[04]

RSVD[05]

RSVD[06]

RSVD[07]

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A20M#

ADS#

ADSTB[0]#

ADSTB[1]#

RSVD[08]

BC LK [ 0 ]

BC LK [ 1 ]

BN R #

BP M [ 0 ] #

BP M [ 1 ] #

BP M [ 2 ] #

BP M [ 3 ] #

BPRI#

BR0#

DBR#

DBSY#

DEF ER#

DRD Y#

FER R#

HIT#

HITM#

IER R#

IGNNE#

INIT #

LI N T 0

LI N T 1

LOCK#

PR D Y #

PREQ#

PROCHOT#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

RESET #

RS[0]#

RS[1]#

RS[2]#

SMI#

STPCLK#

TC K

TD I

TDO

THERMTRIP#

TH E R M D A

THERMDC

TM S

TR D Y #

TR S T #

A[32]#

A[33]#

A[34]#

A[35]#

RSVD[09]

R108 * 51_04

H_ RS#0 4

H_T RST#

PS I #

CPU_BSEL0

R118 10_04

CPU_ BSEL 025

H_DINV# 04

H_T MS

H_ D#6

H_D #5 5

H_ BPM3#

H_ INIT#

H_A# 11

R158 4.7K_04

Q9

*NDS352AP_NL

G

DS

VDD3

H_ADSTB#14

H_ D#1 8

H_D #3 5

H_PW RGD

Z0216

COM P0 , COM P2 : 0.5 " Ma x, Zo =2 7.4 O hm s(2 0m il )

COM P1 , COM P3 : 0.5 " Ma x, Zo =5 5 O hm s(5 mi l)

Bes t es tim at e is 18 m ils w id e t ra ce fo r ou ter

lay er s and 1 4 mil s wi de tr ac e i f on in te rn al

lay er s.

Z0201

Z0209

C6 86 C los e to TE ST 4 (Pi n AF 26)

H_DSTBP#04

H_ D# 14

H_D #4 8

R116 * 330_04

H_A# 4

H_ A# 31

H_ REQ#[4 :0]4

SMD_CPU_ THERM 2 7

Z0210

H_A# 8

H_ A# 23

Thermal IC

H_A#[35:3]4

H_DSTBN #2 4

H_D #3 9

H_A# 15

H_ BPM2#

H_IERR#

R1 26 * 1K_0 4

COMP3

Z0207

H_ TCK

La yo ut No te :

H_ D#2 3

C5 53

1U _6 . 3V _X 5R _0 6

R137 * 10mil_short-NMNP

H_ D#1 9

H_IG NNE#

H_T CK

H_D #5 7

H_A2 0M#

H_A# 13

IF U SED Desk top CPU, H_CPURS T#,H_PWR GD,H_BRD ,need

add pull hig h resist or

H_ LOCK# 4

H_A# [35:3]4

C5 52

.01U_16V_X7R_04

R 4 59 1 K _0 4

H_ PRD Y#

H_PW RGD

R113 56_04

H_CL K_CPU# 25

H_DPW R# _R

H_D #6 3

H_A# 3

H_ A# 18

R149 68_04

CP U_ GRF E= 0. 7V

H_D #5 9

H_CPUSL P#

Z0214

R4 58 * 1K_0 4

R151

*330K_04

C1 64

1000P_50V_04

H_ REQ #2

Z0208

H_PROCH OT#

H_ A# 19

H_ A# 33

R114 56_04

If u sed M672 than

del R40 and add R42

H_ D#2 4

H_ A# 27

H_A# 7

R117 56_04

H_DSTBP# 3 4

VDD 3 20,23,27,34,35,36,38,40

R7 4

54.9_1%_04

H_INTR22

H_D #4 1

R106 * 51_04

H_ PRO CHOT#

H_ BPM0#

H_ REQ #0

If P ROCHOT# is route d betwee n CPU, I MVP and MCH,

pull -up resi stor has to be 6 8 ohm ? 5%. If n ot

use, pull-up resisto r has to be 56 o hm ? 5%

H_D# [63 :0] 4

R15 2

* 1 00 K_ 04

H_D #4 0

H_ D#9

H_ CPU RST#

C5 54 * .1U_10V_X7R_04

If used M672

tha n del R3

H_SMI#22

H_ D#2 2

H_D #4 9

H_D #4 5

H_ A# 30

H_STPCLK#

H_DSTBP# 2 4

CPU_ BSEL 2

H_ D#1 6

H_ THRMTRIP#

R8 5

2 7. 4 _1 % _ 04

3.3V 12,19,20,22,23,24,26,31,32,33,38,39,40

R5 7 6 80 _0 4

H_DSTBP#14

H_ HITM# 4

H_CPURST#

H_CL K_CPU 25

H_ TMS

H_ADSTB#04

H_PW RGD

Z0215

H_ DPWR# 4

TH E R M _ R S T#27

H_T DI

H_ D#2 5

H_ D#1 2

R101 51_1%_04

V_THERM

H_ NMI22

H_A# 16

R1 55 * 0_ 04

H_ A# 21

H_ BPRI# 4

H_DSTBN #3 4

H_A# 14

R130 56_04

H_ D#3

H_ D#1

Z0226

H_ A# 34

R 7 3 1 50 _1 % _ 04

1.05VS 3,4,6,7,24,39

H_D# [63 :0] 4

H_ A# 22

H_ A# 35

U7

AS C 7 5 2 5

1

2

3

4

5

6

7

8

VDD

D+

D-

TH E R M

GND

AL E R T

SDATA

SCLK

C PU to S B i nt er fac e

1. 05 V S

1. 0 5V S

H_DPSLP#

H_ D#3 0

H_ D#2 0

H_STPC LK#

R 8 8 5 6_ 1% _0 4

H_A# 12

H_D #3 8

H_D #3 2

H_ D#2 8

DA TA GRP 0

DA TA GRP 1

DATA GRP 2DATA GRP 3

MI SC

JSKT1B

Pen ryn

R26

U26

AA 1

Y1

E22

F24

J24

J23

H22

F26

K22

H23

N22

K25

P26

R23

E26

L23

M24

L22

M23

P25

P23

P22

T24

R24

L25

G22

T25

N25

Y22

AB 2 4

V2 4

V2 6

V2 3

T2 2

U25

U23

F23

Y25

W2 2

Y23

W2 4

W2 5

AA 2 3

AA 2 4

AB 2 5

AE 2 4

AD 2 4

G25

AA 2 1

AB 2 2

AB 2 1

AC 2 6

AD 2 0

AE 2 2

AF 2 3

AC 2 5

AE 2 1

AD 2 1

E25

AC 2 2

AD 2 3

AF 2 2

AC 2 3

E23

K24

G24

AF 1

H25

N24

U22

AC 2 0

E5

B5

D24

J26

L26

Y26

AE 2 5

H26

M26

AA 2 6

AF 2 4

AD26

AE 6

D6

D7

C24

B22

B23

C21

D25

AF26

A26

C23

C3

CO MP[0]

CO MP[1]

CO MP[2]

CO MP[3]

D[0]#

D[1]#

D[10]#

D[11]#

D[12]#

D[13]#

D[14]#

D[15]#

D[16]#

D[17]#

D[18]#

D[19]#

D[2]#

D[20]#

D[21]#

D[22]#

D[23]#

D[24]#

D[25]#

D[26]#

D[27]#

D[28]#

D[29]#

D[3]#

D[30]#

D[31]#

D[3 2]#

D[3 3]#

D[3 4]#

D[3 5]#

D[3 6]#

D[3 7]#

D[3 8]#

D[3 9]#

D[4]#

D[4 0]#

D[4 1]#

D[4 2]#

D[4 3]#

D[4 4]#

D[4 5]#

D[4 6]#

D[4 7]#

D[4 8]#

D[4 9]#

D[5]#

D[5 0]#

D[5 1]#

D[5 2]#

D[5 3]#

D[5 4]#

D[5 5]#

D[5 6]#

D[5 7]#

D[5 8]#

D[5 9]#

D[6]#

D[6 0]#

D[6 1]#

D[6 2]#

D[6 3]#

D[7]#

D[8]#

D[

9]#

TEST5

DINV[0]#

DINV[1]#

DINV[2]#

DINV[3]#

DPRSTP#

DPSLP#

DPW R#

DSTBN[0]#

DSTBN[1]#

DSTBN[2]#

DSTBN[3]#

DSTBP[0]#

DSTBP[1]#

DSTBP[2]#

DSTBP[3]#

GTLREF

PSI#

PWRGO OD

SLP#

TEST3

BSEL[0]

BSEL[1]

BSEL[2]

TEST2

TEST4

TEST6

TEST1

TEST7

H_D #5 4

R119 * 56_04

D05

H_ D#2 9

H_D #5 2

H_CPUSL P#

Q10

*2N7002W

G

DS

1. 0 5V S

H_DPRSTP# 6,3 7

CPU_ BSEL 0

H_D #5 1

H_ A# 17

H_ A# 26

R157 4.7K_04

R 1 50 1 K _0 4

R out e H_ THE RM DA an d

H _TH ER MD C o n sa me la ye r.

1 0 m il t rac e on 10 m il sp ac in g.

VDD3

H_ D#1 3

COMP3

H_ D#1 0

H_IN TR

R115 56_04

La yo ut No te :

H_PROCHOT#22

H_IGNNE#22

H_ THERMDC

CPU_BSEL1

Z0225

R122 56_04

H_FERR#22

COMP2

H_ D#1 1

R407 1K_1%_04

R148 150_1%_04

H_STPCLK#22

H_D #3 7

L ayo ut N ote :

H_ CPURST# 4

H_ DRDY# 4

H_PREQ#

H_DINV# 3 4

H_ D#2 7

R131 56_04

H_ BN R# 4

H_ D#2 1

H_ A# 24

C180

* .01U_16V_X7R_04

R 1 20 * 0 _0 4

C1 63

.1 U_1 0V_ X7 R_0 4

R 6 6 5 1_ 1% _0 4

0. 5" m ax, Z o= 55 O hm s

CPU_ BSEL 125

H_D #6 1H_ DBR #

Z0202

R8 9 5 6_ 04

H_ INIT# 22

COMP1

H_DBR#

H_IGNN E#

H_ A# 25

R100 51_1%_04

R40 6

2K _ 1% _ 04

R147 56_04

H_DINV# 2 4

COMP1

H_D #3 4

Z0 2 2 3

H_ DEFER# 4

H_ IERR #

Z0213

H_INTR

H_ A# 32

H_ REQ #4

CPU_G TL REF

H_ THERMDC

H_ A# 20

H_SMI#

V_THERM

H_ AD S# 4

H_ A2 0M #22

R156 * 10K_04

COMP2

H_D #4 6

H_T HRMTRIP#

H_ D#1 7

Z0211

Z0212

R65 27.4_1%_04

H_CPUSL P# 22

COMP0

H_F ERR#

R 4 60 1 K _0 4

Schematic Diagrams

B - 4 Penryn (Socket-P) 2/2

B.Schematic Diagrams

Penryn (Socket-P) 2/2

VCOR EVC O R E

1.05VS

1.5VS

VC ORE

VCORE

VCORE

VCORE

VCORE

1.05VS

VCORE

VCORE

1.05VS

1.5VS 6,33,35

VCORE 37

1.05VS 2,4,6,7,24,39

VSSSENSE 37

VCC SEN SE 37

H_VID[6 :0] 3 7

H_ VID6

H_ VID1

H_ VID5

H_ VID3

VCCSENSE

H_ VID2

H_ VID4

VSSSENSE

H_ VID0

Z0301

R22

* 15mil_short-NMNP

C5 82

.1U _1 0V_ X7 R_ 04

C46

.1U_10V_X7 R_04

C1 46

10 U _ 6. 3 V _X 5 R _0 8

C5 1

1U _6 . 3V _ X5 R _ 06

C594

* 10U_6.3V_X5R_08

C161

. 0 1U _1 6V _ X7 R _ 04

C140

1U_6.3V_X5R _06

C1 18

10U_6.3V_X5R_08

C61

10U_6.3V_X5R_08

C5 9

10U _6.3V_X5R_08

C565

* 10U_6.3V_X5R _08

C57 7

10 U _ 6. 3 V _X 5R _0 8

C6 8

1U _6 . 3V _ X5 R _ 06

C5 68

10 U _ 6. 3 V _X 5 R _0 8

C129

10U _6.3V_X5R_08

C5 93

10 U _ 6. 3 V _X 5 R _0 8

C1 11

.1U_10V_X7R_04

C584

1U_6.3V_X5R _06

C141

.1U_10V_X7 R_04

C6 2

.1U _1 0V_ X7 R_ 04

C12 4

*1U_6.3V_X5R_06

C57 5

10 U _ 6. 3 V _X 5R _0 8

C65

10 U _ 6. 3 V _X 5R _0 8

C10 0

1U_6.3V_X5R_06

C583

.1 U_ 10 V_X7R _0 4

JS K T 1C

Pen ryn

.

A7

A9

A10

A12

A13

A15

A17

A18

A20

B7

B9

B10

B12

B14

B15

B17

B18

B20

C9

C1 0

C1 2

C1 3

C1 5

C1 7

C1 8

D9

D1 0

D1 2

D1 4

D1 5

D1 7

D1 8

E7

E9

E10

E12

E13

E15

E17

E18

E20

F7

F9

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AA 1 0

AA 1 2

AA 1 3

AA 1 5

AA 1 7

AA 1 8

AA 2 0

AB9

AC10

AB 1 0

AB 1 2

AB 1 4

AB 1 5

AB 1 7

AB 1 8

AB2 0

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE1 0

AE1 2

AE1 3

AE1 5

AE1 7

AE1 8

AE2 0

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

B26

J6

K6

M6

J2 1

K21

M21

N21

N6

R21

R6

T2 1

T6

V21

W2 1

AF7

AD6

AF5

AE5

AF4

AE3

AF3

AE2

AE7

C26

G21

V6

V C C [ 00 1]

V C C [ 00 2]

V C C [ 00 3]

V C C [ 00 4]

V C C [ 00 5]

V C C [ 00 6]

V C C [ 00 7]

V C C [ 00 8]

V C C [ 00 9]

V C C [ 01 0]

V C C [ 01 1]

V C C [ 01 2]

V C C [ 01 3]

V C C [ 01 4]

V C C [ 01 5]

V C C [ 01 6]

V C C [ 01 7]

V C C [ 01 8]

V C C [ 01 9]

V C C [ 02 0]

V C C [ 02 1]

V C C [ 02 2]

V C C [ 02 3]

V C C [ 02 4]

V C C [ 02 5]

V C C [ 02 6]

V C C [ 02 7]

V C C [ 02 8]

V C C [ 02 9]

V C C [ 03 0]

V C C [ 03 1]

V C C [ 03 2]

V C C [ 03 3]

V C C [ 03 4]

V C C [ 03 5]

V C C [ 03 6]

V C C [ 03 7]

V C C [ 03 8]

V C C [ 03 9]

V C C [ 04 0]

V C C [ 04 1]

V C C [ 04 2]

V C C [ 04 3]

V C C [ 04 4]

V C C [ 04 5]

V C C [ 04 6]

V C C [ 04 7]

V C C [ 04 8]

V C C [ 04 9]

V C C [ 05 0]

V C C [ 05 1]

V C C [ 05 2]

V C C [ 05 3]

V C C [ 05 4]

V C C [ 05 5]

V C C [ 05 6]

V C C [ 05 7]

V C C [ 05 8]

V C C [ 05 9]

V C C [ 06 0]

V C C [ 06 1]

V C C [ 06 2]

V C C [ 06 3]

V C C [ 06 4]

V C C [ 06 5]

V C C [ 06 6]

V C C [ 06 7]

VCC[068]

VCC[069]

VCC[070]

VCC[071]

VCC[072]

VCC[073]

VCC[074]

VCC[075]

VCC[076]

VCC[077]

VCC[078]

VCC[079]

VCC[080]

VCC[081]

VCC[082]

VCC[083]

VCC[084]

VCC[085]

VCC[086]

VCC[087]

VCC[088]

VCC[089]

VCC[090]

VCC[091]

VCC[092]

VCC[093]

VCC[094]

VCC[095]

VCC[096]

VCC[097]

VCC[098]

VCC[099]

VCC[100]

VCCA[01 ]

VCCP[03 ]

VCCP[04 ]

VCCP[05 ]

VCCP[06 ]

VCCP[07 ]

VCCP[08 ]

VCCP[09 ]

VCCP[10 ]

VCCP[11 ]

VCCP[12 ]

VCCP[13 ]

VCCP[14 ]

VCCP[15 ]

VCCP[16 ]

VCCSENSE

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VSSSENSE

VCCA[02 ]

VCCP[01 ]

VCCP[02 ]

C585

1U_6.3V_X5R_06

C85

.1U_ 1 0V_ X7 R_ 04

C67

.1 U_ 10 V_X7R _0 4

C1 23

* 1 0U _6 . 3V _ X5 R _ 08

C113

1U_6.3V_X5R _06

C5 72

.1U_10V_X7R_04

JS K T 1D

Pe n r y n

.

P6

AE11

A8

A11

A14

A16

A19

A23

AF2

B6

B8

B11

B13

B16

B19

B21

B24

C5

C8

C1 1

C1 4

C1 6

C1 9

C2

C2 2

C2 5

D1

D4

D8

D1 1

D1 3

D1 6

D1 9

D2 3

D2 6

E3

E6

E8

E11

E14

E16

E19

E21

E24

F5

F8

F11

F13

F16

F19

F2

F22

F25

G4

G1

G2 3

G2 6

H3

H6

H2 1

H2 4

J2

J5

J2 2

J2 5

K1

K4

K23

K26

L3

L6

L2 1

L2 4

M2

M5

M2 2

M2 5

N1

N4

N2 3

N2 6

P3 A25

AF2 1

AF1 9

AF1 6

AF1 3

AF1 1

AF8

AF6

A2

AE26

AE23

AE19

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

Y6

A4

AE14

AE16

AE8

AF2 5

VSS[082 ]

VSS[148 ]

VSS[002]

VSS[003]

VSS[004]

VSS[005]

VSS[006]

VSS[007]

VSS[008]

VSS[009]

VSS[010]

VSS[011]

VSS[012]

VSS[013]

VSS[014]

VSS[015]

VSS[016]

VSS[017]

VSS[018]

VSS[019]

VSS[020]

VSS[021]

VSS[022]

VSS[023]

VSS[024]

VSS[025]

VSS[026]

VSS[027]

VSS[028]

VSS[029]

VSS[030]

VSS[031]

VSS[032]

VSS[033]

VSS[034]

VSS[035]

VSS[036]

VSS[037]

VSS[038]

VSS[039]

VSS[040]

VSS[041]

VSS[042]

VSS[043]

VSS[044]

VSS[045]

VSS[046]

VSS[047]

VSS[048]

VSS[049]

VSS[050]

VSS[051]

VSS[052]

VSS[053]

VSS[054]

VSS[055]

VSS[056]

VSS[057]

VSS[058]

VSS[059]

VSS[060]

VSS[061]

VSS[062]

VSS[063]

VSS[064]

VSS[065]

VSS[066]

VSS[067]

VSS[068]

VSS[069]

VSS[070]

VSS[071]

VSS[072]

VSS[073]

VSS[074]

VSS[075]

VSS[076]

VSS[077]

VSS[078]

VSS[079]

VSS[080]

VSS[08 1] VSS[162 ]

VSS[161 ]

VSS[160 ]

VSS[159 ]

VSS[158 ]

VSS[157 ]

VSS[156 ]

VSS[155 ]

VSS[154 ]

VSS[153 ]

VSS[152 ]

VSS[151 ]

VSS[083 ]

VSS[084 ]

VSS[085 ]

VSS[086 ]

VSS[087 ]

VSS[088 ]

VSS[089 ]

VSS[090 ]

VSS[091 ]

VSS[092 ]

VSS[093 ]

VSS[094 ]

VSS[095 ]

VSS[096 ]

VSS[097 ]

VSS[098 ]

VSS[099 ]

VSS[100 ]

VSS[101 ]

VSS[102 ]

VSS[103 ]

VSS[104 ]

VSS[105 ]

VSS[107 ]

VSS[108 ]

VSS[109 ]

VSS[110 ]

VSS[111 ]

VSS[112 ]

VSS[113 ]

VSS[114 ]

VSS[115 ]

VSS[116 ]

VSS[117 ]

VSS[118 ]

VSS[119 ]

VSS[120 ]

VSS[121 ]

VSS[122 ]

VSS[123 ]

VSS[124 ]

VSS[125 ]

VSS[126 ]

VSS[127 ]

VSS[128 ]

VSS[129 ]

VSS[130 ]

VSS[131 ]

VSS[132 ]

VSS[133 ]

VSS[134 ]

VSS[135 ]

VSS[136 ]

VSS[137 ]

VSS[138 ]

VSS[139 ]

VSS[140 ]

VSS[141 ]

VSS[142 ]

VSS[143 ]

VSS[144 ]

VSS[145 ]

VSS[146 ]

VSS[106 ]

VSS[001]

VSS[149 ]

VSS[150 ]

VSS[147 ]

VSS[163 ]

C564

10U _6.3V_X5R_08

C846

1U_6.3V_X5R_06

C159

* 10U_6.3V_X5R_08

C8 8

* 1 U _ 6. 3 V _X 5R _0 6

C86

.1U_ 1 0V_ X7 R_ 04

C581

.1U_10V_X7 R_04

C126

.1 U_ 10 V_X7R _0 4

C566

10U_6.3V_X5R_08

C75

1U_6.3V_X5R _06

+

C574

150U_4V_B2

C5 0

10U _6.3V_X5R_08

C1 30

*.1U_10V_X7R_04

C7 7

.1U_10V_X7R_04

C49

1U_6.3V_X5R_06

C580

10U _6.3V_X5R_08

C9 5

10U_6.3V_X5R_08

C1 28

1U_6.3V_X5R_06

L12

H C B 16 08 K F - 12 1T 25

C155

.1 U_ 10 V_X7R _0 4

C11 6

.1U_ 1 0V_ X7 R_ 04

R21

*1 5 mil_ s ho rt-NMNP

Pow er Plane

Layout note:

Ne ar pi n B26

Layout note:

130m A

Rou te V CCSEN SE an d

VSS SENS E tra ces a t 27. 4

ohm s wi th 50 mils spac ing.

Pla ce P U and PD w ithin 1

inc h of CPU.

Check cap for santa rosa platform

2A

PLACE NEAR C PU

6-07-10611-7C0

P LACE NE AR CPU

5/10

D05 10/15

D05 10/15

Sheet 3 of 38

Penryn (Socket-P)

2/2

Schematic Diagrams

SiSM672 Host, PCIE 1/5 B - 5

B.Schematic Diagrams

SiSM672 Host, PCIE 1/5

NB_GTLREF

1.05VS

C1XAVDD

C1XAVSS

C4XAVDD

C4XAVSS

1. 0 5V S

1.8VS

C1XAVSS

C1XAVDD 1.8VS C4XAVDD

C4XAVSS

NB_G TL REF

1. 0 5V S

NB_PCIE_ 1.2 VS1.2VS

1.8VS 5,6,7,11,13,14,15,17,19,21,22,23,24,25,35

1 . 05 V S 2, 3 , 6, 7 , 24 , 39

H_ BNR#2

H _DBSY#2

H_D RDY#2

H_ HIT#2

H_H ITM#2

H_ADS#2

H _TRDY#2

H_ LO CK#2

H_D#[63:0] 2

H_ A#[3 5:3]2

H_ DINV# 0 2

H_ DINV# 1 2

H_ DINV# 2 2

H_ DINV# 3 2

H_ DSTBN #0 2

H_ DSTBN #1 2

H_ DSTBN #2 2

H_ DSTBN #3 2

H_ DSTBP# 0 2

H_ DSTBP# 1 2

H_ DSTBP# 2 2

H_ DSTBP# 3 2

H_R EQ #[4:0]2

H_ AD STB# 02

H_ AD STB# 12

H_ CL K_NB#25

H_ CL K_NB25

H_BPRI#2

H_ BR0#2

H_ RS#02

H_ RS#12

H_ RS#22

H_DEFER#2

H_CPURST#2

H_ PW RGD2

H_D PWR #2

PCIE_CLK_NB 25

PCIE_CLK_NB# 25

PCIE_WAKE#23 , 3 3

PCI_INT#A6,21

PE 0 R X 012

PE 0 R X 0 #12

PE 0 R X 112

PE 0 R X 1 #12

PE 0 R X 212

PE 0 R X 2 #12

PE 0 R X 312

PE 0 R X 3 #12

PE 0 R X 412

PE 0 R X 4 #12

PE 0 R X 512

PE 0 R X 5 #12

PE 0 R X 612

PE 0 R X 6 #12

PE 0 R X 712

PE 0 R X 7 #12

PE0TX0 12

PE0TX0# 12

PE0TX1 12

PE0TX1# 12

PE0TX2 12

PE0TX2# 12

PE0TX3 12

PE0TX3# 12

PE0TX4 12

PE0TX4# 12

PE0TX5 12

PE0TX5# 12

PE0TX6 12

PE0TX6# 12

PE0TX7 12

PE0TX7# 12

1.2VS 7,35

HDVAP0 11

HDVAN2 11

HDVAN0 11

HDVAP2 11

HDVAN1 11

HDVAP1 11

HDVBN1 11

HDVBP0 11

HDVBP2 11

HDVBN0 11

HDVBN2 11

HDVBP1 11

H_ D# 4

H_ A#1 9

H_ A#2 0

H_ D# 5

H_ A#2 1

H_ D# 6

H_ A#2 2

H_ D# 44

H_ D# 7

H_ A#2 3

H_ D# 45

H_ D# 8

H_ A#2 4

H_ A#2 5

H_ D# 46

H_ D# 9

H_ A#2 6

H_ D# 10

H_ D# 47

H_ A#2 7

H_ D# 11

H_ D# 48

H_ A#2 8

H_ D# 12

H_ D# 49

H_ A#2 9

H_ D# 13

H_ A#3 0

H_ D# 50

H_ D# 14

H_ A#3 1

NB_ PC REQ#

H_ D# 51

Z0401

H_ D# 15

H_ D# 52

H_ D# 16

H_ D# 53

H_ D# 17

H_ D# 54

H_ D# 18

H_ D# 19

H_ D# 20

H_ D# 21

H_ REQ# 3

H_ REQ# 2

H_ REQ# 4

H_ REQ# 0

H_ REQ# 1

H_ D# 0

H_ D# 22

H_ D# 23

H_ A#3

H_ D# 55

H_ D# 24

H_ D# 25

H_ D# 56

H_ D# 26

H_ D# 57

H_ D# 27

H_ D# 58

H_ D# 28

H_ D# 59

H_ D# 29

H_ D# 60

H_ A#3 2

H_ D# 30

H_ D# 61

H_ A#3 3

H_ D# 31

H_ A#3 4

H_ D# 62

H_ D# 32

H_ A#3 5

H_ D# 63

H_ D# 33

H_ D# 34

H_ D# 35

H_ A#4

H_ D# 36

H_ A#5

H_ D# 37

H_ A#6

H_ A#7

H_ D# 38

H_ A#8

NB_ COMP#

NB_ COMP

H_ D# 39

H_ A#9

H_ A#1 0

H_ D# 40

H_ A#1 1

H_ D# 41

H_ A#1 2

H_ A#1 3

H_ D# 42

H_ A#1 4

H_ D# 43

H_ A#1 5

H_ D# 1

H_ A#1 6

H_ D# 2

H_ A#1 7

H_ D# 3

H_ A#1 8

NB_ PC REQ#

Z0402

Z0403

Z0404

Z0405

Z0406

Z0407

Z0408

Z0410

Z0409

Z0411

Z0412

Z0413

Z0414

Z0415

Z0416

Z0417

Z0438

Z0439

Z0440

Z0441

Z0442

Z0443

Z0444

Z0445

Z0446

Z0447

Z0448

Z0449

Z0450

Z0451

Z0452

Z0453

Z0454

Z0463

Z0455

Z0462

C 6 28 * . 1U _ 1 0V _ X7 R _ 04

NC1 0 NC_04

C 6 17 * . 1U _ 1 0V _ X7 R _ 04

C 6 19 * . 1U _ 1 0V _ X7 R _ 04

C 6 30 * . 1U _ 1 0V _ X7 R _ 04

C 6 21 * . 1U _ 1 0V _ X7 R _ 04

R196 *56_04

R192

150_1%_04

C 6 18 * . 1U _ 1 0V _ X7 R _ 04

C264

. 0 1U _1 6V _ X 7R _ 04

PCIE

U32D

SiSM6 72

E4

E5

F1

G1

H3

H2

H1

J1

V1

V6

W4

W1

W2

Y1

Y6

AA4

AA1

AB1 AB6

AC4

AB2

AC 1

AD 1

AD6

AE4

AE1

AE2

AF1

AG 1

T2

U1

K1

K2

L1

M1

N1

N2

P1

R1

T1

J6

G6

G4

J4

L6

M4

P6

P4

H6

G5

K6

J5

M6

M5

R6

P5

W6

W5

AA6

AA5

AC6

AC5

AE6

AE5

P7

R7

T7

U7

V7

D7

G1 6

T5

T4

PERP0

PERN0

PERP1

PERN1

PERP2

PERN2

PERP3

PERN3

PERN9

PETP8

PETP9(HDVBP2)

PERP10

PERN1 0

PERP11

PETP10 (HDVBP1)

PETP11 (HDVBP0)

PERN1 1

PERP12 PETP12

PETP13 (HDVAP2)

PERN1 2

PERP13

PERN1 3

PETP14 (HDVAP1)

PETP15 (HDVAP0)

PERP14

PERN1 4

PERP15

PERN1 5

PERN8

PERP9

PERP4

PERN4

PERP5

PERN5

PERP6

PERN6

PERP7

PERN7

PERP8

PETP2

PETP0

PETP1

PETP3

PETP4

PETP5

PETP6

PETP7

PETN 0

PETN 1

PETN 2

PETN 3

PETN 4

PETN 5

PETN 6

PETN 7

PETN 8

PETN9(HDVBN2)

PETN10(HD VBN 1)

PETN11(HD VBN 0)

PETN12

PETN13(HD VAN 2)

PETN14(HD VAN 1)

PETN15(HD VAN 0)

PCIEAVDD

PCIEAVDD

PCIEAVDD

PCIEAVDD

PCIEAVDD

PME#

INTX#

REF CLK+

REF CLK-

C 6 25 * . 1U _ 1 0V _ X7 R _ 04

C2 55

.1U_1 0V_X7R_0 4

C 6 27 * . 1U _ 1 0V _ X7 R _ 04

C2 3 0

.1U_10V_X7R _04

C26 2

.1U_10V_X7R_04

C 6 20 * . 1U _ 1 0V _ X7 R _ 04

R195

75_1%_04

Ho st

U32C

SiSM6 72

R3 4

E21

P32

B16

C1 7

A17

B18

F18

G1 8

P31

N3 0

P33

L32

P30

P28

F21

K34

M3 1

K33

M3 3

M3 2

L34

N3 2

N3 4

M3 4

T34

R3 0

R2 9

R3 2

P34

U3 4

AA34

N29

M30

M28

L30

L29

K28

K31

K30

H31

G34

H32

G32

K32

F34

F33

F32

H28

J30

H30

G29

J29

G30

F30

D33

D34

B32

B33

C34

D31

A32

A31

C31

B30

C30

A30

D28

G28

C29

C28

E28

E27

C27

G26

E26

D26

B26

A26

C26

G22

C24

A25

B24

C25

A24

E23

E25

G24

D22

C22

E22

C23

A23

A22

B22

T32

T28

T31

T33

T30

U3 2

U3 0

V34

U2 9

V33

V32

V28

V31

W34

Y33

W32

V30

W30

Y34

Y28

W29

Y32

Y30

Y31

AA32

AA30

AA29

AB33

AB34

AB32

AC34

AB30

AB31

J32

E32

F27

F23

H33

E31

B28

D24

H34

D32

A28

E24

A21

C21

W24

U2 4

R2 4

N2 4

L21

PCREQ#

NC2 (DPW R# )

EDRD Y#

C1XAVDD

C1XAVSS

C4XAVDD

C4XAVSS

CPUC LK

CPUC LK#

HTRDY#

BPRI#

BREQ0 #

HL OCK#

DEF ER#

CPUPW RG D

CPUR ST #

RS0 #

RS1 #

RS2 #

DRD Y#

BNR#

DBSY#

HIT#

HITM#

ADS#

HREQ 0#

HREQ 1#

HREQ 2#

HREQ 3#

HREQ 4#

HASTB0#

HASTB1#

HD0 #

HD1 #

HD2 #

HD3 #

HD4 #

HD5 #

HD6 #

HD7 #

HD8 #

HD9 #

HD10#

HD11#

HD12#

HD13#

HD14#

HD15#

HD16#

HD17#

HD18#

HD19#

HD20#

HD21#

HD22#

HD23#

HD24#

HD25#

HD26#

HD27#

HD28#

HD29#

HD30#

HD31#

HD32#

HD33#

HD34#

HD35#

HD36#

HD37#

HD38#

HD39#

HD40#

HD41#

HD42#

HD43#

HD44#

HD45#

HD46#

HD47#

HD48#

HD49#

HD50#

HD51#

HD52#

HD53#

HD54#

HD55#

HD56#

HD57#

HD58#

HD59#

HD60#

HD61#

HD62#

HD63#

HA3 #

HA4 #

HA5 #

HA6 #

HA7 #

HA8 #

HA9 #

HA1 0#

HA1 1#

HA1 2#

HA1 3#

HA1 4#

HA1 5#

HA1 6#

HA1 7#

HA1 8#

HA1 9#

HA2 0#

HA2 1#

HA2 2#

HA2 3#

HA2 4#

HA2 5#

HA2 6#

HA2 7#

HA2 8#

HA2 9#

HA3 0#

HA3 1#

HA3 2#

HA3 3#

HA3 4#

HA3 5#

DBI0#

DBI1#

DBI2#

DBI3#

H DSTBN0#

H DSTBN1#

H DSTBN2#

H DSTBN3#

HDST BP0 #

HDST BP1 #

HDST BP2 #

HDST BP3 #

HPCO MP

HNCO MP

HVREF

HVREF

HVREF

HVREF

HVREF

C 6 22 * . 1U _ 1 0V _ X7 R _ 04

C210

10U_10V_08

C 6 29 * . 1U _ 1 0V _ X7 R _ 04

C2 60

.01U_16V_X7R_04

C605

.1U_10V_X7R _04

C24 0

. 01 U _ 16 V _X 7R _0 4

C 6 31 * . 1U _ 1 0V _ X7 R _ 04

C273

. 0 1U _1 6V _ X 7R _ 04

L23

HCB1005KF-121T20

C6 06

.01U_16V_X7R_04

R183 10_1%_04

C 6 23 * . 1U _ 1 0V _ X7 R _ 04

L1 8 H C B 10 0 5K F - 1 21 T2 0

C59 8

*10U_10V_08

C 6 16 * . 1U _ 1 0V _ X7 R _ 04

NC2 NC_04

C 6 24 * . 1U _ 1 0V _ X7 R _ 04

R178 110_1%_06

L65 HCB1005KF-121T20

C 6 15 * . 1U _ 1 0V _ X7 R _ 04

P la c e un de r M6 71 MX

solder side

NB _G TL RE F= 0. 7V

INT ERNAL VGA( M 740S ) : R

EXT ERNAL VGA ( M760SU ) : 0 .1U

77mA

D05 10/15

Sheet 4 of 38

SiSM672 Host,

PCIE 1/5

剩余38页未读,继续阅读

资源评论

JOZECN

- 粉丝: 747

- 资源: 2516

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功