没有合适的资源?快使用搜索试试~ 我知道了~

温馨提示

试读

12页

Type7系列紧凑轻便,适用于服务器级边缘应用。最新COM.0 3.1版本增加对PCIe Gen4的支持,并为16-31通道配置第2个PCIe时钟。此外,4个10GbE基础接口更新对CEI边带信令的支持,紧跟前沿技术趋势。 Type7系列载板封装LAN物理层,终端用户可使用10GbE铜缆或光纤连接。它进一步兼容最大支持32通道的PCIe插口以及NC-SI管理接口; 由于LAN PHY位于载板上,因此最终用户可以选择10GbE铜缆或光纤解决方案。Type 7还支持最多32个PCIe通道以及NC-SI管理接口。 Type 7模块的应用范围非常广泛:通用加固级嵌入式电脑,关键任务服务器,SDN设备,信号处理和数据采集设备,网络测试设备,卫星网关,机上娱乐系统。

资源推荐

资源详情

资源评论

COM.0 Re

PICMG® COM.0

COM Express™ Type 7 Preview

Type 7 Preview – Subject to Change Page 1 of 12 Copyright © PICMG® July 25, 2016

Purpose

The information in this document provides a preview of the upcoming PICMG® COM.0 COM Express®

Type 7 pinout. The pinout will officially launch with R3.0 of the specification later in 2016. The goal of

this document is to provide COM Express module and carrier designers with information on the soon to

be released Type 7 pinout so that potential users have the necessary design information.

Note: The information provided is preliminary and subject to change.

Why Type 7?

The current revision of the COM.0 specification was released 4 years ago. The interfaces provided in

the existing specification reflect the commonly used chipset interfaces at that time. In the last year

there has been an increased interest in higher bandwidth as well as additional Ethernet interfaces. The

primary motivation for Type 7 was to add support for two or four 10GbE interfaces.

Type 7

Type 7 is focused on data center applications where high bandwidth Ethernet interfaces are required.

Ideally the pins required for the new 10G signals would come from a pool of reserved pins.

Unfortunately, the COM.0 pinouts did not have the necessary number of pins available. Since most

data center applications are headless, the COM.0 subcommittee made the decision to repurpose the

video pins for 10GbE pins. The Type 7 pinout is based on Type 6 with the following changes:

Removed LVDS, DDI, and VGA graphics interfaces. The pins now provide the 10G signals.

Removed audio support. These pins are now reserved.

Removed ExpressCard support. Some of these pins are now reserved.

Reduced the number of SATA channels from 4 to 2 to gain 2 additional PCIe lanes.

Reduced the number of USB 2.0 ports from 8 to 4 to gain 4 additional PCIe lanes. Note that all 4

USB ports support USB 3.0.

Added 8 PCIe lanes for a total of up to 32.

Added two or four 10GbE interfaces with management sideband signals.

Added NC-SI interface.

Added support for IEEE1588.

Added eSPI interface multiplexed over LPC.

COM.0 Re

PICMG® COM.0

COM Express™ Type 7 Preview

Type 7 Preview – Subject to Change Page 2 of 12 Copyright © PICMG® July 25, 2016

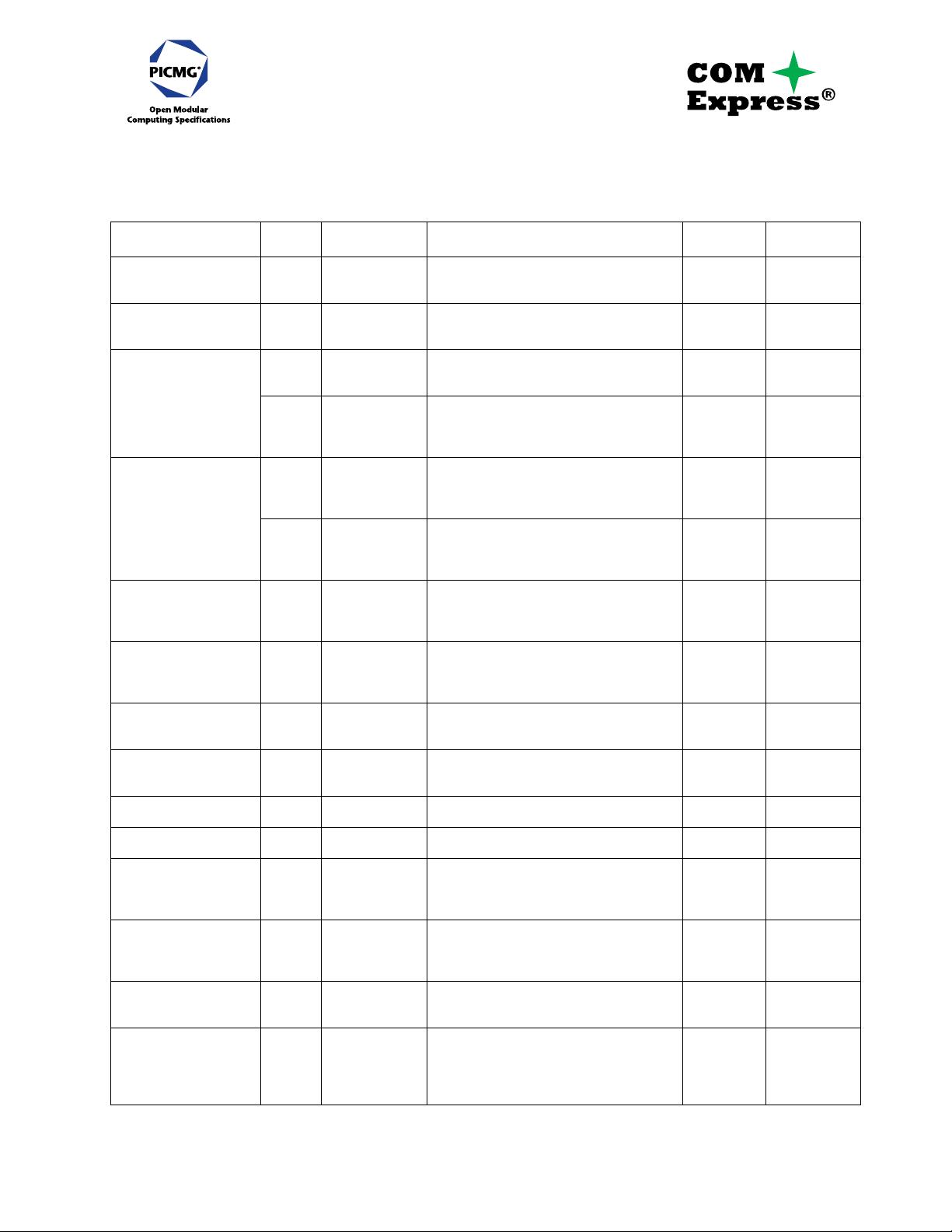

Module 10GB Ethernet

Gigabit Ethernet

Pin

Type

Pwr Rail /

Tolerance

Description

PU/PD

Pin

Availability

10G_KR_TX[0:3]+

10G_KR_TX[0:3]-

O KR

AC coupled on

Carrier

10GBASE-KR ports, Transmit Output differential

pairs

T7

10G_KR_RX[0:3]+

10G_KR_RX[0:3]-

I KR

AC coupled on

Module

10GBASE-KR ports, Receive Input differential

pairs

T7

10G_PHY_MDIO_SDA[0:3]

O

3.3V Suspend /

3.3V

MDIO Mode Management Data I/O Interface

mode data signal for serial data transfers

between the MAC and an external PHY

T7

I/O OD

3.3V Suspend /

3.3V

I

2

C Mode

I

2

C Data signal, of the 2-wire management

interface used for serial data transfers between

the MAC and an external PHY

PU 2K2

T7

10G_PHY_MDC_SCL[0:3]

O

3.3V Suspend /

3.3V

MDIO Mode

Management Data I/O Interface mode clock

signal for serial data transfers between the

MAC and an external PHY

T7

I/O OD

3.3V Suspend /

3.3V

I

2

C Mode

I

2

C Clock signal, of the 2-wire management

interface used for serial data transfers between

the MAC and an external PHY

PU 2K2

T7

10G_SFP_SDA[0:3]

I/O OD

3.3V Suspend /

3.3V

I2C data signal of the 2-wire management

interface used by the 10GbE controller to

access the management registers of an

external Optical SFP module.

PU 2K2

T7

10G_SFP_SCL[0:3]

I/O OD

3.3V Suspend /

3.3V

I2C clock signal of the 2-wire management

interface used by the 10GbE controller to

access the management registers of an

external Optical SFP module

PU 2K2

T7

10G_LED_SDA

I/O OD

3.3V Suspend /

3.3V

I2C Data,of the 2-wire interface that transfers

all LED signals and additional Strapping Signal

for I2C or MDIO mode of the Optical PHY

PU 2K2

T7

10G_LED_SCL

I/O OD

3.3V Suspend /

3.3V

I2C Clock,of the 2-wire interface that transfers

all LED signals and additional Strapping Signal

for I2C or MDIO mode of the Optical PHY

PU 2K2

T7

10G_INT[0:3]

I

3.3V Suspend /

3.3V

Interrupt pin from Copper PHY or Optical SFP

module to the 10GbE Controller

PU 2K2

T7

10G_SDP[0:3]

I/O

3.3V Suspend /

3.3V

Software-Definable Pins. Can also be used for

IEEE1588 support such as 1pps signal

T7

10G_PHY_SEL_01

I

3.3V Suspend /

3.3V

Input signal that declares if the carrier board is

equipped with a Copper or Optical PHY on port

0 and port1. Default state is MDIO mode. For

I2C mode pull down with 1K on carrier

PU 10K

T7

10G_PHY_SEL_23

I

3.3V Suspend /

3.3V

Input signal that declares if the carrier board is

equipped with a Copper or Optical PHY on port

2 and port 3. Default state is MDIO mode. For

I2C mode pull down with 1K on carrier

PU 10K

T7

10G_PHY_RST_01

O

3.3V Suspend /

3.3V

Output signal that resets an Optical PHY

on port 0 and port1 (with Copper PHY this

signal is not used)

T7

10G_PHY_RST_23

O

3.3V Suspend /

3.3V

Output signal that resets an Optical PHY

on port 2 and port 3 (with Copper PHY this

signal is not used)

T7

COM.0 Re

PICMG® COM.0

COM Express™ Type 7 Preview

Type 7 Preview – Subject to Change Page 3 of 12 Copyright © PICMG® July 25, 2016

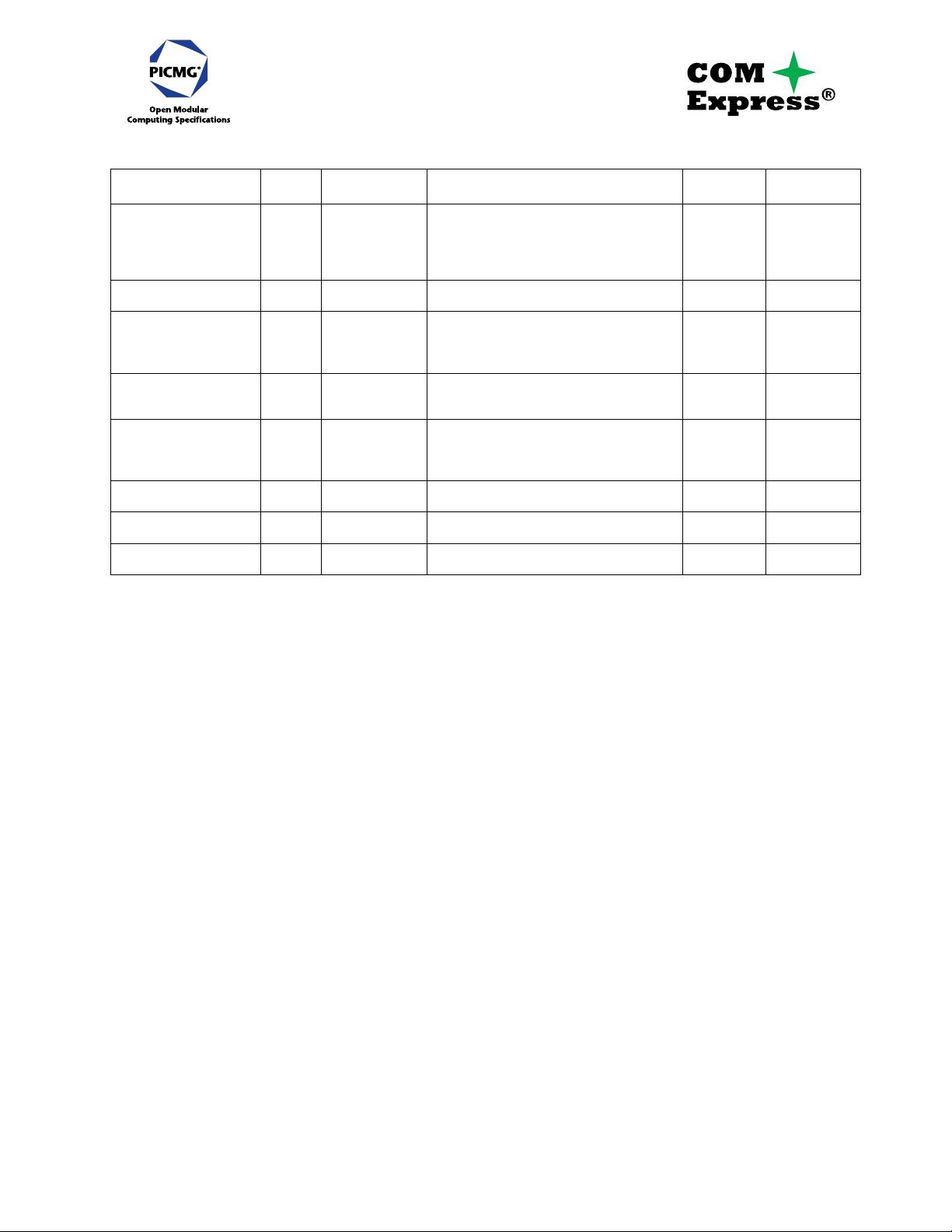

Gigabit Ethernet

Pin

Type

Pwr Rail /

Tolerance

Description

PU/PD

Pin

Availability

NCSI_CLK_IN

I

3.3V Suspend /

3.3V

Clock reference for receive, transmit, and

control interface

(PD 10K on carrier when NC-SI is not used on

carrier)

T7

NCSI_RXD[0:1]

O

3.3V Suspend /

3.3V

Receive Data (from NC to BMC)

T7

NCSI_TXD[0:1]

I

3.3V Suspend /

3.3V

Transmit Data (from BMC to NC)

(PD 10K on carrier when NC-SI is not used on

carrier)

T7

NCSI_CRS_DV

O

3.3V Suspend /

3.3V

Carrier Sense/Receive Data Valid to NC,

indicating that the transmitted data from NC to

BMC is valid

T7

NCSI_TX_EN

I

3.3V Suspend /

3.3V

Transmit enable

(PD 10K on carrier when NC-SI is not used on

carrier)

T7

NCSI_RX_ER

O

3.3V Suspend /

3.3V

Receive error

T7

NCSI_ARB_IN

I

3.3V Suspend /

3.3V

Network Controller hardware arbitration Input

T7

NCSI_ARB_OUT

O

3.3V Suspend /

3.3V

Network Controller hardware arbitration

output

T7

剩余11页未读,继续阅读

资源评论

黄小鹿

- 粉丝: 3322

- 资源: 32

上传资源 快速赚钱

我的内容管理

展开

我的内容管理

展开

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

前往需求广场,查看用户热搜

前往需求广场,查看用户热搜安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功